摘要: 针对目前移动存储设备大量的失泄密事件,提出了一种适用于移动安全存储设备的密码SoC设计方案,并在FPGA开发板上进行了验证。该SoC集成自主设计的安全协处理器,能够支持多种密码算法。介绍了NAND Flash控制器的设计方案,并在此基础上提出了高速存取技术。基于FPGA的测试结果表明,该SoC能够有效完成多种密码操作,具有较高的数据吞吐率。基于SMIC 0.18 μm工艺综合后的结果显示,工作频率能够达到100 MHz,面积约为250万门。

移动存储产品已广泛应用于各行各业,是不可或缺的信息交换载体,特别在日常办公系统中,以U盘、固态移动硬盘为代表的存储介质的使用日益普遍。而在实际应用中,移动存储设备易丢失、易损坏、易染病毒、不可控的特性也使数据安全无法得到充分保证。因遗失、暴力破解、主动泄密、木马攻击等方式导致的泄密事件也在逐渐上升[1]。

为了解决这一问题,国内外已经研制出多款相关安全产品,但是这些安全产品大多采用单一算法或固定的几种算法,其灵活性和安全性都不够高,无法满足不同设计的安全需求[2]。

针对现有安全SoC存在的问题,本文基于高性能嵌入式CPU构建并设计了一款密码SoC平台。该SoC平台采用自主设计的安全协处理器执行密码操作,经验证可适用于三类主要的密码算法[3]:对称密钥加密算法、散列算法和公开密钥加密算法。此外,设计了高性能NAND Flash控制器,支持外接多种类型的NAND Flash芯片(SLC、MLC 和TLC),最大支持容量为160 GB。本设计可应用于加密U盘、加密U盘KEY、加密移动硬盘、高速加密流转接器等设备中。

1 硬件设计

1.1 系统架构

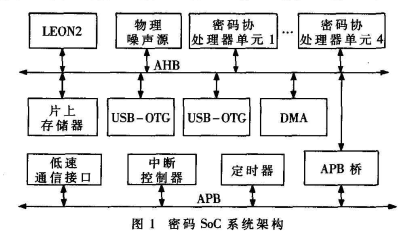

本文提出的密码SoC架构如图1所示。其中集成了两种处理器核,分别是通用处理器(LEON2)和4个安全协处理器(Security ASIP),两者通过系统总线相连。所有涉及加解密的运算都被映射到安全协处理器中执行。DMA控制器负责把将要执行的加解密任务按照CPU的配置分配到各安全处理器中,CPU只承担控制和部分数据传输任务,绝大部分的运算由安全协处理器完成,CPU在大部分时间处于挂起(suspend)状态,直到有中断将其唤醒。

片上存储器主要包括EFlash/SRAM,用于存储操作系统引导程序、用户程序等;物理噪声源主要用于产生真随机数,生成密码运算时的消息密钥;两个USB-OTG 接口可根据应用需求设置成Host、Device 或OTG,支持多达6 个端点,可设置成多重复合设备,最大限度地满足用户的设计需求;

NAND Flash控制器负责产生符合NAND Flash接口操作规范的时序信号,带有ECC校验模块,每512 B可修正位数为1 bit或8 bit,支持外接8片NAND Flash。另外还包含有低速通信接口、定时器、中断控制器、存储保护单元、功耗管理单元等辅助模块,用于完成平台的其他功能。

1.2 安全协处理器结构

分析现有的安全存储设备[4]可以发现,在使用存储设备之前,必须对使用者进行身份验证;文件读写时,必须对数据进行加解密操作;为了保证数据的完整性,必须对数据进行完整性验证操作。所以,密码SoC必须能够灵活处理对称、公钥和杂凑三类算法,这个任务主要由安全协处理器完成。在进行安全协处理器的设计之前,必须对各类密码的执行特点进行分析。由专门的工具[5]分析可以得出各种密码算法的执行特点。

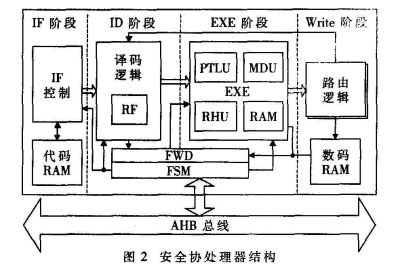

对各类密码算法的特点进行分析后,本文提出了如图2所示的安全协处理器架构。该安全协处理器基于传统的RISC处理器结构所设计,分为取指令(IF)级、译码(ID)级、执行(EXE)级/memory访存级和写回(write)级四级,能支持标准的RISC指令,并且还能执行一些专门设计的特殊指令。

在执行级,不仅有处理正常RISC标准指令的ALU单元,还有专用的硬件功能单元、PTLU(Parallel Table Look-Up)和MHU(Mul/Div unit&Hash Unit),用来对算法中比较耗时的运算(如查找表、模乘等操作)进行加速。为了加快安全协处理器的指令和数据的存取速度,在协处理器内部分别嵌入1 KB大小的指令RAM和数据RAM,用来存放协处理器的指令和数据。该协处理器指令集不仅包括标准的算术和逻辑运算指令,还包括专用的密码运算指令,如PTAES、 PTW、MOD_MUL等。

1.3 NAND Flash控制器设计

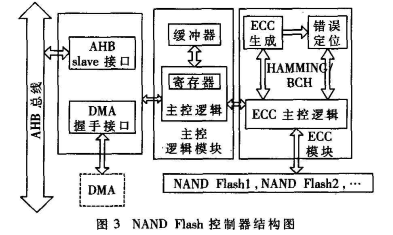

本文设计的NAND Flash控制器[7]结构如图3所示。NAND Flash控制器包含总线接口模块、DMA握手接口模块、控制状态机转换的主控逻辑模块,用以缓冲数据、收发命令和状态字的缓冲器(buffer);提供ECC校验纠错功能的ECC模块和直接控制NAND Flash存储体的接口模块。

总线接口模块负责接收CPU发送的指令,将收发数据送至相应数据寄存器和指令寄存器,并将状态寄存器内容返回给CPU核;主控逻辑模块负责整个Flash控制器的控制工作,包含指令、状态、配置、数据、页交换使能、错误地址等寄存器,是控制器的核心。

ECC模块主要负责对存入NAND Flash中的数据进行纠错编码并对从NAND Flash中读出的数据进行纠错译码的工作。DMA握手接口模块在系统DMA参与数据传输的情况下,负责DMA与NAND Flash控制器之间的硬件握手功能。相比与直接由CPU核发送命令字给NAND Flash,然后直接从I/O 口读写数据的工作方式,通过DMA方式的传输效率明显要高。

特别在连续读取大批量数据的情况下,这种工作方式的优点能更好地体现出来。在实际产品应用中(如数码照片的存取),读写数据量一般都是页大小的上千倍,所以这样的设计有助于提高产品的实用性。

该NAND Flash控制器支持外接8片NAND Flash芯片。为了提高数据的读写速度,实现对并行数据读写的支持,控制器的数据线位宽设置为16 bit,可以支持对两片数据线位宽为8 bit的NAND Flash的并行读写操作;同时,本设计对控制器的结构进行了优化,使其能够支持对多片NAND Flash芯片的流水线读写操作。为了更好地支持SLC、MLC和TLC NAND Flash器件,还设计了基于汉明码的1 bit ECC纠错模块和可纠正8 bit随机错误的BCH编/译码器,用户可以根据需要选择相应的ECC操作。

2 高速存储技术

NAND Flash器件属于低速设备。以K9WBG08U1M为例,芯片的写入时间分为加载时间和编程时间两部分,写满一页所需的命令、地址和数据的加载时间约为102.5 ?滋s,最大编程时间约为700 μs。在写入过程中,因还要进行BCH编码等操作,也会消耗一些时间,所以设计中,使用最大的编程时间进行计算,而单片Flash其写入速度最高也只有5.1 MB/s,NAND Flash的读写速度也会成为系统性能的瓶颈。为了解决这个问题,可以采用如下技术。

2.1 数据并行处理技术

因Flash的数据位宽一般为8 bit,如果按传统的操作方法对Flash进行读写,即写完一片NAND Flash之后再写下一片,其最高的存储速度只有5.1 MB/s,无法适用于高速数据传输的要求。为此,本文设计的NAND Flash控制器将I/O数据线设为16 bit,主控制可以通过配置来选择数据线的位数。

当需要对数据进行并行处理时,将两片低速Flash芯片并联起来,使用相同的控制线、片选和读写信号线,组成一个多位宽的Flash组;两片Flash并行工作时,一片存储数据的高8 bit,一片存储数据的低8 bit,这样,存储容量和存储速度都是单片Flash的2倍。

2.2 流水线技术

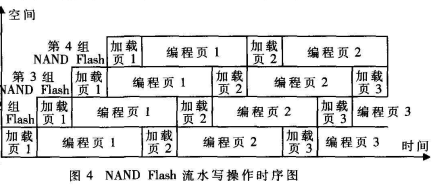

流水线技术在计算机领域得到广泛运用,它是提高硬件资源利用率和执行效率的有效手段,该技术可以有效提高存储系统的性能。本文设计的NAND Flash控制器中只有一个读数据FIFO和一个写数据FIFO,大小均为4 KB。

当对一片NAND Flash进行操作时,在命令或数据加载完成后,该片NAND Flash会处于忙状态,此时读或写数据FIFO由于处于空闲或等待状态未被使用,因此控制器可以继续对处于空闲状态的NAND Flash进行操作,如此便形成流水线操作。还可以把两片NAND Flash作为一组进行数据并行处理,共4组进行流水线操作,以达到最大的数据吞吐率。其流水写操作时序如图4所示。

3 功能验证与性能分析

本文采用两块FPGA开发板完成SoC平台的验证,FPGA型号均为Xilinx Virtex5-xc5vlx85,两者之间通过自制的电路板进行通信验证流程:首先通过JTAG接口向EFlash中下载一个boot-loader程序,用于SoC系统的启动和测试向量的下载;SoC系统的硬件驱动和安全协处理器程序通过UART接口下载到系统中;

PC端通过UART接口给出控制命令,选择NAND Flash控制器和安全协处理的工作模式;PC端通过USB接口对NAND Flash进行数据读写的测试。系统工作时钟为80 MHz,选择K9WBG08U1M作为实体NAND Flash器件对SoC进行测试。单片K9WBG08U1M的情况下,读速度可以达到19.3 MB/s,写速度可以达到9.6 MB/s;两片K9F1208UOB并行连接时,读速度可达37.5 MB/s,写速度可达18.4 MB/s。

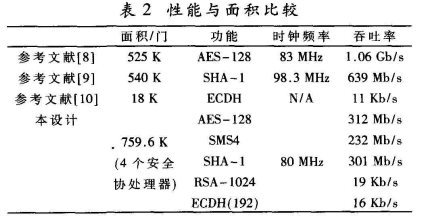

安全协处理器性能、面积与参考文献中的设计比较结果如表2所示。

经过SMIC 0.18 μm工艺库的综合,整个平台的面积约为250万门,最高工作频率为100 MHz。

本文设计的面向大安全存储的密码SoC集成了多个高性能安全协处理器,极大地提高了系统的密码处理性能。设计的NAND Flash可支持外接多种类型(如SLC、MLC和TLC)的NAND Flash芯片,并且支持多片NAND Flash的并行读写和流水线读写操作,最大支持160 GB存储容量。基于FPGA的验证表明,其能够灵活支持多种密码算法的实现,具有较高的NAND Flash访问速度。

该设计可应用于加密U盘、加密U盘KEY、加密移动硬盘、高速加密流转接器等设备中。

参考文献

[1] Chen Hanlin.The single-chip solution of embedded USB encryptor[C].Information Theory and Information Security,2010:42-45.

[2] 宁超。基于SOC存储控制器的研究与开发[D]。西安:电子科技大学,2008:50-53.

[3] Huang Wei,Han Jun,Wang Shuai.The design and implement of a mobile security SoC[C].Conference on Solid-State and Integrated Circuit Technology,2010:96-98.

[4] 胡伟,慕德俊,刘航,等。移动硬盘硬件加密的设计与实现[J]。计算机工程与应用,2010,46(22)。

[5] 沈弼龙。基于应用程序特征分析的SoC任务分配技术研究与实现[D]。长沙:国防科学技术大学,2009:31-33.

[6] AIGNER G,DIWAN A,HEINE D L,et al.An over- view of the SUIF2 compiler infrastructure[R].Computer Systems Laboratory,Stanford University,1999.

[7] 李璐,周海燕。一种含BCH编解码器的SLC/MLC NAND Flash控制器的VLSI设计[J]。现代电子技术,2009,32(7)。

[8] Wang Chenhsing,YEH J C,HUANG C T,et al.Scalable security processor design and its implementation[C].ASSCC,2005:513-516.

[9] SREEDHARAN D,AKOGLU A.A hybrid processing element based reconfigurable architecture for hashing algorithms[C].Parallel and Distributed Processing,2008:1-8.

[10] BERTONI G B,VENTURI L.ECC hardware coprocessor for 8-bit systems and power consumption considerations[C]。 ITNG,2006:573-574.

编辑:jq

-

cpu

+关注

关注

68文章

11216浏览量

222862 -

soc

+关注

关注

38文章

4514浏览量

227554 -

SMIC

+关注

关注

0文章

21浏览量

20938

发布评论请先 登录

AES加解密算法逻辑实现及其在蜂鸟E203SoC上的应用介绍

国芯科技云安全芯片CCP917T通过商用密码产品认证

为何硬件安全与软件安全在现代系统中同等重要

8款SOC方案全面支持大升降压大功率快充移动电源方案

电科网安助力第三届“熵密杯”密码安全挑战赛圆满收官

全能快充移动电源核心:深度解析IP5353高集成SOC

ESP32-P4—具备丰富IO连接、HMI和出色安全特性的高性能SoC

IP5209 2.1A充电2.4A放电集成DCP功能移动电源SOC

兆芯亮相2025商用密码展暨密码应用与创新发展大会

深度解析:SM5401S/SM5401/SM5402移动电源SOC如何优化效率与安全?

【HarmonyOS NEXT】关键资产存储开发案例

抵御量子计算威胁:航芯「抗量子密码加密签名方案」为信息安全筑起新防线

基于移动安全存储的密码SoC设计与实现

基于移动安全存储的密码SoC设计与实现

评论