作者:ToddNelson AtshushiKlwllo|o

引言

随着中国开始在人口密集的都市部署第三代(3G)无线业务,各种客观局限性驱使用户对高性能模数转换器(ADC)提出更多重要需求。高速ADC的应用多种多样,但低功耗是用户普遍要求的关键因素。要为用户的最终产品提供具有竞争性的优势,ADC需要在更低的功率和更小的尺寸基础上实现高分辨率、高速度和高性能。

3G基础设施要求

高速ADC在GSM、WCDMA和TD-SCDMA基站的接收(Rx)和发射(Tx)通路中发挥着重要作用。虽然前一代设计方案广泛使用消耗功率超过1500mW的高功率ADC,新型基站设计方案仍然需要具有高性能的低功率ADC。在城域中尤其如此,因为都市需要微基站和皮基站的密集网络来保证服务质量。除了对低功率工作这种显而易见的要求之外,小尺寸的基站在核心元器件的热耗散上还有额外限制。有限的系统散热能力经常成为实现集成密度的瓶颈。有竞争优势的系统设计方案要求ADC在紧凑和低功率基础上,实现高性能的同时还要保持低温度。

由于最终客户的要求不同,不同的制造商所选择的Rx通路架构也大相径庭。前一代接收器通常使用双ADC对从单通道解调的I和Q信号采样。因为在这

种方法中I和Q信号相对靠近基带,对双ADC的性能要求也相对较低。就下一代设计而言,趋势是通过直接在中频(IF)采样,由单个Rx通路支持多通道传输。该架构对ADC的要求更高。考虑到多个载波的频率规划情况,14位通常要求65Msps或80Msps的采样率。由于IF频率常在70MHz至140MHz之间,好的欠采样性能也是必需的。

3G基站的Tx通路中也需要高性能ADC。在Tx通路中,输出功率放大器(PA)的非线性限制了系统级性能,因此要采用不同的方法线性化PA输出。以前,PA线性化通过如前馈方法的全模拟技术实现。就下一代设计而言,发展趋势是通过采用快速反馈通路对PA输入进行数字化预失真来补偿其非线性。

例如,尽管主流WCDMA基站一般在12位时要求125Msps采样率,但PA线性化所需采样率取决于数字化载波数量以及线性化在何种频率范围内有效。为了减少RF下变频阶数,目前趋势是在更高的IF频率上采样。由于目标IF频率在100MHz至200MHz范围内已很普遍,ADC必须具有卓越的欠采样性能。

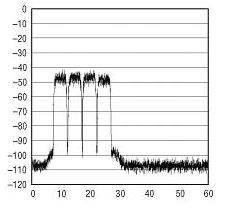

在同时数字化多个WCDMA调制载波时,该应用的一个重要衡量指标是ADC的相邻通道泄漏率(ACLR)。图1所示是一个常见方案的FFT频谱,其中4个以140MHz为中心的WCDMA载波以122.88Msps采样率和12位分辨率采样。ACLR测量结果反映该ADC在靠近每个载波边缘的频率信噪比(SNR)与其互调失真。该测量常常被视为判定某特定ADC可否用于一个给定PA线性化应用的关键测试。

图1

如何挑选一个高速ADC

高速ADC的性能特性对整个信号处理链路的设计影响巨大。系统设计师在考虑ADC对基带影响的同时,还必须考虑对射频(RF)和数字电路系统的影响。由于ADC位于模拟和数字区域之间,评价和选择的责任常常落在系统设计师身上,而系统设计师并不都是ADC专家。

除了上文提及的用户需求之外,还有一些重要因素用户在最初选择高性能ADC时常常忽视。他们可能要等到最初设计样机将要完成时才能知道所有系统级结果,而此时已不太可能再选择另外的ADC。

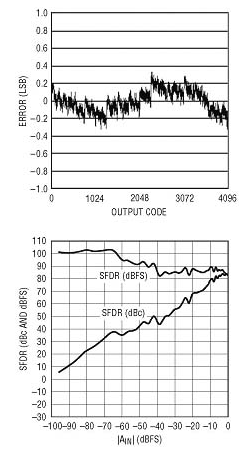

影响很多无线通信系统的重要因素之一就是低输入信号电平时的失真度。大多数无线传输到达ADC的信号电平远低于满标度输入范围。为确保多路传输信号的功率同时汇集到ADC输入时不发生压缩,信号链路的前端增益被设计成稍微低于ADC的满标度范围。然而,几乎所有高速ADC都保证其SFDR性能在输入电平从满标度的 -1dB。此外,大多数数据表都有宽输入幅度范围内典型的SFDR图。用户应该仔细观察该曲线,核实运行是否稳定和是否可预知。低输入幅度上存在任何大步进或锯齿特性都表明ADC转移函数中的系统非线性。由于转移函数线性度和低输入电平失真密切相关,对最大积分非线性(INL)有严格保证的ADC在低输入幅度上一般会有更稳定的失真性能。

选择对INL、差分非线性(DNL)、SNR和SFDR等所有关键性能规格具保证最小或最大值限制的ADC是非常重要。这些规格在应用的整个工作温度范围内应该得到保证。用户特别需要留意这些关键参数是否仅在小温度范围内或室温下才能保证。高速ADC内部的精确运算放大器和快速比较器如果设计得不够坚固,它们在温度变化时可能会发生很大的变化。选择没有宽温度范围内保证限制的ADC会给设计带来不必要的风险。

解决方案的尺寸要求也很关键,因为都市基站设计的PCB面积非常有限。由于使用QFN等小型扁平IC封装缩减小了ADC本身的面积,总体解决方案面积实际上可能大得多。仔细察看所推荐的电路会发现很多高速ADC都需要大量电容值很大的电容器(如10μF),这些电容器比ADC占用的PCB面积大得多。由于存在封装连接线寄生电感,很多高速ADC需要此类大外部电容器旁路电源和内部基准电路系统。要在最终产品中实现小体积,就要求ADC不仅采用小型封装,而且还要使这些大的外部旁路电容器尺寸和数量最小化。

技术趋势

除了新颖的电路设计技术,工艺的进步在低功率高速ADC的开发中同样重要。特别值得一提的是,由于数字技术最初的驱使,硅技术工艺不断调整,采用CMOS工艺制造的ADC也因此受益匪浅。

就模拟电路设计而言,CMOS工艺调整的关键优势在于更低的功率和更高的速度运作。与仅消耗动态功率的传统数字CMOS电路不同,ADC消耗的大部分功率都是静态电流用来偏置放大器和比较器等模拟电路引起的。对给定的模拟偏置电流,更短的通道长度(L)工艺为晶体管提供更高的跨导(gm),这是器件性能的一个关键衡量指标。更小的晶体管尺寸也使器件的寄生电容更小。在高速ADC的每一种流水线级上,精确运算放大器等关键电路的模拟稳定速度极大程度上由晶体管gm决定。因此,在给定总偏置电流情况下,缩短L会使工作速度更快。

另一个好处是,电源电压通常随着L缩短而降低,因此即使模拟偏置电流保持不变,总体功耗也会降低。通过工艺精细程度的调整,ADC设计师可以灵活地在给定功率级别上提高速度或在给定速度时降低功率。

然而,模拟电路的工艺调整存在一个严重的缺点。由于降低了电源电压,ADC的满标度输入范围也必须降低,以便为运算放大器等模拟电路系统提供足够的电压空间。更小的输入范围导致更低的信号功率,SNR会随着工艺调整而下降。低功率、高性能设计方案的挑战还在于降低ADC产生的噪声,以保持足够的信噪比。

凌特公司低功率高性能ADC介绍

很明显,低功率、高性能是市场上用户的主要要求。为满足市场需求,凌特公司新近推出了几个高速ADC系列。

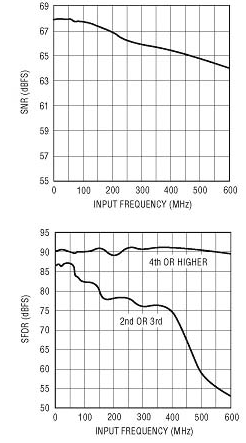

LTC2224/2222/2223是引脚兼容的3.3V 12位135/105/80Msps ADC,并为欠采样而优化。LTC2224系列在输入频率高达140MHz时具有超过67.5dB的SNR和80dB的SFDR,而在135Msps时仅消耗630mW功率。该高度优化的跟踪与保持设计对高达400MHz的输入频率持续保持超过65dB的SNR和75dB的SFDR,在低功率时具有极佳的欠采样性能。图2概括了LTC2224的高频性能。即使是那些消耗功率高得多的器件也极少在高输入频率时具有如此的欠采样性能。如图3所示,就12位ADC而言,该ADC转移函数的线性度也很高,可与很多14位器件媲美。如同干净的转移函数预料,小输入幅度时的失真性能也相当稳定。LTC2224系列非常适合要求低功率和卓越欠采样性能的WCDMA PA线性化应用。

图2

图3

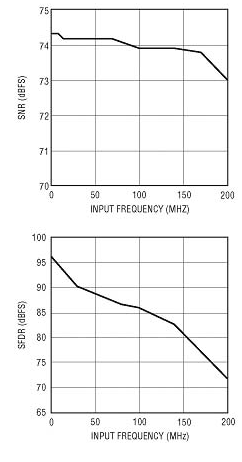

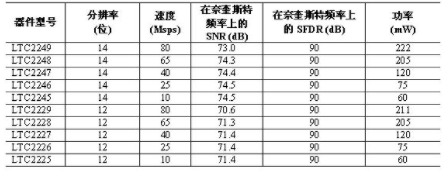

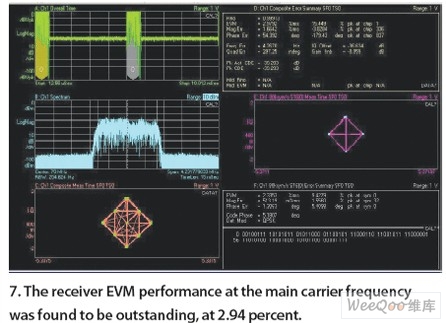

LTC2249/LTC2229系列是引脚兼容的3V 14位/12位ADC,具有高达80Msps的速度。表1概括了这些器件的性能特性。这些高速ADC功率极低,范围从LTC2249/LTC2229在80Msps时的222mW至LTC2245/LTC2225在10Msps时的60mW。实现这些低功率并未损失性能。例如,如图4所示,LTC2248(65Msps)对远离奈奎斯特频率(Nyquist Frequency)的输入保持为74dB SNR和80dB SFDR。通过使用5mm×5mm纤巧型QFN封装,这两个系列还实现了小体积。大部分必需的旁路电容都直接集成在芯片上,因此这些器件仅需要少量低值外部旁路陶瓷电容器,就能达到数据表所显示的性能。引脚兼容的LTC2249和LTC2229系列具有高性能,低功耗,小体积的特点。使它们非常适合用于小型WCDMA、GSM和TD-SCDMA等基站。

图4

表1

结论

都市基站设计方案在高输入频率和宽输入带宽时要求良好的SNR和SFDR性能。这样就需要有高线性度的跟踪与保持设计以及小内部采样时钟抖动;每一方面在ADC中都需要消耗功率。很多低功率ADC的SNR和SFDR都随着输入频率的提高而迅速下降,因为内部时钟抖动和跟踪与保持电路的非线性主要影响了响应。但是,最近推出的低功率和小尺寸的高性能ADC克服了这些问题,满足了新一代无线通信市场对尺寸更小、功率效率更高产品的需求。

责任编辑:gt

-

放大器

+关注

关注

146文章

14296浏览量

220960 -

adc

+关注

关注

100文章

7379浏览量

553672 -

基站

+关注

关注

17文章

1438浏览量

68339

发布评论请先 登录

基于高性能ADC的都市基站设计方案

基于高性能ADC的都市基站设计方案

评论