大家晚上好,今天给大家分享一个篇关于状态机的学习。为啥突然会写这个话题,因为今天要看文章和视频学习的时候,突然看到了“状态机”三个字,也突然让我想起了,在刚入职一家公司的时候,看产品的源代码画出整个软件框架流程图来,现在我还清晰的记得当时公司产品里面就有用到这个状态机的用法,但是当时我刚接触到这个东西,看了老半天那个源码吗,没看懂,因为那时候第一次看那么大的工程量代码,说实话脑袋有点晕晕的,不是很习惯。所以今天的文章只是带大家入门和了解一下状态机,等你真正在工作当中有遇到这个状态机作为开发需要的话,你再去深入研究。

一、什么是状态机?

1、有限状态机:

常说的状态机是有限状态机FSM(Finite State Machine)。FSM指的是有有限个状态(一般是一个状态变量的值),这个机器同时能够从外部接收信号和信息输入,机器在接收到外部输入的信号后会综合考虑当前自己的状态和用户输入的信息,然后机器做出动作:跳转到另一个状态。

举个实际生活例子来理解一下,比如我们平时烧开水喝,在你没烧之前,水的状态是液态的,但是当你把外界温度一升高,水达到它的沸点之后,就会形成水蒸气;当你把外界温度降下来,水蒸气就有会变成液态的水了。这里是外界条件是温度,温度的变化会引起水的状态的变化。这个例子可以和我们的状态机来做一个简单的思想对比。

2、考虑状态机的关键点:

从刚才的定义来看,我们只要抓住状态机的关键点来理解就行:

1、外部输入

2、当前状态

3、下一个状态

二、两种状态机类型:

(1)Moore型状态机特点是:输出只与当前状态有关(与输入信号无关)。相对简单,考虑状态机的下一个状态时只需要考虑它的当前状态就行了。

(2)Mealy型状态机的特点是:输出不只和当前状态有关,还与输入信号有关。状态机接收到一个输入信号需要跳转到下一个状态时,状态机综合考虑2个条件(当前状态、输入值)后才决定跳转到哪个状态。

三、状态机的常见用途:

(1)电路设计中广泛使用了状态机思想。

(2)FPGA程序设计。

(3)软件设计(框架类型的设计,譬如操作系统的GUI系统、消息机制)。

四、状态机解决了什么问题:

(1)我们平时写程序都是顺序执行的,这种程序有个特点:程序的大体执行流程是既定的,程序的执行是遵照一定的大的方向有迹可寻的。

(2)但是偶尔会碰到这样的程序:外部不一定会按照既定流程来给程序输入信息,而程序还需要完全能够接收并响应外部的这些输入信号,还要能做出符合逻辑的输出。

五、实战例子:

开锁状态机。功能描述:用户连续输入正确的密码则会开锁,如果密码输入过程错误则锁会退回到初始状态重新计入密码,即:用户只需要连续输入出正确的密码即可开锁(输入错误不用撤销、也不用删除)。

#include <stdio.h>

// 给状态机定义状态集

typedef enum

{

STATE1,

STATE2,

STATE3,

STATE4,

STATE5,

STATE6,

STATE7,

}STATE;

int main(void)

{

int num = 0;

// current_state记录状态机的当前状态,初始为STATE1,用户每输入一个正确的

// 密码STATE就走一步,一直到STATE为STATE7后锁就开了;其中只要有一次用户

// 输入对不上就回到STATE1.

STATE current_state = STATE1; // 状态机初始状态为STATE1

// 第一步:实现一个用户循环输入密码的循环

printf("请输入密码,密码正确开锁.");

while (1)

{

scanf("%d", &num);

printf("num = %d.", num);

// 在这里处理用户的本次输入

switch (current_state)

{

case STATE1:

if (num == 1)

{

current_state = STATE2; // 用户输入对了一步,STATE走一步

}

else

{

current_state = STATE1;

}

break;

-

状态机

+关注

关注

2文章

497浏览量

28849 -

fsm

+关注

关注

0文章

36浏览量

13075

发布评论请先 登录

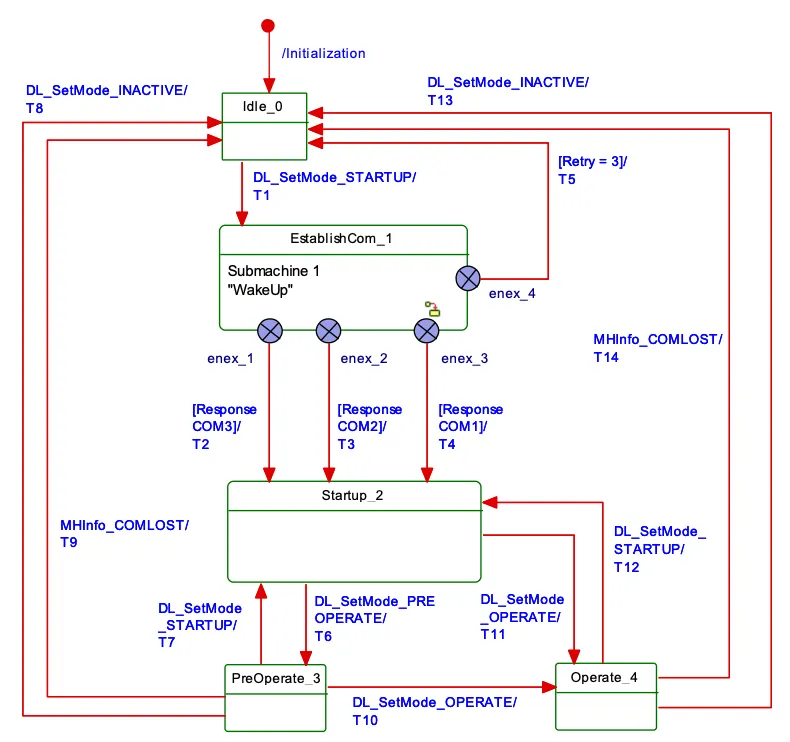

睿远研究院丨IO-Link规范解读(十一):ISDU状态机与EVENT事件

什么是状态机?

嵌入式开发为何经常用到状态机架构

睿远研究院丨IO-Link规范解读(八):M-Sequence Type 与消息处理状态机

睿远研究院丨IO-Link规范解读(六):主从站状态机解析

JTAG标准的状态机实现

简单的状态机入门知识详解

简单的状态机入门知识详解

评论