FPGA 要取代 ASIC 了,这是 FPGA 厂商喊了十多年的口号。可是,FPGA 地盘占了不少,ASIC 也依旧玩得愉快。这两位仁兄到底有啥不一样呢?

一、介绍

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,是在 PAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC) 领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。它是当今数字系统设计的主要硬件平台,其主要特点就是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。在修改和升级时,不需额外地改变 PCB 电路板,只是在计算机上修改和更新程序,使硬件设计工作成为软件开发工作,缩短了系统设计的周期,提高了实现的灵活性并降低了成本。

ASIC(Application Specific Integrated Circuit),即专用集成电路,是一种为专门目的而设计的集成电路。是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。ASIC 的特点是面向特定用户的需求, ASIC 分为全定制和半定制。亮点在于专用,量身定制所以执行速度较快。一句话总结就是,市场上买不到的芯片。水果的 A 系列处理器就是典型的 ASIC。

二、FPGA 是可复用的

FPGA 采用了逻辑单元阵列 LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块 CLB、输出输入模块 IOB 和内部连线三个部分。现场可编程门阵列(FPGA)是可编程器件。FPGA 利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个 D 触发器的输入端,触发器再来驱动其他逻辑电路或驱动 I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到 I/O 模块。FPGA 的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与 I/O 间的联接方式,并最终决定了 FPGA 所能实现的功能。

FPGA 的特点:

加电时,FPGA 芯片将 EPROM 中数据读入片内编程 RAM 中,配置完成后,FPGA 进入工作状态。掉电后,FPGA 恢复成白片,内部逻辑关系消失,因此,FPGA 能够反复使用。理论上,FPGA 允许无限次的编程。

FPGA 的编程无须专用的 FPGA 编程器,只须用通用的 EPROM、PROM 编程器即可。

FPGA 内部有丰富的触发器和 I/O 引脚。

快速成品,可以被修改来改正程序中的错误和更便宜的造价。

用户不需要介入芯片的布局布线和工艺问题,而且可以随时改变其逻辑功能,使用灵活。

(FPGA 基本架构)

三、ASIC 是为 VIP 服务的

ASIC 是定制的,具体分为全定制和半定制。

全定制设计可以实现最小面积,最佳布线布局、最优功耗速度,得到最好的电特性。特点:精工细作,设计要求高、周期长,设计成本昂贵。

半定制设计方法又分成基于标准单元的设计方法 CBIC 和基于门阵列的设计方法。半定制主要适合于开发周期短,低开发成本、投资、风险小的小批量数字电路设计。

ASIC 的特点是:

面向特定用户的需求,ASIC 在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC 需要较长的开发周期,风险较大,一旦有问题,成片全部作废,所以小公司已经玩不起了。

(ASIC 基本架构)

四、两者的设计流程

完整的 FPGA 设计流程包括功能描述、电路设计与输入、功能仿真、综合优化、综合后仿真、实现与布局布线、时序仿真、板级仿真与验证、调试与加载配置。

ASIC 的设计流程(数字芯片)包括:功能描述、模块划分、模块编码输入、模块级仿真验证、系统集成和系统仿真验证、综合、STA(静态时序分析)、形式验证。

(FPGA 和 ASIC 设计流程)

插一句,在 ASIC 设计过程中,往往要用到 FPGA 进行原型验证。FPGA 验证是进行 ASIC 设计的重要环节,其后,还需要引入 ASIC 版本源码,插入 IO PAD,DFT,功耗估计和进行其它后端流程。完成 FPGA 验证可以说就完成了 ASIC 整套流程的 50~80%。

从设计成本来考虑,小批量上 FPGA 占优,大批量时,ASIC 占优。

FPGA 本身就是一个芯片,只是你可以通过编程的方式修改内部逻辑连接和配置实现自己想要的功能。实现 ASIC,就如从一张白纸开始,你得有代码,之后综合,之后布局,布线,得到 GDSII 后去流片。

五、比速度

相同的工艺和设计,在 FPGA 上的速度应该比 ASIC 跑得慢。因为 FPGA 内部是基于通用的结构,也就是 LUT(look up table),它可以实现加法器,组合逻辑等等,而 ASIC,一般加法器就是加法器,而比较器就是比较器,FPGA 结构上的通用性必然导致冗余;另外,作为 FPGA 基本单元是 LUT(LUT 组成 SLICE,SLICE 组成 CLB--这是 xilinx 的结构),为此大的设计假如一个 LUT 实现不了,就得用两个 LUT,一个 SLICE 实现不了就要用 CLB,不同结构处于特定的位置,信号之间的互联,导致的 wire delay 是不可忽略的一部分。而对于 ASIC 来说没有结构上的限制,而且对于特定的实际可以在空间上靠得很近,相对之下 wire delay 和 cell delay 都应该比 FPGA 小。当然 LUT 中也有 DFF,作为高速的设计一般都会在一个简单的组合逻辑操作之后打一拍,再做下一步的处理。

六、比个头

完全相同的结构的话,FPGA 被 ASIC 远远踢飞。FPGA 要规模大得多才能实现 ASIC 相同的功能,主频还只有几分之一。因此,FPGA 相对于 ASIC 来说还是大很多的。

七、功耗方面

在相同工艺条件下,FPGA 要大于 ASIC。FPGA,尤其是基于占用大量硅面积的、每个单元六个晶体管的静态存储器(SRAM)的查寻表(LUT)和配置元件技术的 FPGA,其功耗要比对等的 ASIC 大得多。

八、比花的银子

FPGA 贵在单片,开发工具和风险基本不存在。对于 ASIC 贵在流片的费用和开发工具,NRE 费用随着工艺的提高变相当贵,除非你的芯片一次成功可以量产,否则单片费用将其贵无比!

九、其他方面

ASIC 用于大型项目,而对于需要快速投放市场且支持远程升级的小型项目,FPGA 则更为适合。FPGA 技术的主要优势仍是产品投放市场的时间较短。

在 ASIC 的优势方面,ASIC 加电后可立即运行,就单位逻辑大小而言封装选择更多,还可包括某些模拟逻辑。与此相对比,FPGA 加载配置进入存储器需要时间,因此不能立即工作。此外,FPGA 的封装也较复杂。

除此之外,FPGA 内部还包括接口 I/O,I/O 分为普通 I/O 和高速 I/O,高速 I/O 支持例如高速的 SERDES,用于实现 XAUI,PCIE 等高速接口,这些接口动辄几 Gbps 到 10Gbps 以上。此外种类多种多样的硬核 IP 也是各 FPGA 厂商差异化竞争利器,例如 POWERPC、ARM 等硬核 IP。从而构成 CPU+FPGA 于一体的集可编程性和可重构的处理平台。因此,相对来说,FPGA 虽然发展有二三十年的历史,其基本架构一直不变不大。

十、两者的定位

FPGA 和 ASIC 产品的使用要根据产品的定位和设计需要来选用,ASIC 产品适用于设计规模特别大,如 CPU、DSP 或多层交换芯片等,或者是应用于技术非常成熟且利润率非常低的产品,如家用电器和其它消费类电器,亦或是大量应用的通用器件如 RAM、PHY 等。而 FPGA 产品适用于设计规模适中,产品要求快速占领市场,或产品需要灵活变动的特性设计等方面的产品,如 PDH、2.5G 以下 SDH 设备和大部分的接口转换芯片等。当然具体使用那种产品来设计还要设计者充分考虑自己的产品定位来决定。

十一、两者在互相融合

最明显的莫过于处理器中开始集成 FPGA,而可编程的 ASIC 也开始兴起。随着 SoC 成为主流,两者的边界也就不辣么明显了。

十二、最后奉上网友对 FPGA 比 ASIC 快的解释

FPGA 的 LUT 等资源已经固定了,你用不用都在那里,不多不少。

ASIC 理论上每一个你用到的 CELL 或者 IP 等资源你都可以手动的摆放来进行优化。

FPGA 的资源固定有两个劣势:

劣势一:能够利用的资源是固定的,且不成大片,横跨区域的产生逻辑,会退化时序。其实也就是你没有办法把逻辑尽可能的摆得近。逻辑摆得近可以减小线上的延迟,可以提高速度。ASIC 的 cell 你可以全部的挤在一起(不违反 DRC 的前提下)。

劣势二:你的大小是固定的。你用 1 个门还是用 10W 个门,都是这一片已经固定好了的 LUT 给你用。如果你的逻辑很小很小,FPGA 很大,你信号从 IO 进来到逻辑,有可能会走比较长的距离,这个也要花时间的。极端的例子,你从上部的 IO 进来,你的逻辑在下部,这走线的长度感人啊。(正常的设计不会这么做的)

除此之外,FPGA 的走线,你几乎是动不了的。

ASIC 中你可以直接加宽金属线,比如两倍宽度走时钟线,复位线啦,之类的。金属线宽度变大,线上的延迟变小,对速度也是有帮助的。

还有 asic 的库一般还包含高性能 cell,低功耗 cell 等。在关键路径,为了提高时序,你全用高性能的 cell(功耗大)。一般的路径,时序比较松,多用低功耗的 cell(性能低)。你 FPGA 一旦选定了,你就只有他给你的东西,你没有选的。

ASIC 还可以使用 useful skew 的方式来提高速度,手段会比 FPGA 中的多。

总的来说,就如同 GPU 和 CPU 一样。GPU 可以非常快的处理图像,但是让 GPU 去处理其他的东西,GPU 表示摊手。CPU 很多的运算都能处理,也能去处理图像,只是慢而已。一旦你是冲着某个目的去的(ASIC)你为了实现这个目标,你各种没节操没下线都可以。如果你想要多方面兼顾(FPGA),你就不可能在每一个方面都做到最好,你必须 trade-off。

审核编辑 黄昊宇

-

FPGA

+关注

关注

1655文章

22286浏览量

630298 -

asic

+关注

关注

34文章

1269浏览量

124057

发布评论请先 登录

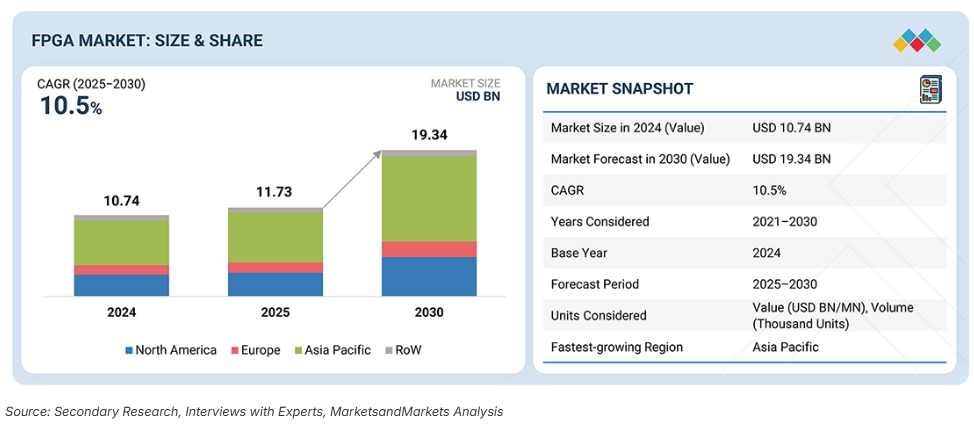

MarketsandMarkets FPGA行业报告,2026~2030 FPGA市场洞察

FPGA技术为什么越来越牛,这是有原因的

何时选择光纤电缆:场景与选择指南

AI芯片,需要ASIC

CPO光模块能取代传统光模块吗?

FPGA芯片的概念和结构

FPGA+AI王炸组合如何重塑未来世界:看看DeepSeek东方神秘力量如何预测......

DLPC410如何对SPI闪存进行编程?

JESD204B有专用于ADC/DAC和FPGA或ASIC的接口吗?

CPLD 与 ASIC 的比较

ASIC和GPU的原理和优势

大多数FPGA的程序存储器(FLASH)为什么都放在外面呢?FPGA的主要应用

FPGA VS ASIC,究竟何时能取代后者

FPGA VS ASIC,究竟何时能取代后者

评论