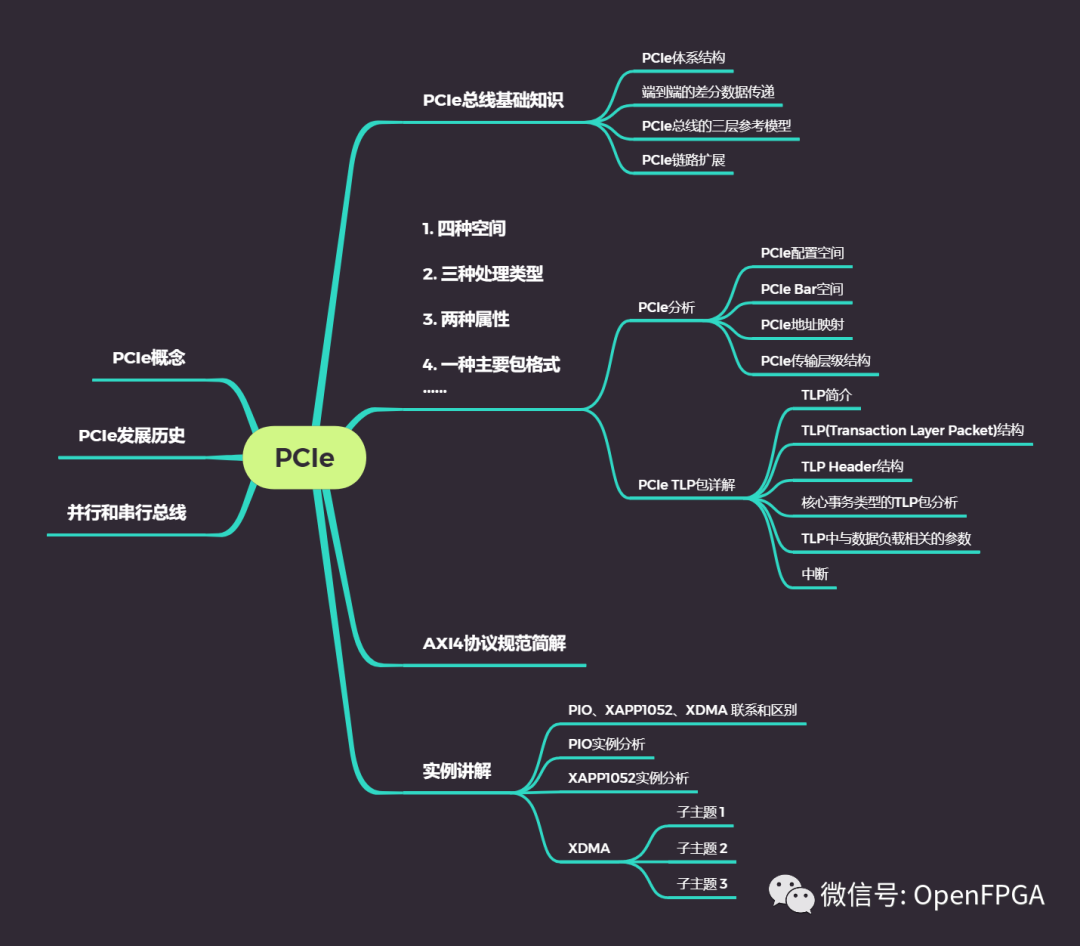

本来是在写PCIe,怎么突然又出现AXI了?不要急,先看下PCIe涉及到的知识点(初版):

其中AXI协议也是PCIe知识体量中的一部分,所以先花一部分篇幅把AXI知识总结一下,具体如下。

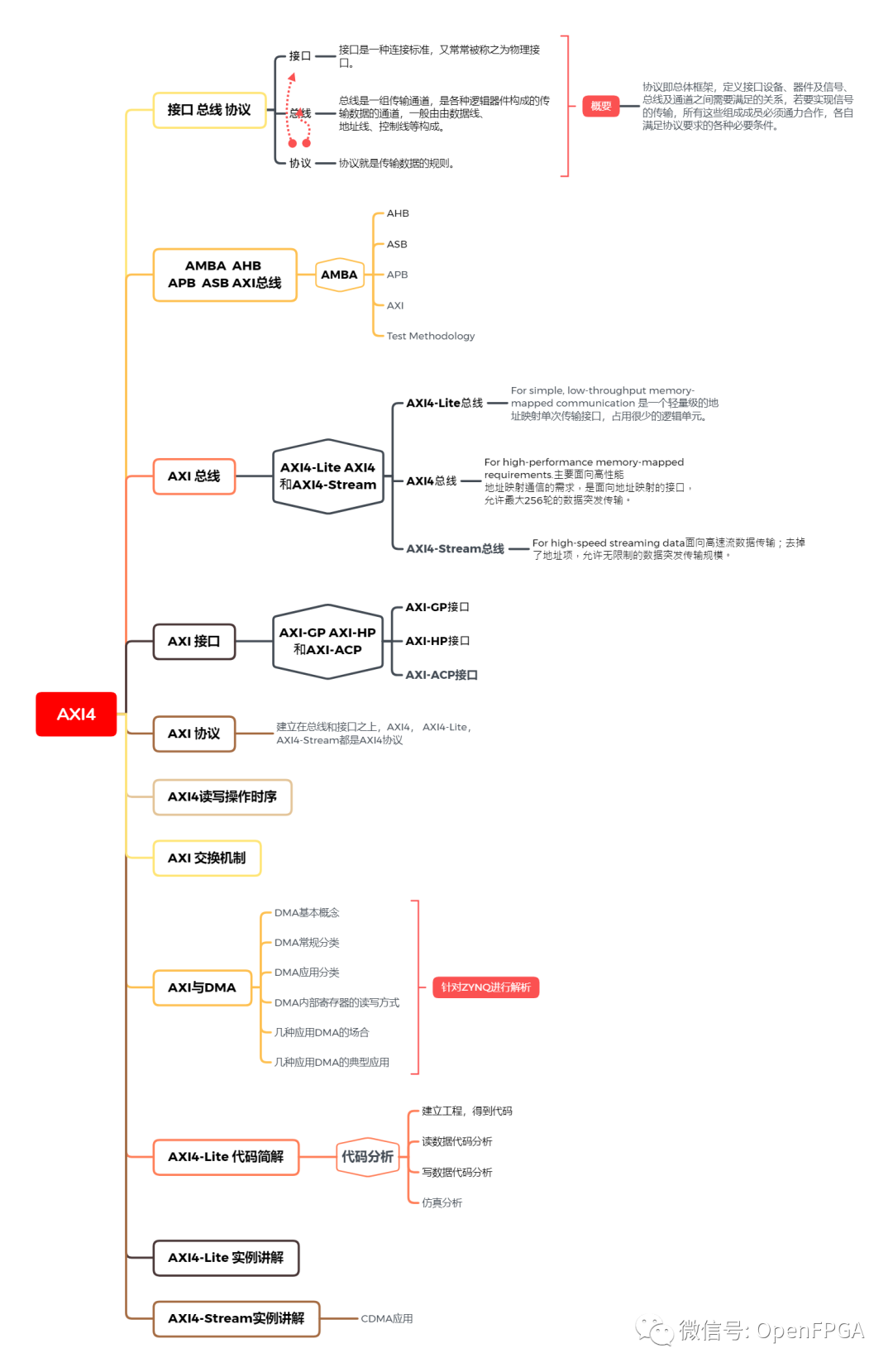

整个AXI非常复杂,涉及到的知识点也非常多,通过上面的图谱也能清晰地看出。 其中,AXI也是ZYNQ系统中比较重要的一部分。

·AMBA总线,熟悉ARM架构的朋友应该都大致了解, AMBA是ARM公司的注册商标。是一种用于片上系统(SoC)设计中功能块的连接和管理的开放标准片上互连规范。它促进了具有总线结构及多控制器或组件的多核处理器设计开发。自成立以来,AMBA已广为应用,远远超出了微控制器设备领域。如今,AMBA已广泛用于各种ASIC和SoC部件,包括在现代便携式移动设备中使用的应用处理器。

·高级可扩展接口AXI(AdvancedeXtensible Interface):是ARM公司AMBA 3.0 和AMBA 4.0规范的一部分,是并行高性能,同步,高频,多主机,多从机通讯接口,主要设计用于片上通讯。为啥说AXI是AMBA的一部分,看看下面两个图就可以比较清晰的了解。

-

总线

+关注

关注

10文章

3014浏览量

91307 -

PCIe

+关注

关注

16文章

1422浏览量

87551 -

AXI

+关注

关注

1文章

143浏览量

17791

原文标题:AXI总线详解

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

NVMe高速传输之摆脱XDMA设计14: PCIe应答模块设计

NVMe高速传输之摆脱XDMA设计20: PCIe应答模块设计

使用xilinx的axi pcie如何清除中断标志位?

充电宝又出现着火事故

如何使用AXI配置的ILA调试PCIe AXI接口?

PCIE项目中AXI4 IP核例化详解

如何使用AXI-PCIe桥接IP与我的逻辑进行通信

XPS中用“axi-pcie 1.08a”和其他一些露水创建项目不起作用的原因?

axi_pcie3_0编译的解决办法?

AXI 总线和引脚的介绍

PCIE通信技术:通过AXI-Lite ip配置的VDMA使用

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

本来是在写PCIe,怎么突然又出现AXI了?

本来是在写PCIe,怎么突然又出现AXI了?

评论