何谓 I2C?

在本文中,您将了解有关内部集成电路总线(I2C 或 IIC)的基础知识以及将此协议总线应用于短距离通信的方法。 I2C 属于串行通信协议,供双线接口用于连接 EEPROM、传感器、RTC、ADC/DAC 等低速器件以及嵌入式系统中的其它兼容 I/O 接口。

I2C 简介

I2C 包含 2 条线路:1 条为 SCL(串行时钟),另 1 条为 SDA(串行数据)。这 2 条线路都必须通过电阻上拉到 Vcc。借助使用 I2C 多路复用器可访问各条通道以连接外设,还可通过电平移位器来转换这 2 条 I2C 线路/信号上的电压电平。

注:SCL 为时钟信号,SDA 为数据信号。

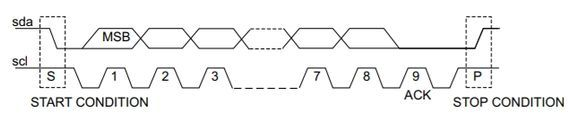

I2C 的数据传输格式如下所述。

单次数据传输包含 9 个时钟脉冲,用于驱动 8 位数据和 1 位 ACK/NACK。

数据传输帧包含 1 个 START 和 1 个 STOP 条件。

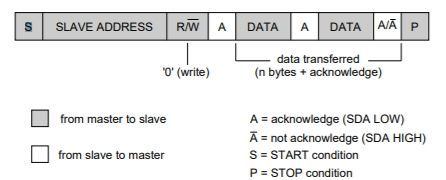

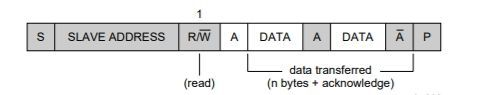

地址类型传输的启动顺序为:1 个 START 条件,后接 1 个 7 位/10 位地址、1 个 1 位 R/~W 和 1 个 1 位 ACK/NACK。随后,数据类型传输包含 8 位数据和 1 位 ACK/NACK。

I2C 总线条件

启动 (Start) 条件 - 在 SDA 上执行从高到低转换时,SCL 线路应处于高位。

停止 (Stop) 条件 - 在 SDA 上执行从低到高转换时,SCL 线路应处于高位。

数据有效性 - 当 SCL 处于高位状态时,SDA 线路上的数据有效。

数据变更 - 当 SCL 处于低位状态时,在 SDA 线路上发生数据变更。

总线繁忙 - 处于 START 与 STOP 条件之间时,总线处于繁忙状态。

ACK - 在 SCL 的第 9 次时钟脉冲时,SDA 应处于低位

NACK - 在 SCL 处于第 9 次时钟脉冲时,SDA 应处于高位

1 主器件写 (Master Write) 传输 Master Write 操作从 START 条件开始,后接 7 位/10 位从器件地址和 1 位写操作(等于 0)。成功的从器件寻址应由从器件应答 (ACK)。之后,主器件启动到从器件的数据写入,从器件将在响应中提供 N-1 字节的 ACK。当 N-1 字节完成传输后,主器件会在第 N 字节传输上发送 Not Acknowledged (NACK) 以生成 STOP 条件。 主器件执行的从器件寻址操作失败将导致总线上出现 NACK,故而将不启动数据传输,并生成 STOP 条件。

2 主器件读 (Master Read) 传输 Master Read 操作从 START 条件开始,后接 7 位/10 位从器件地址和 1 位读操作(等于 1)。成功的从器件寻址应由从器件应答 (ACK)。后续,从器件会向主器件发送数据,主器件将在响应中提供 N-1 字节的 ACK。当主器件收到 N-1 字节后,它会在第 N 字节传输上发送 NACK 以生成 STOP 条件。 主器件执行的从器件寻址操作失败将导致总线上出现 NACK,故而将不启动数据读取,并生成 STOP 条件。

3 时钟拉伸 (Clock Stretching)

SCL 由处于活动状态的总线主器件生成。从器件有时可强制时钟处于低位以延迟主器件发送更多数据(或者在主器件尝试切断从器件时钟前,从器件需要更多时间来准备数据)。这称为时钟拉伸或时钟降频。欲知详情,请参阅https://learn.sparkfun.com/tutorials/i2c/all 的协议页面

4 动态编程序列 使用如下示例中所示伪操作步骤并将其与您所看到的行为进行比较可便于您理解赛灵思 AXI IIC 仿真中的协议行为。 请保留以下步骤的副本,以便您后续在自己的设计中对其进行编辑,如省略或追加步骤。 或者,只需填入适用于的测试案例的任意内容即可。

5 初始化

1. 将 RX_FIFO 深度设置为最大值:设置 RX_FIFO_PIRQ = 0x _ _

2. 将 TX_FIFO 复位为 0x_ _

3. 启用 AXI IIC、移除 TX_FIFO 复位,并禁用通用调用

6 从 IIC 器件地址0x_ _读字节数据 1. 读取状态 (Status) 寄存器以检查确认所有 FIFO 均为空,并且总线未处于繁忙状态

2. 将 0x___ 写入 TX_FIFO(设置启动位,器件地址设置为 0x__,读权限)

3. 将 0x___ 写入 TX_FIFO(设置停止位,4 字节,将由 AXI IIC 接收)

4. 等待至 RX_FIFO 不为空为止。 a) 读取 RX_FIFO 字节。 b) 如果读取的是最后一个字节,则退出;否则,只要 RX_FIFO 不为空,则继续检查。

7 对IIC 从器件地址0x_ _写byte数据 将数据置于从器件地址 0x__: 1. 读取 SR 以检查确认所有 FIFO 均为空,并且总线未处于繁忙状态

2. 将 0x___ 写入 TX_FIFO(设置启动位,器件地址,写权限)

3. 将 0x__ 写入 TX_FIFO(数据的从地址)

4. 将 0x__ 写入 TX_FIFO(字节 1)

5. 将 0x__ 写入 TX_FIFO(字节 2)

6. 将 0x__ 写入 TX_FIFO(停止位,字节 x)

8 从 IIC 器件地址0x_ _读字节数据 数据位于从地址 0x _ _。 首先,需要写权限才能设置从器件地址,然后读权限之后执行重复启动。 1. 读取状态 (Status) 寄存器以检查确认所有 FIFO 均为空,并且总线未处于繁忙状态。

2. 将 0x_ _ _ 写入 TX_FIFO(设置启动位,器件地址设置为 0x__,写权限)。

3. 将 0x__ 写入 TX_FIFO(数据的从地址)。

4. 将 0x___ 写入 TX_FIFO(设置重复启动的启动位,器件地址设置为 0x_ _,读权限)。

5. 将 0x___ 写入 TX_FIFO(设置停止位,4 字节,将由 AXI IIC 接收)。

6. 等待至 RX_FIFO 不为空为止。 a) 读取 RX_FIFO 字节。 b) 如果读取的是最后一个字节,则退出;否则,只要 RX_FIFO 不为空,则继续检查。

AXI IIC 仿真

本文随附了一个在 Vivado 2018.1 工程中经过修改的仿真测试平台。 请将所提供的测试平台与 AXI IIC IP 配合使用。它已经过测试,可在 Vivado 环境中正常运行。 以下是根据 AXI IIC 产品指南(PG090)所提供的部分编程序列建议的示例。 以下提供了有关示例案例的说明:测试 1 - 建议的序列将数据置于从器件地址 0x6C(含 1 个数据字节)。 1. 读取 SR 以检查确认所有 FIFO 均为空,并且总线未处于繁忙状态。 2. 将 0x1D8 写入 TX_FIFO(设置启动位,器件地址,写权限)。

3. 将 0x212 写入 TX_FIFO(停止位,最后一个字节)

测试 2 - 建议的序列将数据置于从器件地址 0x6C(含 2 个数据字节)。 1. 读取 SR 以检查确认所有 FIFO 均为空,并且总线未处于繁忙状态。

2. 将 0x1D8 写入 TX_FIFO(设置启动位,器件地址,写权限)。

3. 将 0x011 写入 TX_FIFO(字节 1)。

4. 将 0x012 写入 TX_FIFO(字节 2)。

5. 将 0x2EF 写入 TX_FIFO(停止位,最后一个字节)

测试 3 - 建议的序列将数据置于从器件地址 0x6C(含 2 个数据字节)。使用错误的从器件地址重新启动。 1. 读取 SR 检查总线未处于繁忙状态并且确认所有 FIFO 均为空。

2. 将 0x1D8 写入 TX_FIFO(设置启动位,器件地址,写权限)。

3. 将 0x011 写入 TX_FIFO(字节 1)。

4. 将 0x012 写入 TX_FIFO(字节 2)。

5. 将 0x2EF 写入 TX_FIFO(停止位,最后一个字节)

6. 将 TX FIFO 复位

7. 将错误的地址 0x108 写入 TX_FIFO(设置启动位,器件地址,写权限)。

测试 4 - 不建议 将数据置于从器件地址 0x6C(含 1 个数据字节以及 START 位和 STOP 位): 1. 读取 SR 以检查总线未处于繁忙状态并确认所有 FIFO 均为空。

2. 将 0x3D8 写入 TX_FIFO(设置启动位,停止位,器件地址,写权限)。 由于该字节为停止位,故将被视为最后一个字节。 对其将不会生成 TX FIFO 空中断传输,因此它将产生总线不繁忙中断。 根据 IIC 协议,我们不建议在任一字节中同时包含启动位和停止位。 请参阅如下有关此行为的示例:

建议遵循测试案例 1、2 和 3 进行操作,但不建议使用测试案例 4。 这也将有助于您遵循编程序列来进行操作。 注释: 1) 请留意 ISR interrupt(4) 而不是 interrupt(2),以检测最后一个字节的结束位置。在 interrupt(2) 上会将监测到的最后一个字节前发生的中断判定为正常。 2) 根据 IIC 协议,请勿将启动位和停止位与数据/地址字节置于一处。

-

集成电路

+关注

关注

5446文章

12465浏览量

372687 -

I2C

+关注

关注

28文章

1547浏览量

130488

原文标题:【干货分享】IIC 协议与编程序列

文章出处:【微信号:FPGA-EETrend,微信公众号:FPGA开发圈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

I2C总线通信原理 如何设计I2C总线电路

I2C总线的优缺点分析

I2C总线与Arduino的接口示例

I2C总线的工作模式介绍

I2C总线协议详细解析

I2C总线故障排除技巧

I2C总线与SPI总线的比较

TMS320C6000 DSP内部集成电路(I2C)模块参考指南

TMS320VC5501/5502/5503/5507/5509 DSP内部集成电路(I2C)模块参考指南

TMS320x280x、2801x、2804x内部集成电路(I2C)参考指南

有关内部集成电路总线(I2C或IIC)的基础知识

有关内部集成电路总线(I2C或IIC)的基础知识

评论