这两天可能很多人都被兆易创新基于RISC-V架构的GD32V刷屏了,可见RISC-V的发展之迅猛。

一、了解GD32V处理器

兆易创新在国内32位MCU中算是一家做的比较好的公司。在前天(2019年8月22日),兆易创新发布了基于RISC-V架构的GD32V系列MCU,算是在业界引起了不小轰动。

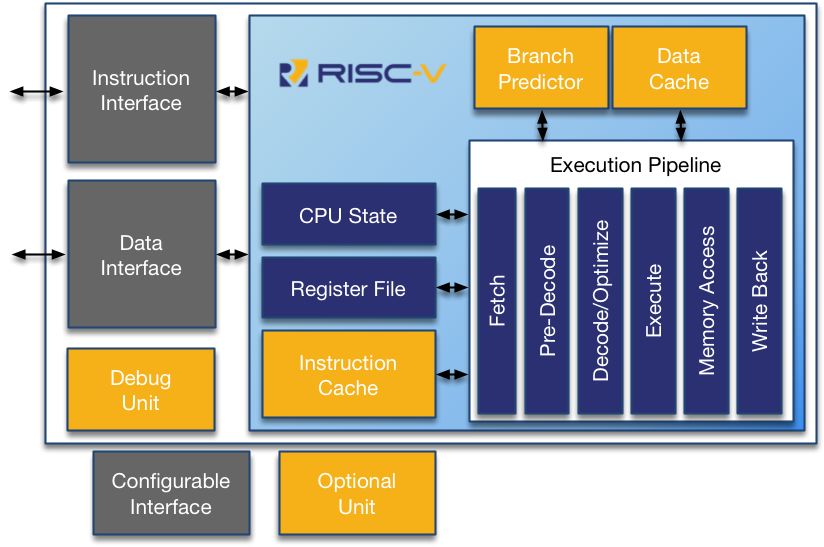

GD32V系列MCU采用了全新的基于开源指令集架构RISC-V的Bumblebee处理器内核,是兆易创新携手中国领先的RISC-V处理器内核IP和解决方案厂商芯来科技,面向物联网及其它超低功耗场景应用自主联合开发的一款商用RISC-V处理器内核。

发布的新品GD32VF103,首批提供了14个型号,包括QFN36、LQFP48、LQFP64和LQFP100等4种封装。供了108MHz的运算主频,以及16KB到128KB的片上闪存和6KB到32KB的SRAM缓存。

二、RISC-V发展历程

RISC:Reduced Instruction Set Computer,即精简指令集计算机。

RISC-V是基于RISC原理建立的免费开放指令集架构(ISA),V是罗马字母,代表第五代RISC(精简指令集计算机),可读作RISC-FIVE。

RISC的历史可追溯到1980年左右,在此之前,人们觉得简单的计算机可能会有用,但是没有很多人去阐述其设计原则,这种简单而有效的计算机一直都是学术界的兴趣。

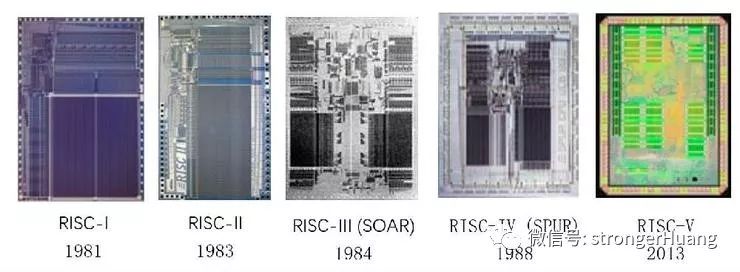

1981年,在David Patterson的带领下,加州大学伯克利分校的一个研究团队起草了RISC-1,这就是今天RISC架构的基础。RISC-1原型芯片有44500个晶体管,拥有31条指令。包含78个32位寄存器,分为6个窗口,每个窗口包含14个寄存器,另外还有18个全局变量,寄存器占用大部分面积,控制和指令只占用芯片面积的6%,而同时代的芯片设计里要占用约50%的面积。

随后在1983年发布了RISC-II原型芯片,包含138个寄存器,分为8个窗口,每个窗口有16个寄存器,另外还有10个全局变量,但是只有39000个晶体管。接着在1984年和1988年发布了RISC-III和RISC-IV。

而RISC的设计理念也催生了一系列新架构,包含了许多我们耳熟能详的名字,如学术上认为比较成功的DEC Alpha、被写入经典教科书的MIPS、绕过指令级并行度障碍,追求线程级并行的SUN SPARC、服务器的王者IBM Power、以及现在统治嵌入式市场的arm。

2010年,Patterson教授的研究团队准备启动一个新项目,需要设计CPU,因而要选择一种指令集。他们调研了包括arm、MIPS、SPARC、X86等多个指令集,发现它们不仅设计越来越复杂,而且还存在知识产权问题。

RISC-V(第五代精简指令集)是David Patterson教授基于其30多年在精简指令集RISC领域的深入积累,在2010年到2014年期间带领团队研发出的最新一代CPU芯片设计指令集。RISC-V是基于精简指令集计算(RISC)原理建立的开放指令集架构(ISA),RISC-V是在指令集不断发展和成熟的基础上建立的全新指令。RISC-V指令集完全开源、设计简单、易于移植Linix系统,采用模块化设计,拥有完整工具链。

我在之前写过一篇文章:第五代精简指令集计算机RISC-V你了解多少?

三、X86和ARM的厮杀

X86 架构和 Arm 架构厮杀多年,x86 没能移动处理器市场,Arm 也没能在服务器市场分到多少羹,两者各自安好,x86 依然在 PC 处理器市场独领风骚,Arm 依然在移动处理器市场稳坐老大。就在大家都认为主流架构市场会以当前格的局长治久安时,发生了中兴事件,打疼了中兴,打来了 RISC-V 崛起的机会。

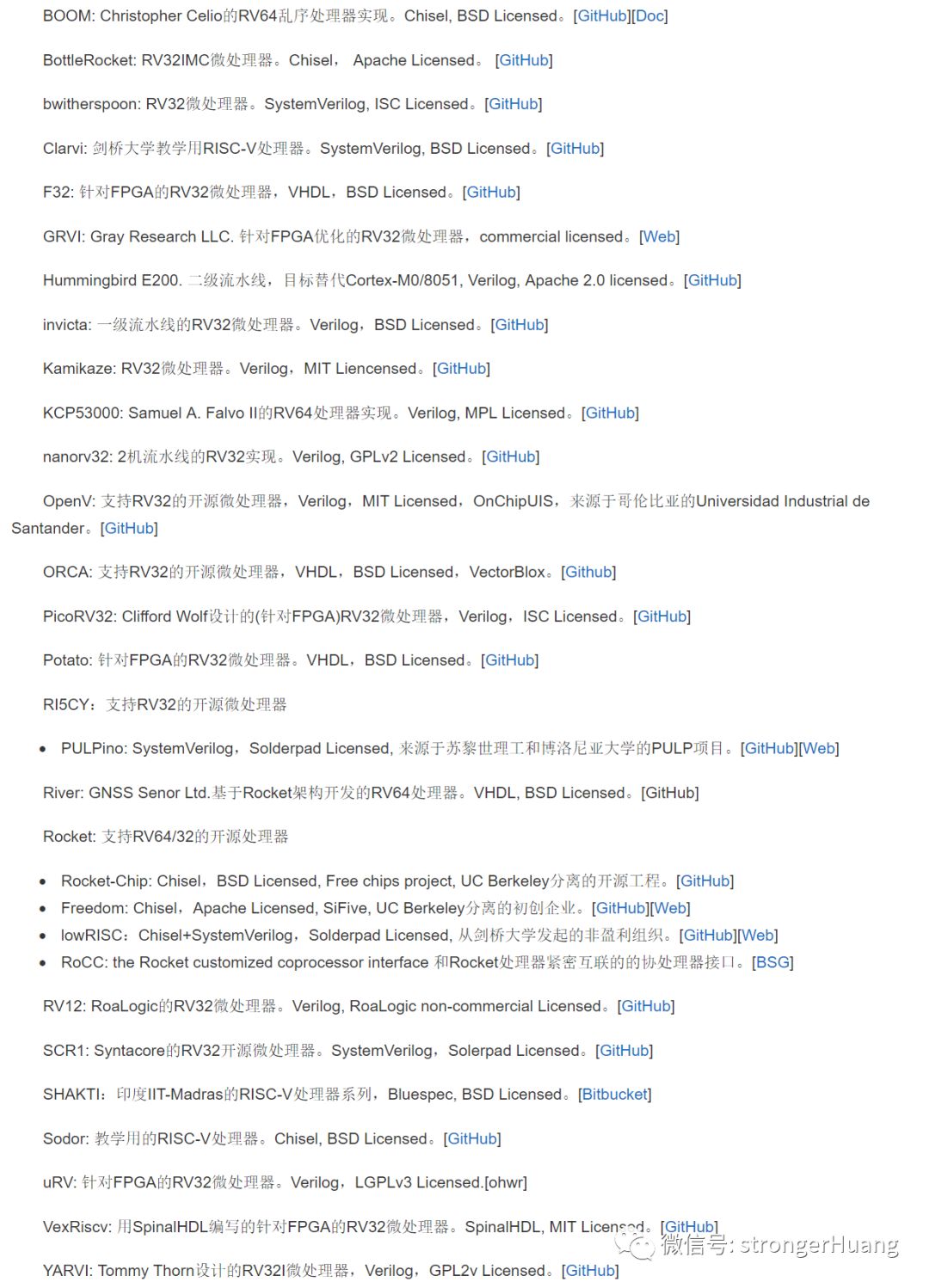

上面说的兆易创新基于开源指令集架构RISC-V的GD32V系列MCU就是一个例子,其实,在GD32V之前还有很多基于RISC-V架构的处理器已经问世。

四、Arm 的随变而变

面对 RISC-V 的猛烈攻势,Arm 看“在眼里急在心里”,不想被人碾压只能迅速应变。熟悉 Arm 授权的用户应该清楚,以前客户如果想基于 Arm 架构设计产品,必须先选择处理器IP授权方案,向 Arm 支付一笔预付款才能取得 Arm 的 IP 设计资料,当客户完成研发、制造、出货后,还需要根据产品出货量向 Arm 支付权利金。显然,对于那些中小企业来说,RISC-V 的开源免费策略更受欢迎,虽然市面上基于 RISC-V 的产品为数不多,但是已经有很多 Arm 阵营的芯片公司在做双重准备,以满足用户可能出现的转移阵地的需求。

面对 RISC-V 咄咄逼人的发展态势,今年 7 月,Arm 推出新的授权模式“Flexible Access”:对于中低阶芯片的授权,未来客户不再需要缴纳“预付款”才能看到设计细节,而是能直接免费取得相关设计档案,并从中评估并选择最适合自己的产品,等到芯片正式生产后再按照制造的数量收费。

其实早在 2010 年 Arm 就发布了 DesignStart 计划,2015 年开放了 Cortex-M0 系统,取消预付授权或者评估费用,2017 年又将用户范围最广的 Cortex-M3 放入了 DesignStart 计划,如今推出“Flexible Access”授权模式无疑对准的是中小企业,这也是“不得已”的选择,在手机和平板市场增量停滞的大环境下,Arm 要想拿到新增用户只能对准初创企业,而这些企业资金有限,在 RISC-V 免费的吸引下及容易抛弃Arm拥抱 RISC-V,为了拿到更多增量市场,Arm 不得不放下“身段”召唤更多的新用户采用 Arm 架构设计产品。

-

处理器

+关注

关注

68文章

20149浏览量

247230 -

ARM

+关注

关注

135文章

9499浏览量

388770 -

RISC-V

+关注

关注

48文章

2793浏览量

51919

发布评论请先 登录

为什么RISC-V是嵌入式应用的最佳选择

大湾区RISC-V生态全景展示:RISC-V生态发展论坛、开发者Workshop和生态应用专区

RISC-V 手册

RISC-V 发展态势与红帽系统适配进展

包云岗:原位替代 ARM,并未真正发挥 RISC-V 的优势

RISC-V和ARM有何区别?

FPGA与RISC-V浅谈

Arm与RISC-V架构的优劣势比较

关于RISC-V芯片的应用学习总结

RISC-V MCU技术

赛昉科技将亮相RISC-V产业发展大会,带来应用、软件、人才三大核心主题分享

RISC-V发展迅猛 ARM有点坐不住了

RISC-V发展迅猛 ARM有点坐不住了

评论