PADS®DFM分析在您的流量中,您可以控制您的设计,在移交给制造业之前执行制造和装配规则检查,以最大限度地减少生产问题,实现更少的旋转/设计修改,并节省产品发布计划中的时间,同时添加Quality.Datasheet,确保视频的可制造性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

视频

+关注

关注

6文章

1999浏览量

74647 -

制造业

+关注

关注

9文章

2432浏览量

56921 -

PADS

+关注

关注

81文章

821浏览量

110579

发布评论请先 登录

相关推荐

热点推荐

Molex推出蜂窝柔性天线的特性与优势-赫联电子

Molex蜂窝柔性天线支持不断发展的LTE和4G蜂窝技术。该器件采用平衡的传输设计,可通过消除额外的电路、频率调谐和电子元件集成,最大限度地减少地面-平面效应、降低成本并减少所需的工程资源。该

发表于 10-14 09:37

MES - 制造执行系统

不同的好处: 生产经理:实时监控生产,提高透明度,减少停机时间IT 部门:提高数据集成度,减少数据孤岛,实现流程自动化质量经理:有了详细的文档资料,

发表于 09-04 15:36

小批量多品种生产困局破冰:选择性波峰焊如何重塑柔性电子制造竞争力

,减少反工和维修的后处理成本。面对通孔密集、大热量器件、高精度、高可靠性要求的复杂电子产品的制造,选择性波峰焊具有显著的优势。

柔性制造时代的选择题

选择

发表于 06-30 14:54

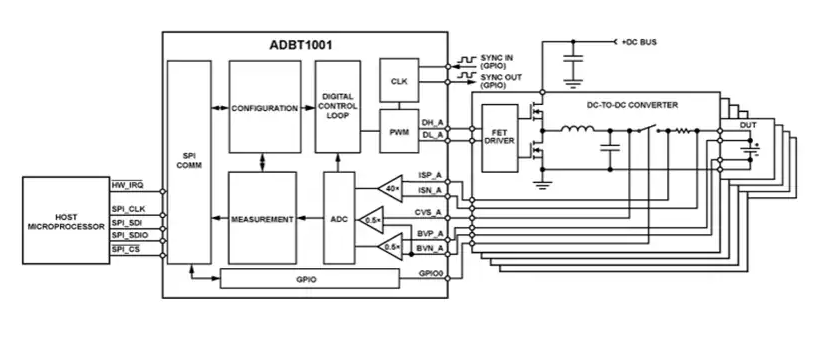

Analog Devices Inc. ADBT1001 4通道AFE数字控制器数据手册

Analog Devices Inc. ADBT1001 4通道AFE数字控制器是功能丰富的灵活数字控制器,用于大容量电池测试和成型制造以及精密电池测试仪器仪表应用。该控制器经优化可最大限度地

华邦电子如何通过绿色制造实现可持续发展

随着环保意识的增强,企业面临着采用可持续做法的巨大压力。#绿色制造 通过减少废弃物、节约能源和有效利用资源,最大限度地减少对环境的影响,从而

PanDao:制造成本影响分析软件工具

在设计阶段测试其光学设计的可生产性以及生产所需的必要光学制造技术。此外,还能基于光学设计参数进行制造成本影响分析,从而优化设计参数以实现最低

发表于 05-12 08:55

PanDao:光学制造链设计

了一种新型的软件工具,可以将可生产性分析和制造链优化集成到光学设计过程中(见图2b)。PanDao通过读取ISO 10110标准中描述的透镜参数和公差,并考虑360多种光学制造技术,

发表于 05-12 08:51

PanDao:通过可生产性调控实现光学设计流程的动态优化

简介

尽管光学设计能够将光学系统的应用参数(如调制传递函数MTF、图像分辨率等)转化为定义明确的技术图纸,但其可生产性评估往往只能事后进行,例如通过人工分析,或者使用近年来出现的PanDao软件

发表于 05-09 08:49

如何最大限度地扩大基于氮化镓 (GaN) 功率放大器的雷达系统的探测距离

(SNR),“脉冲衰减”成为一个问题。 虽然与采用旧工艺的器件相比,基于氮化镓 (GaN) 的功率放大器 (PA) 具有显著的效率和其他优势,但设计人员仍需采用系统级方法,最大限度地减少脉冲衰减及其影响。这将确保远程雷达系统的卓越性能。

TRCX应用:显示面板工艺裕量分析

制造显示面板的主要挑战之一是研究由工艺余量引起的主要因素,如CD余量,掩膜错位和厚度变化。TRCX提供批量模拟和综合结果,包括分布式计算环境中的寄生电容分析,以改善显示器的电光特性并最大限度

发表于 03-06 08:53

LVDS连接器PCB设计与制造

过程中因线宽或线距不合理导致的问题。

4、叠层厚度

LVDS连接器的叠层设计需考虑介质厚度,以满足阻抗要求。同时,叠层设计还需兼顾生产可制造性

发表于 02-18 18:18

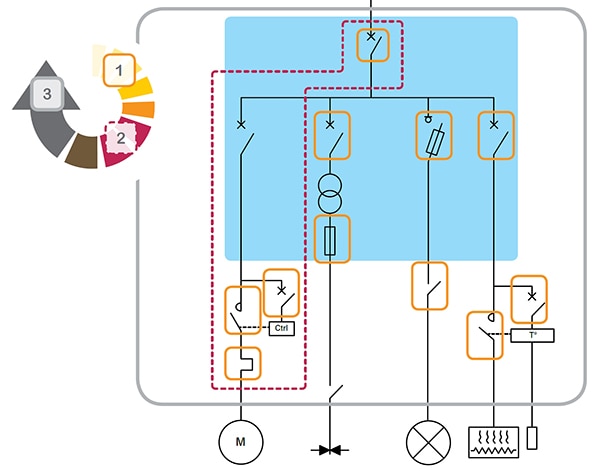

智能电机控制装置如何最大限度地提高恢复能力和正常运行时间

作者:Jeff Shepard 投稿人:DigiKey 北美编辑 在下一代工业 4.0 制造、金属与基础材料加工、矿物提炼与采矿以及像饮用水和污水处理厂之类关键基础设施中,都需要能够最大限度地提高

AN101-最大限度地减少线性稳压器输出中的开关稳压器残留

电子发烧友网站提供《AN101-最大限度地减少线性稳压器输出中的开关稳压器残留.pdf》资料免费下载

发表于 01-09 14:19

•0次下载

可制造性分析以最大限度地减少生产问题

可制造性分析以最大限度地减少生产问题

评论