设计人员在前沿片上系统(SoC)设计中平衡功耗和性能方面面临着持续的困难。更高的电源电压意味着更快的设备,但代价是更高的功耗—在90nm及以下的先进纳米工艺节点发现的高电流泄漏加剧了这个问题。

直到最近,部署有效的低功耗设计策略仍然远远超出主流设计师的范围。然而,通过知识产权(IP)供应商,EDA提供商和独立代工厂的广泛合作,新的低功耗设计方法增强了熟悉的RTL到GDSII流程,使每个设计人员能够优化其功耗和性能的SoC设计。

为了追求市场对复杂移动应用的广泛兴趣,半导体设计人员利用日益先进的CMOS技术提供集成电路(IC),为每一代产品设定尺寸,性能和复杂性的新里程碑。然而,即使新的工艺技术使晶体管密度每18个月翻一番,电池技术仍然显着滞后,需要五年多才能实现相当于两倍的能力。

与此同时,由于与纳米技术相关的泄漏电流增加,每次工艺生成后,先进器件的功耗仍在显着上升。高级微处理器的功耗要求通常超过100W,并且随着设计人员转向更先进的技术节点和更高的时钟速率,威胁增长甚至更高。因此,随着系统制造商面临从较小封装消散更多热量的新要求,增加的功耗已经成为有线和无线系统中系统级的主要问题。

一旦主要关注便携式消费产品,在最小化功耗的同时最大限度地提高性能的需求现已成为包括有线嵌入式产品和高端计算平台在内的更广泛市场领域的关键问题。过去,低功耗设计专家已经能够采用专门的架构方法或特定的电路设计方法,包括时钟门控,频率调整和特殊工艺选项。然而,即使这些方法在很大程度上仍然是最大的半导体公司的专属领域,并且通常仅适用于容量最大的设备。

有效的低功耗设计需要一套兼容的专业功能,可以跨越整个设计链。包括知识产权(IP)模型,图书馆,设计工具和制造能力。反过来,主流低功耗设计的有效解决方案需要IP供应商,图书馆提供商,EDA工具开发人员和代工厂的共同努力。

因此,Silicon Design Chain Initiative的成员最近合作创建了一个跨行业的电源管理解决方案,并在测试设计上验证了该解决方案。这项工作最终成功实现了基于ARM1136JF-S核心模块的芯片的成功实施和芯片验证,该芯片将在ARM参考板中提供。该器件针对移动和无线应用,功耗降低了40%以上。

低功耗设计

器件的功耗来自两个主要来源:基于器件开关活动的动态功耗,以及由于先进的纳米工艺技术降低晶体管阈值电压而增加的漏电流引起的静态功耗。

Silicon Design Chain团队开始证明其低功耗设计系统可以显着降低ARM1136JF-S测试设计中漏电流引起的动态和静态功耗。作为通过系统级电源管理方法提出潜在节省的替代方法的补充,这种低功耗设计方法采用电路级方法来实现这些节省,而无需高度专业化的核心功能。

为了验证这种方法的广泛适用性,该测试芯片开发工作采用了典型工艺,TSMC 90nm G硅工艺和ARM Artisan通用物理IP,包括SAGE-X标准单元库和内存生成器。如下所述,标准单元库增加了扩展电压范围表征,并且单元旨在实现功率降低设计技术。 Cadence Design Systems使用Encounter数字IC设计平台的4.1版开发了一种低功耗设计方法。

动态功耗降低

在这个项目中,设计团队首先解决了动态功耗问题,可以用以下公式表示:/p》

P = KCV 2 F

其中

K 是切换率(晶体管切换的时间分数) C 是电路电容,包括互连和晶体管电容

V 是晶体管的电源电压

F 是工作频率

如该等式所示,功率与电源电压的平方成比例。因此,设计人员只需降低电压即可节省大量的动态功耗。称为电压缩放的方法。

另一方面,降低电源电压会降低晶体管的开关速度。由于此设计需要达到350 MHz以满足ARM开发合作伙伴的要求,因此团队必须有选择地确定设计的哪些部分可以使用电压缩放技术。

在这种情况下,该团队创建了一种多电源电压(MSV)设计,将设计划分为单独的“电压岛”或“电压域”,其中每个域在不同的电源电压下工作,具体取决于其时序要求(图1)。在这里,该团队在一个域中保留了时序关键模块,工作在1.0V的标准90nm电源电压下。具有较少关键时序路径的块被聚合到第二域中,其中电压缩小到0.8V—该部分设计的动态功耗降低了36%。

图1—单独的电压域优化功率和性能

过去,电压域方法在物理设计中引入了额外的复杂性,特别是用于连接适当的电源和电源网络。设计人员通常需要手动插入称为电压电平转换器的特殊转换单元,以在不同电压域之间转换信号,以及钳位单元以提供隔离。

实施这些翻译单元对插入,放置和电源连接提出了挑战。此外,分析不同电压岛上的MSV设计也是一个挑战,因为每个岛的传统分层建模方法对于先进技术节点可能不够准确。

ARM1136核心设计有3400个信号,从0.8V到1.0V域,需要3400个电平移位器。在此流程中,Cadence Encounter设计系统自动将电平移位器插入到设计中,借助提供电压电平移位器和钳位单元的ARM Artisan库。在此过程中,设计系统将这些单元连接到两个电源轨并优化其放置时序,信号完整性对时序和电源布线的影响。

此外,Cadence和ARM合作创建了优化用于Cadence Encounter NanoRoute路由引擎的电平转换器。电平转换器的设计以及它们在ARM1136JF-S内核设计中实现的自动化是实现显着动态功耗降低的关键因素,同时仍能满足激进的时序要求。

为了进一步降低动态功耗要求,这个低功率设计方法也使用时钟门控技术。在典型设计中,各个寄存器相对不频繁地加载数据,但时钟信号在每个时钟周期继续切换,从而驱动容性负载。利用这种技术,门控电路关闭那些不需要加载的寄存器的时钟。通常可以实现动态功耗节省10%到20%的方法。

对于这个测试芯片,Silicon Design Chain团队使用Encounter RTL Compiler执行自动时钟门控,使用Artisan库中集成的时钟门控单元。在这种情况下,自动时钟门控功能使设计团队能够在低功耗芯片中选通85%的寄存器。

整体性能的关键还在于低功耗时钟树综合和高性能时钟树实现。此外,优化两个电压域设计的能力减轻了电压调节放大的困难时序收敛挑战。

使用这种专用电池组合,自动电压调节和时钟门控方法,Silicon Design连锁团队将芯片的动态功耗降低了37.9%。

静态功耗降低

随着设计人员转向更先进的技术节点,他们必须应对急剧增加的漏电流。对于具有0.7V阈值电压(Vt)的130nm工艺,每个晶体管的漏电流约为10-20pA。在0.3V Vt时,每个晶体管的漏电流可达10-20 nA,在较小的几何结构中呈指数增长。总体而言,泄漏功率从《5%=“”= =“”power =“”budget =“”at =“”0.25 =“”micron =“”to =“”20-25 =“”percent =“” at =“”130nm =“”and =“”as =“”much =“”as =“”40-50 =“”percent =“”at =“”90nm。=“”》 5》

在这种低功耗方法中,设计人员通过使用包含一组匹配逻辑单元的库来管理泄漏功耗,这些逻辑单元具有不同的阈值电压(Vt)和相同的物理占用空间。具有较高Vt的电池比具有较低Vt的对应电池表现出较小的漏电流。

然而,较高的阈值电池也表现出较高的电池延迟,降低了整体性能(图2)。因此,设计工具需要能够提供满足最低漏电流性能的网表实现,并同时优化功耗,性能和面积。

图2—电池延迟随着电池阈值电压的降低而增加

对于这个测试芯片,设计团队使用了ARM Artisan库,它为电池提供不同的电压阈值。该团队首先使用Encounter RTL Compiler在综合期间优化设计,以满足350MHz的性能目标,同时最大限度地降低总漏电流。

在布局和布线可获得更准确的寄生信息后,设计然后使用SOC Encounter的路由后泄漏优化来微调泄漏功率和性能。具有不同电压阈值的电池组合以及自动化和一致的设计能力使Silicon Design Chain设计团队能够实现46.7%的泄漏功率节省。

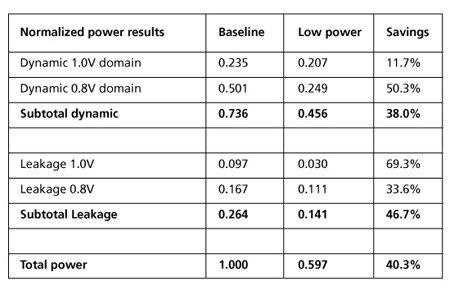

通过降低动态功耗和降低静态功耗的总体节省,可以节省超过40%的总功耗(表1)。

表1—使用低压设计方法测试芯片功耗

功耗分析

以及一组合格的IP组件这种低功耗设计方法依赖于一个实现平台,可以在各种电压电平和工作条件下准确预测和优化性能。在单一设计中使用多个电源会引入时序分析的复杂性,因为精确的延迟计算需要针对每个工作电压的精确延迟模型。

此外,还必须对电平移位器和钳位单元进行适当建模,以正确计算聚合延迟。通过他们的共同努力,Cadence和ARM通过使用有效电流源模型(ECSM)表征这些组件来克服这一挑战,以确保跨多个电压域的准确性。

ECSM模拟晶体管吸收的电流,而不是传统建模方法中的电压。使用传统方法,将特定电压电平的单元延迟精确建模到Spice的几个百分点内,需要为该电压电平创建特征化的时序视图 - 这是一个广泛而昂贵的过程。例如,要在三个不同的工艺/温度拐角处使用六个不同的电压电平,需要18个独立的时序库特征。

此外,大多数延迟计算器和行业标准时序分析仪仅支持单个标称电压电平的精确延迟计算。使用标称以外的电压会引起过多的误差,因为线性降额通常超过Spice的20%,特别是对于速度较慢的低功率电池。

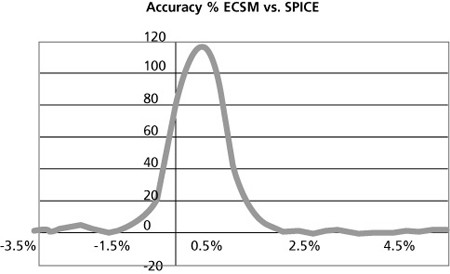

相比之下,MSV设计中的不同工作电压可以覆盖ECSM型号的特点是电压范围内只有三个点。硅设计链芯片中使用的基于ECSM的标准单元模型实现了延迟预测,平均与Spice仿真的2%相关(图3)。对于这个测试芯片,Artisan通过提供lib_ecsm库视图来表征其90-nm库以支持ECSM延迟预测。

图3 - ECSM在Spice模拟的2%范围内达到准确度

设计签收

与任何设计一样,准确性是签核过程中的主要问题。随着多个电压域的复杂性增加,这种类型的低功耗设计可能给签核分析带来额外的困难。对于此测试芯片,Silicon Design Chain使用VoltageStorm和CeltIC NDC来提供所需的精度。

VoltageStorm分析了1.0V和0.8V电网的IR压降,证实设计中的每个晶体管都在必要的电源电压下工作。反过来,这些电压被用作CeltIC NDC(SignalStorm)中基于ECSM的延迟计算器的输入,在两个电源电压域上提供接近Spice精确的时序。在这种类型的设计中,这种精度水平尤其重要,因为在MSV设计中使用的较低电源电压下,IR时序对时序的影响更为明显。

结论

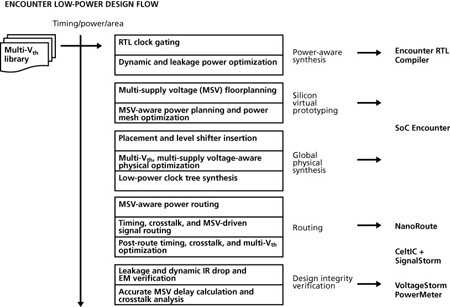

随着半导体公司寻求利用新兴市场机遇,解决新兴纳米设计挑战的需求变得至关重要。通过其协作努力,硅设计链成员公司正在解决这些棘手的跨行业问题。通过创建全面的低功耗设计流程(图4),成员公司为主流SoC设计人员提供了曾经只有最大的半导体公司才能使用的功能。

图4—低功耗设计流程

Silicon Design Chain工程团队在基于ARM1136JF-S处理器的高性能器件中验证了这种硅片中的低功耗设计方法。该测试设备采用TSMC的90G工艺制造,采用了低功耗设计系统,包括ARM精细调谐的物理IP产品和建模方法,以及Cadence的Encounter低功耗设计流程。这种低功耗解决方案将共同降低与主流电子产品开发人员转向高级工艺节点相关的风险。

Robert Aitken是ARM物理IP产品技术的高级架构师,负责内存架构,可制造性设计和可测试性解决方案设计。

George Kuo是Cadence设计链计划的技术总监,负责与战略合作伙伴一起领导技术项目。在加入Cadence之前,他曾在Hughes Aircraft Company和Synopsys担任高性能信号处理器ASIC设计和流程开发的高级职位。

Edward Wan是台积电北美设计服务营销高级总监。在加入台积电之前,万先生是加利福尼亚州米尔皮塔斯领先的芯片设计服务公司Spike Technologies的首席执行官。

-

soc

+关注

关注

38文章

3746浏览量

215702 -

低功耗设计

+关注

关注

0文章

78浏览量

16106

发布评论请先 登录

相关推荐

多元化贴片晶振规格及封装

萨特科技--电路保护器件更新换代在即 市场需求多元化

低功耗语音唤醒IC

面对“多元化”节奏 LED照明企业要如何把控?

低功耗无线模块在多元化未来市场的前景

在多元化未来市场-低功耗的无线模块

低功耗无线模块在多元化未来市场有什么应用

基于FPGA实现低功耗系统设计

益登科技携多元化方案亮相ICC国际元器件中心

低功耗IC卡燃气表的研究与开发

器件的低功耗设计可实现多元化IC

器件的低功耗设计可实现多元化IC

评论