vhdl语言实现16位数据通信,求助!

2014-03-07 14:02:47

使用FPGA实现显示万年历电子时钟,秒,分钟,小时,月份,年份,,有校时,报时,清零功能,显示用数码管,用vhdl语言实现,芯片用的是EP2C35F672C8,校时用键盘控制,现在仿真没有成功,我

2017-04-19 14:33:14

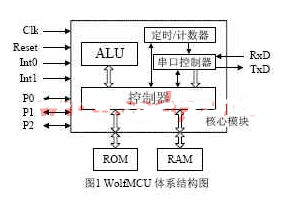

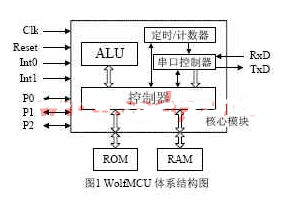

他CPU系统之间的数据通信提到日程上,得到人们的急切关注。本文介绍利用VHDL语言实现 FPGA与单片机的串口异步通信电路。整个设计采用模块化的设计思想,可分为四个模块:FPGA数据发送模块,FPGA

2011-11-24 16:10:01

希望在今后的学习中大家多多帮助,先来几个基础的verilog 教材吧 现在我用到了FPGA关键分配的知识。 不过还是想系统的学习一下。那就先从软件的使用和语法开始学习吧。 完整的pdf格式文档电子发烧友下载地址(共31页): FPGA中文VHDL语言教程.pdf

2018-07-04 01:11:32

设计RISC微处理器需要遵循哪些原则?基于FPGA技术用VHDL语言实现的8位RISC微处理器

2021-04-13 06:11:51

VHDL 主要用于描述数字系统的结构、行为、功能和接口。除了含有许多具有硬件特征的语句外,VHDL 在语言形式、描述风格和句法上与一般的计算机高级语言十分相似。VHDL 的程序结构特点是将一项

2018-09-07 09:04:45

结 语用VHDL语言实现了多DSP局部总线到标准VME总线普通I/O模块和中断请求模块的设计,双口RAM的存储空间映射到工控机的存储空间的地址为0XC0410000~0XC0413FFFC。使用32 MHz时钟时.通信速率町达16 MB/s,能够满足雷达信号处理板到终端通信的要求。来源:***

2019-04-12 07:00:09

采用自顶向下的设计方法,即从系统总体要求出发,自上至下地将设计任务分解为不同的功能模块,最后将各功能模块连接形成顶层模块,完成系统硬件的整体设计。本文用FPGA芯片和VHDL语言设计了一个数字电压表

2012-10-26 15:46:00

请教大家怎么用VHDL语言实现减法运算?在FPGA设计时又该怎么操作呢?

2012-05-17 20:07:12

如何用VHDL 语言实现右移位啊?求大神帮看看为什么实现不了右移位?library ieee;use ieee.std_logic_1164.all;use

2016-05-28 15:46:38

vhdl语言实例大全下载

2008-05-20 09:36:01

在PSOC中,怎样用C语言实现整型向字符型的转换?

2012-11-19 15:43:46

C语言实现常用排序算法是什么?

2021-10-19 06:41:46

CRC算法和c语言实现

2012-08-20 19:21:44

网上的资料,程序原理与实现上主要参考了“PID控制算法的C语言实现.(绝对的好东西)”。本次PID主要是通过固态继电器控制加热片进行加热,温度探测使用的DS18B20,稳定后在0.5

2022-01-14 09:01:15

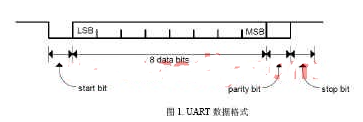

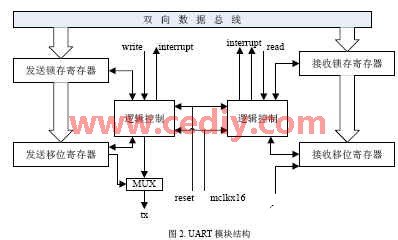

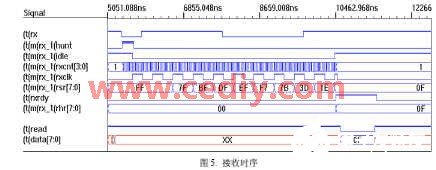

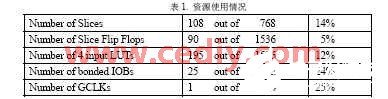

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA片上UART的设计,给出了仿真结果。关键词:通用异步收发器;串口通信;现场可编程逻辑器件;有限状态机

2019-06-21 07:17:24

请问使用VHDL语言设计FPGA有哪些常见问题?

2021-05-06 09:05:31

上限制了错误的产生,调试较容易。VHDL的系统抽象能力比VerilogHDL强,在系统描述上占有一定的优势,但在门级描述上稍显逊色。本设计软件模块框图如图1所示,共8个模块。在本系统中,密码由4位十进制

2021-07-03 08:00:00

不知道有没有大神做过:基于FPGA的图像边缘检测系统设计,用VHDL语言实现

2018-05-10 00:22:07

语言进行CPLD/FPGA设计开发,Altera和Lattice已经在开发软件方面提供了基于本公司芯片的强大开发工具。但由于VHDL设计是行为级设计,所带来的问题是设计者的设计思想与电路结构相脱节,而且

2019-06-18 07:45:03

基于Proteus和C语言实现一共四个题目,有没有人愿意尝试一下?

2021-07-14 06:20:45

本文介绍应用美国ALTERA公司的MAX+PLUSⅡ平台,使用VHDL硬件描述语言实现的十六路彩灯控制系统。

2021-04-19 07:43:57

如何使用C语言实现模糊PID控制?

2021-09-24 08:54:18

单片机实验:使用c语言实现LED流水灯目的:实现一个简单的流水灯程序仿真软件:Portues编程软件:KeilPortues 原理图绘制:需要用到的模块:单片机:AT89C51电容

2021-11-30 07:52:33

利用现场可编程门阵列(FPGA)和VHDL 语言实现了PCM码的解调,这样在不改变硬件电路的情况下,能够适应PCM码传输速率和帧结构变化,从而正确解调数据。

2021-05-07 06:58:37

本文介绍利用VHDL语言实现 FPGA与单片机的串口异步通信电路。

2021-04-29 06:34:57

如何利用c语言实现中文“大”字的显示?

2021-11-02 06:25:39

帧同步是什么工作原理?如何用VHDL语言实现帧同步的设计?

2021-04-08 06:33:59

关于用QuartusⅡ软件实现编程调试,用VHDL语言描述该逻辑关系。多次尝试编写,并不能准确描述逻辑关系,以及进行编程调试,对于vhdl语言不能准确应用,想请教一下结构体的相关逻辑语言。

2022-05-04 12:21:32

老大看到OOP编程很好,就让我学,怎么用C语言实现OOP编程的,请大侠指点

2019-10-30 03:45:28

、组合、多态等面向对象的功能,但C语言有struct和函数指针。我们可以用struct中的数据和函数指针,以此来模拟对象和类的行为。所以在正式开始设计模式前,先看看如何用C语言实现面向对象编程。本章针对面向对象的封装、继承、组合、多态给出C语言的实现方法。1.1 封装封装是指对象仅暴露必要的对外接口(这里

2021-07-12 07:24:18

小白求助,求基于Proteus和C语言实现的程序和仿真

2021-10-19 06:20:34

串行通信发送器是什么工作原理?怎么用VHDL语言在CPLD上实现串行通信?

2021-04-13 06:26:46

在语法和风格上类似于高级编程语言,可读性好,描述能力强,设计方法灵活,可移植性强,因此它已成为广大EDA工程师的首选。目前,使用VHDL语言进行CPLD/FPGA设计开发,Altera和Lattice

2019-08-08 07:08:00

本人小菜鸟,开始学FPGA的时候学的Verilog语言,后来因为课题组前期的工作都是VHDL就该学VHDL了。最近听了几个师兄的看法,说国内用VHDL的已经很少了,建议我还是坚持用Verilog,小菜现在好纠结,请问到底应该用哪种语言呢?望各位大神指点!

2015-07-08 10:07:56

感觉模拟IC设计就应该是设计模拟电路.设计运放等,通过设计电路、在硅片上搭建TTL.CMOS......从而做成IC芯片;而我经常看到说IC设计就是使用VHDL语言设计IC,写好VHDL语言后烧录到FPGA.CPLD.......从而做成芯片。我想问的是这两者有什么区别?

2018-08-29 09:45:43

刚接触FPGA 想用FPGA实现422通讯 求大牛给一个实现UART的VHDL的程序

2013-12-05 20:40:39

最近在做个课题,需要用FPGA中的verilog语言实现BPSK调制,fpga不是很会,望大神指导下,急求代码啊!谢谢

2013-03-06 18:12:36

),有时我们不需要使用完整的UART的功能和这些辅助功能。或者设计上用到了FPGA/CPLD器件,那么我们就可以将所需要的UART功能集成到FPGA内部。使用VHDL将UART的核心功能集成,从而使整个设计更加紧凑、稳定且可靠。本文应用EDA技术,基于FPGA/CPLD器件设计与实现UART。

2012-05-23 19:37:24

各位大神求救啊用verilog语言实现电子钟

2014-05-04 16:37:51

如题,我用的DSP开发板是TMSC5535,需要用到Hibert滤波,需要用汇编语言实现,但是滤波器的系数是复数,请问汇编语言要怎么实现?(汇编语言实数滤波我已经会了),谢谢!

2018-07-31 07:24:29

用VHDL语言实现乐曲演奏电路本程序是用VHDL对《梁祝协奏曲》中《化蝶》部分的乐曲电路实现。

2011-08-18 10:31:53

VHDL硬件描述语言教学:包括fpga讲义,VHDL硬件描述语言基础,VHDL语言的层次化设计的教学幻灯片

2006-03-27 23:46:49 93

93 UART 4 UART参考设计,Xilinx提供VHDL代码 uart_vhdl

This zip file contains the following folders

2009-06-14 08:57:14 113

113

介绍了用VHDL 语言在硬件芯片上实现浮点加/ 减法、浮点乘法运算的方法,并以Altera

公司的FLEX10K系列产品为硬件平台,以Maxplus II 为软件工具,实现了6 点实序列浮点加/ 减法

2009-07-28 14:06:13 85

85 CRC算法原理及C语言实现:本文从理论上推导出CRC 算法实现原理,给出三种分别适应不同计算机或微控制器硬件环境的C 语言程序。读者更能根据本算法原理,用不同的语言编写出独特

2009-09-23 23:38:50 31

31 本文设计了一种基于 FPGA 的UART 核,该核符合串行通信协议,具有模块化、兼容性和可配置性,适合于SoC 应用。设计中使用Verilog HDL 硬件描述语言在Xilinx ISE 环境下进行设计、仿真,

2009-11-27 15:48:51 17

17 用JAVA语言实现RSA公钥密码算法:本文阐述了公开密钥密码体制RSA算法的原理及实现技术。并在此基础上,给出了JAVA语言实现的RSA算法源代码。关键词:ILSA体制;公钥;密钥

2010-02-10 10:27:15 58

58 本文设计了一种在数字通信系统中的数字锁相位同步提取方案,详细介绍了本设计的位同步提取原理及其各个组成功能模块的VHDL语言实现,并在Quartus II开发平台上仿真验证通过。本

2010-08-06 14:28:08 64

64 文章介绍了一种在现场可编程门阵列(FPGA)上实现UART 的方法。首先阐述了UART 异步串行通信原理,然后介绍了实现UART异步串行通信的硬件接口电路及各部分硬件模块,以及用硬件

2010-08-06 16:24:13 55

55 阐述密码控制设计的基本原理。介绍了VHDL语言的特点以及基本的语法结构。在MAX+plusⅡ开发软件环境下,利用VHDL硬件描述语言实现密码控制系统设计,并对其系统各个模块进行仿真

2010-12-16 16:10:37 0

0 阐述了4PSK调制器的基本原理,给出调制系统设计框图。在MAX+plusII环境下,利用VHDL语言实现了4PSK调制器设计,并对系统的各模块仿真。采用VHDL模块化和自上而下的设计方法,提高了

2010-12-20 17:31:28 51

51 用VHDL语言实现3分频电路

标签/分类:

众所周知,分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁相

2007-08-21 15:28:16 5527

5527 用C语言实现FFT算法

/*****************fft programe*********************/#include "typedef.h" #include "math.h"

struct compx EE(struct compx

2008-10-30 13:39:56 6179

6179 【摘 要】 通过设计实例详细介绍了用VHDL(VHSIC Hardware DescriptionLanguage)语言开发FPGA/CPLD的方法,以及与电路图输入和其它HDL语言相比,使用VHDL语言的优越性。

2009-05-10 19:47:30 1111

1111

用VHDL语言实现3分频电路(占空比为2比1)

分频器是FPGA设计中使用频率非常高的基本设计之一,尽管在目前大部分设计中,广泛使用芯片厂家集成的锁

2009-06-22 07:46:33 7831

7831 基于VHDL语言的智能拨号报警器的设计

介绍了以EDA技术作为开发手段的智能拨号报警系统的实现。本系统基于VHDL语言,采用FPGA作为控制核心,实现了远程防盗报警。该

2009-10-12 19:08:43 1167

1167

数字电压表的VHDL设计与实现

介绍数字电压表的组成及工作原理,论述了基于VHDL语言和FPGA芯片的数字系统的设计思想和实现过程。 关键词:数字电压表;VHDL语

2009-10-12 19:14:32 1628

1628

采用CPLD/FPGA的VHDL语言电路优化原理设计

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是IEEE工业标准硬件描述语言,是随着可编程逻辑器件(PLD)的发展而发展起

2010-03-19 11:38:02 2318

2318

利用一块芯片完成除时钟源、按键、扬声器和显示器(数码管)之外的所有数字电路功能。所有数字逻辑功能都在CPLD器件上用VHDL语言实现。这样设计具有体积小、设计周期短(设计过

2011-09-27 15:08:56 366

366 UART 是广泛使用的串行数据通讯电路。本设计包含UART 发送器、接收器和波特率发生器。设计应用EDA 技术,基于FPGA/CPLD 器件设计与实现UART。

2011-12-17 00:15:00 57

57 为了实现某生产线上MCU的数据采集,设计了一种基于FPGA和UART的数据采集系统,并完成系统的软硬件设计。整个设计完全采用硬件逻辑VHDL语言,集成在一枚Altera的cyclone芯片内,设计了单

2012-09-25 14:24:15 41

41 DSP算法的c语言实现,又需要的朋友下来看看。

2016-05-09 10:59:26 0

0 Xilinx FPGA工程例子源码:FM收音机的解码及控制器VHDL语言实现

2016-06-07 14:13:43 11

11 在基于FPGA芯片的工程实践中,经常需要FPGA与上位机或其他处理器进行通信,为此设计了用于短距离通信的UART接口模块。该模块的程序采用VHDL语言编写,模块的核心发送和接收子模块均采用有限状态机

2017-11-18 11:33:01 5153

5153 目前许多FPGA的逻辑资源(LE)都已超过1万门,使得片上可编程系统SOPC已经成为可能。算术逻辑单元ALU应用广泛,是片上可编程系统不可或缺的一部分。利用VHDL语言在FPGA芯片上设计ALU的研究较少,文中选用FPGA来设计32位算术逻辑单元ALU,通过VHDL语言实现ALU的功能。

2018-07-22 11:22:00 6949

6949

4个重要算法C语言实现源代码

2018-06-10 08:00:00 12

12 FPGA芯片却没有这个特点,所以使用FPGA作为处理器可以有两个选择,第一个选择是使用UART芯片进行串并转换,第二个选择是在FPGA内部实现UART功能。

2019-10-18 07:54:00 2317

2317

的UART的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 15:51:05 7

7 的实现方法,具体描述了发送、接收等模块的设计,恰当使用了有限状态机,实现了FPGA上的UART的设计,给出仿真结果。

2020-07-07 17:28:03 10

10 基于以上讨论,可以看出ASIP+FPGA设计模式可以从很大程度上解决引言中提到的两个难题。为了进行更深入的研究,我们对该设计模式进行了尝试,用VHDL硬件描述语言在FPGA上实现了一个8位微处理器

2020-07-28 17:44:49 562

562

本文档的主要内容详细介绍的是使用Quartus和VHDL语言实现的LPC时序的工程文件免费下载。

2020-09-18 16:49:00 20

20 本文档的主要内容详细介绍的是基于VHDL硬件描述语言实现CPSK调制的程序及仿真。

2021-01-19 14:34:15 11

11 本文档的主要内容详细介绍的是使用VHDL硬件描述语言实现基带信号的MASK调制的程序与仿真。

2021-01-19 14:34:17 13

13 本文档的主要内容详细介绍的是使用VHDL硬件描述语言实现基带信号的MFSK调制的程序与仿真。

2021-01-19 14:34:19 4

4 本文档的主要内容详细介绍的是如何使用VHDL硬件描述语言实现基带信号的MPSK调制。

2021-01-19 14:34:21 2

2 本文档的主要内容详细介绍的是使用VHDL硬件描述语言实现基带码发生器的程序设计与仿真免费下载。

2021-01-20 13:44:16 11

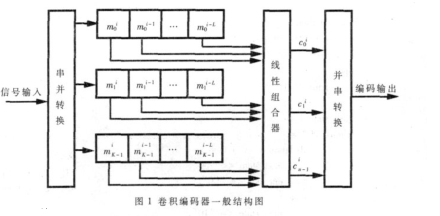

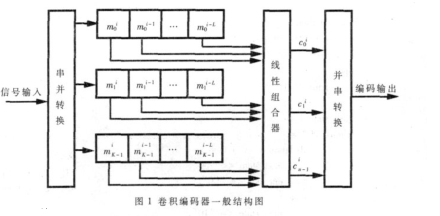

11 介绍并用VHDL语言实现了卷积编码和维特比译码。根据编码器特征设计了一种具有针对性的简洁的维特比译码器结构,

2021-05-12 15:22:41 2112

2112

基于FPGA的UART模块设计与实现介绍说明。

2021-06-01 09:43:30 19

19 CRC校验算法原理及c语言实现

2021-11-30 10:04:07 8

8 累加校验和C语言实现

2021-11-29 18:06:11 10

10 这里我想主要介绍下在C语言中是如何实现的面向对象。知道了C语言实现面向对象的方式,我们再联想下,C++中的class的运行原理是什么?

2022-10-12 09:12:27 1578

1578 本文介绍利用VHDL语言实现FPGA与单片机的串口异步通信电路。

2023-08-03 15:45:37 790

790

电子发烧友网站提供《基于VHDL语言实现远程防盗报警设计.pdf》资料免费下载

2023-11-08 14:33:11 0

0 FPGA芯片主要使用的编程语言包括Verilog HDL和VHDL。这两种语言都是硬件描述语言,用于描述数字系统的结构和行为。

2024-03-14 16:07:38 85

85

电子发烧友App

电子发烧友App

评论