按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

2021-01-22 09:46:34 2138

2138

通过按键检测实验,检测开发板的按键功能是否正常,了解硬件描述语言和FPGA的具体关系,学习PDS View RTL Schematic的使用。

2021-02-02 13:22:00 4091

4091

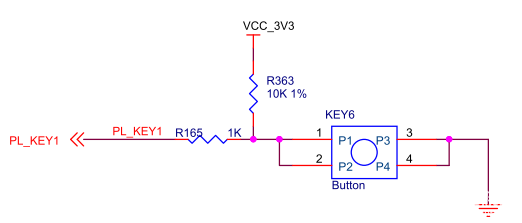

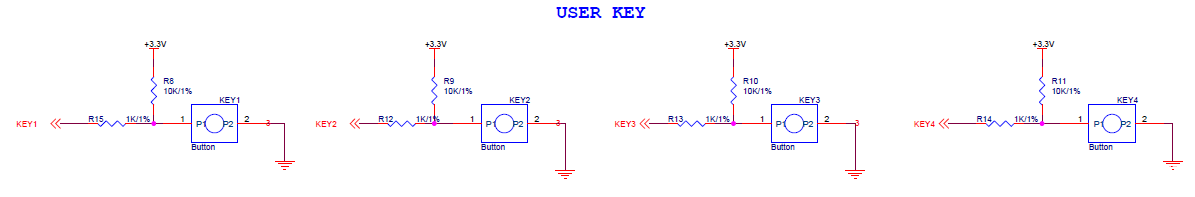

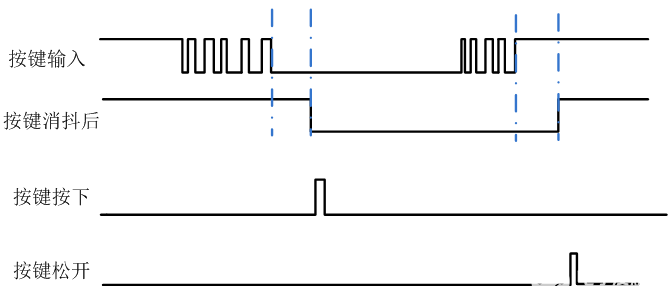

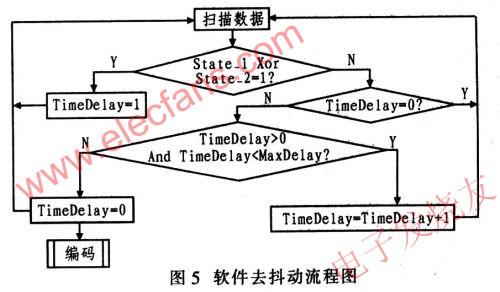

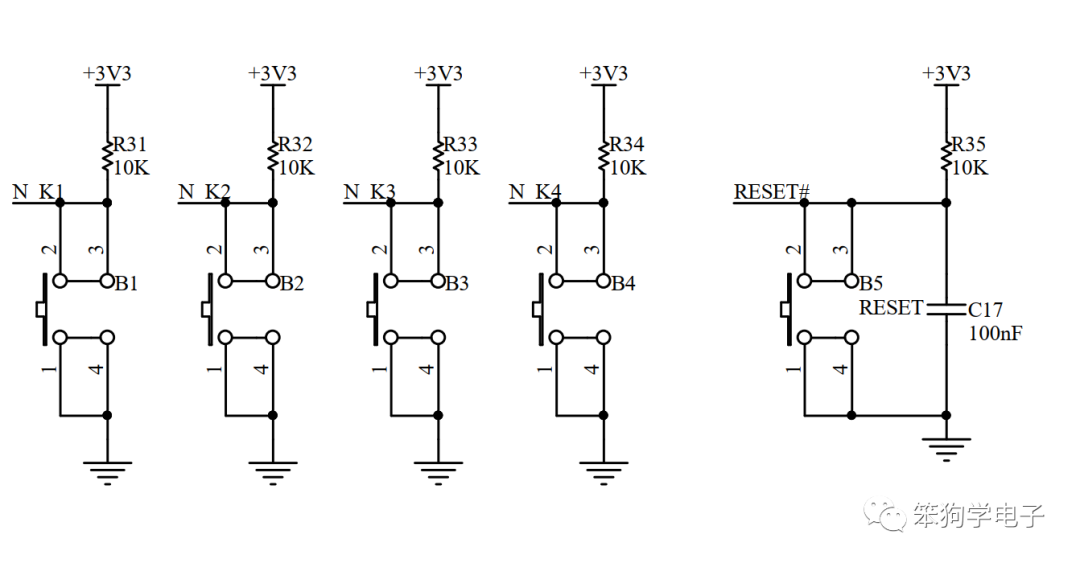

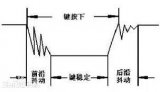

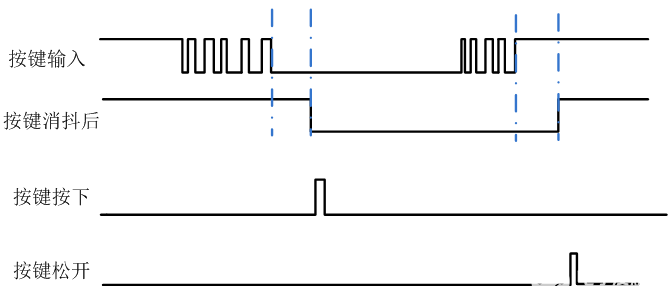

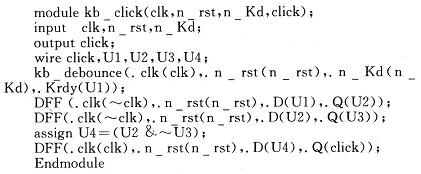

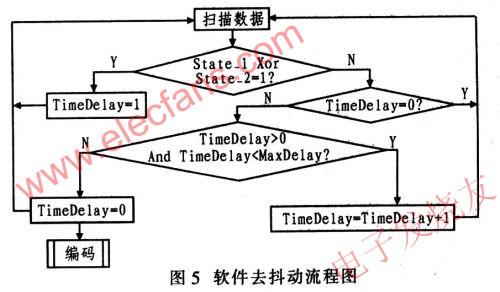

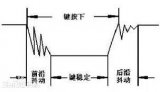

按键做为基本的人机输入接口,在很多电子设计中都能见到,由于机械特性,在按键按下或松开的时候,按键输入值是有抖动的,无论按下去是多平稳,都难以消除抖动,按键消抖方式有很多,本实验主要是通过FPGA计时

2021-02-04 13:24:00 5030

5030

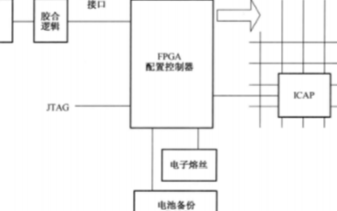

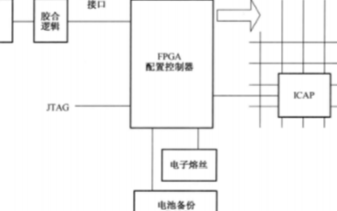

FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为

2022-09-22 09:13:59 3375

3375 :适用于各种不同的应用,如通信、工业控制、视频处理等。

专用FPGA :针对特定的应用领域进行优化,如高速接口、网络处理、AI加速等。

上述分类并非互斥,某些FPGA可能同时属于多个类别。

2024-01-26 10:09:17

FPGA按键消抖的方法

2015-05-01 16:12:25

文章目录目标功能目标功能实现按键点灯,当按键按下时一个LED亮起,松开后LED熄灭。使用开发版型号:AX309

2022-01-18 09:29:09

FPGA与CPLD的辨别和分类,总结的太棒了

2021-04-29 06:34:19

`假设你将一个机械按键开关与FPGA相连,你可能会遇上一些麻烦。下图是一个按键开关按下10次的结果。【问题所在】要想将开关与FPGA相连,你的连接方式可能是这样的:但机械开关最大的问题就在于它们会

2019-08-01 18:11:13

本帖最后由 温家辉 于 2019-9-23 09:05 编辑

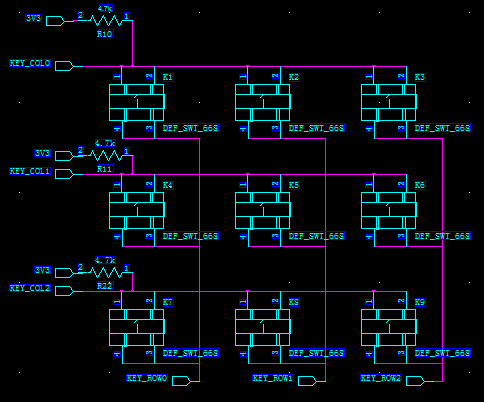

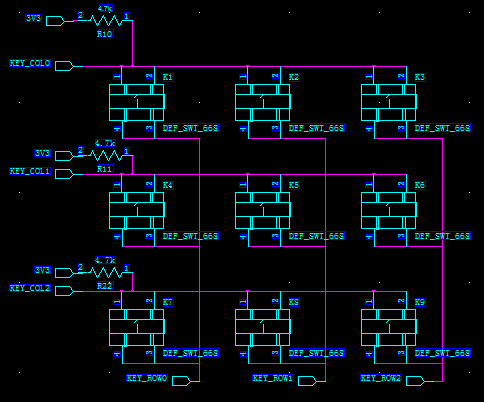

用FPGA实现了加减乘除,4*4矩阵按键作为输入,LCD1602显示,代码写了一个多星期,终于完成了所有功能,开心,,,,注意,矩阵按键需要设置上拉电阻

2019-09-23 09:03:47

...............................................111. 回顾 这次我们继续给玩转LED加入些新元素,使用按键控制LED。点亮LED是利用了FPGA输出

2012-02-27 11:49:08

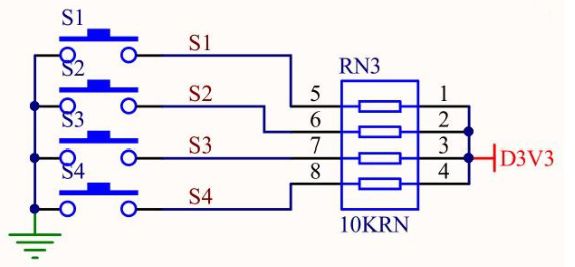

蓝桥杯单片机比赛系列3按键扫描按键扫描原理及实现在独立键盘模式时,要将J5跳在BTN模式。也就是J5中2,3短路。此时S7,S6,S5,S4一端直接接地,一端连接P30,P31,P32,P33。按键

2022-02-17 06:10:41

IO口模式的分类有哪些?怎么使用?

2022-01-20 07:15:44

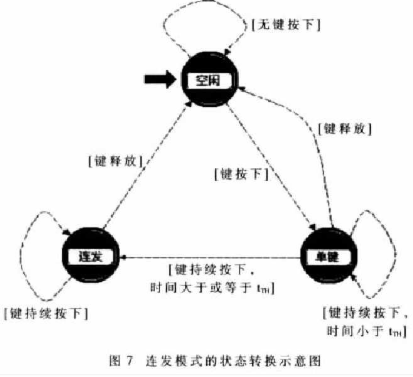

目录一、MPU6050简介1.1、按键的种类1.2、按键的两种使用模式1.3、按键使用过程二、按键理论实现2.1、单击理论流程图2.2、双击理论流程图2.3、长按理论流程图2.4、实现流程思想三

2022-02-10 07:12:42

`Xilinx FPGA入门连载22:经典模式流水灯实验特权同学,版权所有配套例程和更多资料下载链接:http://pan.baidu.com/s/1jGjAhEm 1 功能简介本实例使用一个拨码

2015-11-06 13:48:22

求程序ch582如何在用户程序内跳转到ISP模式,实现免按键下载呢?

2022-07-21 06:03:58

本帖最后由 eehome 于 2013-1-5 10:10 编辑

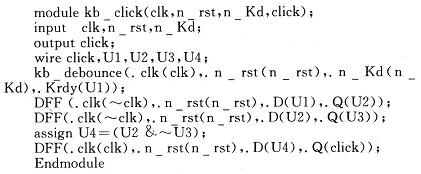

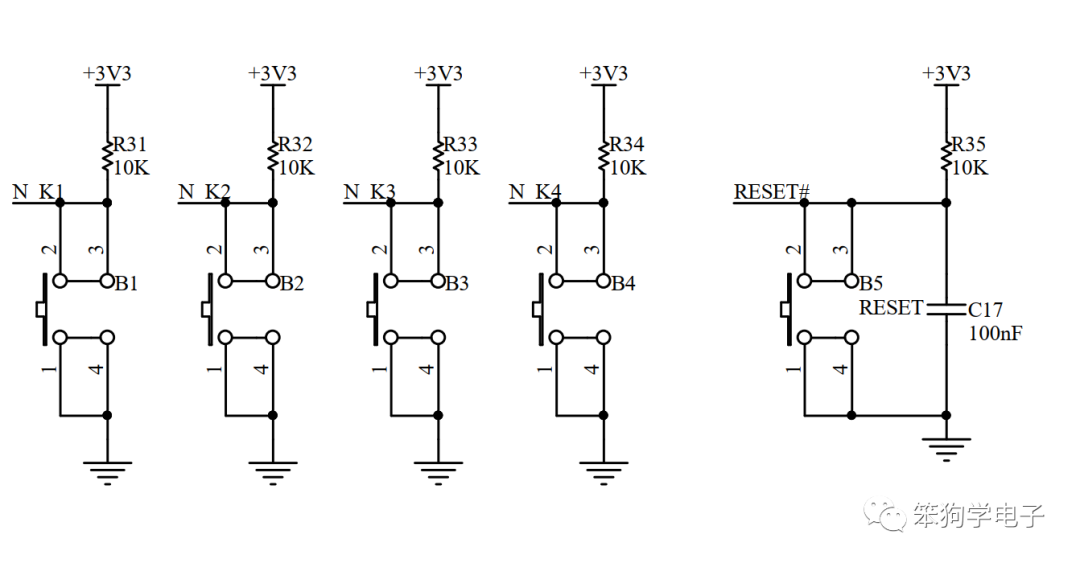

本节将重点讲解,用FPGA实现按键去抖的方法,在以往的按键去抖中,大部分采用的是单片机去抖方法。这里我们将介绍FPGA的实现

2012-03-19 14:48:40

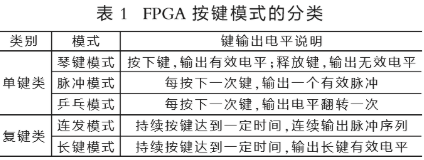

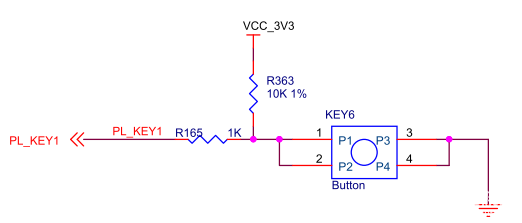

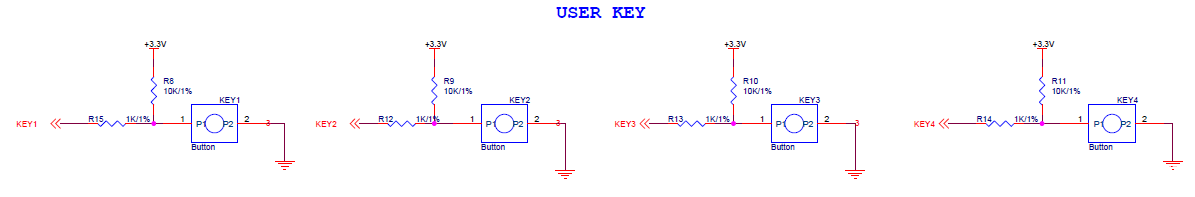

的方式,对于不同的按键可以设计不同的计数器计数时间,更具有稳定性,也节约了一定成本,非常建议大家使用。1.5 按键采集实现 理解了按键工作的原理,我们来在FPGA中实现按键采集。 我们先将设计目标

2019-11-29 14:49:14

本视频是Runber FPGA开发板的配套视频课程,主要介绍按键消抖的方法和FPGA如何实现按键消抖,帮助用户快速掌握信号上升沿、下降沿的识别和FPGA按键消抖的设计方法。本视频教程利用Runber开发板进行讲解,视频课程注重基础知识和设计思路的讲解,帮助初学者理解和掌握FPGA设计。

2021-04-13 10:35:48

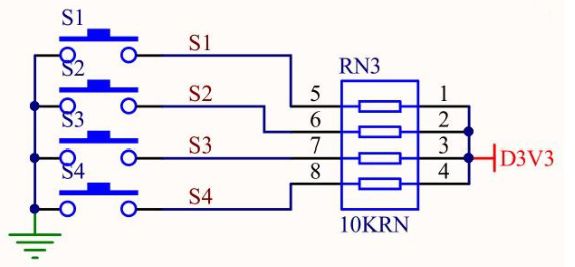

小伙伴都有了解。锆石A4 FPGA开发板上面的触摸按键是通过触摸芯片TTP226 检测。TTP226可选直连、矩阵和串行这三种模式,直连可输入8路Pad触摸按键,开发板采用的便是此模式,不过开发板只用了4

2016-09-04 23:19:14

,首先分几个模块实现不同的功能,然后将子模块组合实现总功能。消抖:因为在按键按下的过程中存在按键开关接触与不接触的临界点,这些抖动可能会被FPGA捕捉到,造成误操作。有按键消抖模块,BEEP模块,LED

2020-01-11 12:47:23

:我是按照官方手册的主串模式连接的电路,请问这样可以实现上述功能吗?还有模式选择端口M0,M1,M2是直接都接地呢,还是说要通过跳冒来设置?都接地为主串模式,这种情况下,能否实现方式一那样直接下载程序到FPGA呢?求高手解答。谢谢。

2013-10-18 10:06:47

一直都想去学习低功耗,今天终于学到了;写了利用 PA0接的KEY按键来实现唤醒和进入待机模式的功能,然后利用PB5接的LED指示状态。

2021-12-30 06:22:51

时,为独立按键模式。图2.22 矩阵按键模式设置的跳线插座 如表2.5所示,这是FPGA与4X4矩阵按键的引脚信号定义。表2.5 FPGA与4X4矩阵按键的引脚信号定义信号名方向功能描述 BUT[3

2017-11-03 18:46:36

的输出信号。若FPGA输出的行信号为高电平时,无论是否有按键被按下,列信号输入到FPGA的电平始终为高电平,这是无法实现任何的矩阵按键值采集的;若FPGA输出的行信号为低电平时,没有按键按下,那么列

2018-05-14 15:34:17

1、基于FPGA开发板的矩阵键盘实验设计与实现在键盘中按键数量较多时,为了减少I/O口的占用,通常将按键排列成矩阵形式。在矩阵键盘中,行线和列线不直接连通,而是通过一个按键进行连接。本实验实现的功能

2022-07-08 17:32:56

基于FPGA的交织编码技术研究及实现中文期刊文章作 者:杨鸿勋 张林作者机构:[1]贵州航天电子科技有限公司,贵州贵阳550009出 版 物:《科技资讯》 (科技资讯)年 卷 期:2017年 第

2018-05-11 14:09:54

和实测验证,该算法能有效快速地消除回声;同时,该算法应用灵活,能实现多路的回声消除,在VOIP终端设备上具有较强的应用价值和应用前景。页 码:9-11页主 题 词:回声消除VOIPFPGA Echo cancellationVOIPFPGA学科分类:TN91核心收录:暂无

2018-05-08 10:23:36

的进化。之后,SPLD、CPLD和FPGA在20世纪80年代早期发展起来。表9.2 PLD分类PLD分类如表9.2所示。以下是用于理解现场可编程设备的关键术语。PAL是一种密度相对较小的现场可编程

2022-10-27 16:43:59

设计由计算部分、显示部分和输入部分四个部分组成,计算以及存储主要用状态机来实现。显示部分由六个七段译码管组成,分别来显示输入数字,输入部分采用4*4矩阵键盘,由0-9一共十个数字按键,加减乘除四个运算符按键,一个等号按键组成的。通过外部的按键可以完成加、减、乘、...

2021-11-11 08:31:27

配置选择上篇【FPGA实验】流水灯实验记录了如何上手FPGA,实现简单的流水灯效果,本篇将稍微升级一些,通过按钮实现多种形态的流水灯。此次仍使用正点原子的开拓者FPGA开发板,配置和上篇一致。功能

2022-01-18 10:28:27

;另一种是扫描阵列方式,适用于大量按键,但不能多键同时动作。因此,需要开发一种既适合大量按键又适合多键同时动作,并能节省单片机(MCU)的口线资源的多按键状态识别系统。利用FPGA技术设计多按键状态识别系统可以实现识别60个按键自由操作,并简化MCU的控制信号,但具体该怎么做呢?

2019-08-02 06:21:32

如何利用KEY_UP按键来实现唤醒和进入待机模式的功能?

2022-01-19 07:06:14

GPCM接口读取一个字节需要4个周期,但回读数据在FPGA的连续周期内连续可用。我可以在非连续模式下使用回读过程吗?我想通过CSI_B信号控制这个读取过程。但是对于“UG380(v2.5)2013年1月23日”版本中的回读过程的连续或非连续模式,没有明确的解释。这是否可以在非连续模式下实现回读过程?

2019-11-04 09:42:34

请问怎么利用FPGA实现模式可变的卫星数据存储器纠错系统?

2021-04-13 06:10:54

怎么用matlab实现对硬币的识别与分类?需要用到哪些函数?求赐教。。。

2013-05-08 17:18:59

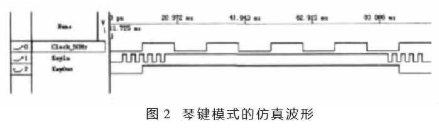

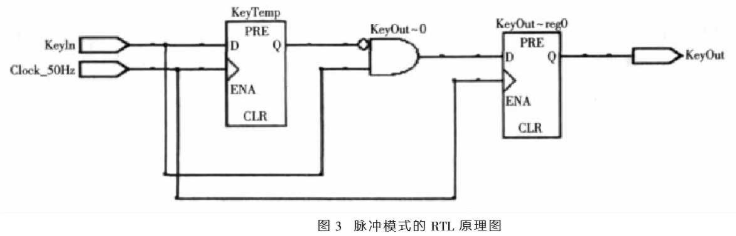

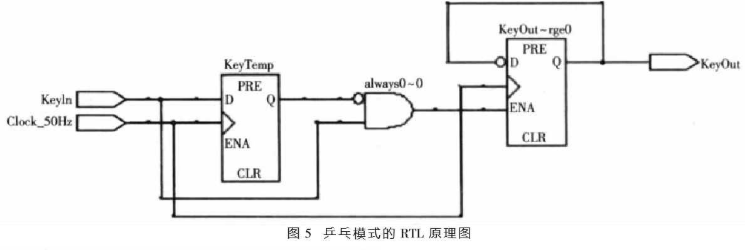

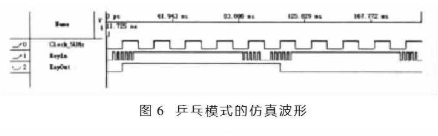

目前针对FPGA按键模式讨论的文章很少,因此本文专门探讨FPGA有哪几类按键模式?

2021-04-08 06:48:32

求大神分享一种高速突发模式误码测试仪的FPGA实现方案

2021-04-29 06:58:18

脉冲耦合神经网络(PCNN)在FPGA上的实现,实现数据分类功能,有报酬。QQ470345140.

2013-08-25 09:57:14

请问STM32怎么通过一个按键实现不同工作模式?stm32几种低功耗模式的实现和差别是什么?

2022-02-23 06:23:38

本文介绍了一种基于FPGA 技术的IDE 硬盘接口的设计。该卡提供两个符合ATA- 6 规范的接口,采用FPGA 实现了两套IDE 接口功能,设计支持PIO 和Ultra DMA 传输模式,文章侧重于介绍用FPGA 实现IDE

2009-07-22 15:58:08 0

0 基于FPGA 的嵌入式ASIP 软核设计与实现作者:李庆诚 任健 刘嘉欣 黄宝贞 来源:微计算机信息摘要:采用ASIP+FPGA 模式设计了一款嵌入式微处理器软核,以该软核为例从体系结构和

2010-02-06 10:44:40 30

30 PCI总线协议的FPGA实现及驱动设计

摘要! 采用FPGA技术! 在公司的flex6000系列芯片上实现了从设备模式pci总线的简化协议!并给出了WIndowsx 系统下的虚拟设备驱动程序

2010-03-12 14:30:27 36

36 本文介绍了一种基于FPGA技术的IDE硬盘接口的设计。该卡提供两个符合ATA-6规范的接口,采用FPGA实现了两套IDE接口功能,设计支持PIO和Ultra DMA传输模式,文章侧重于介绍用FPGA实现IDE接

2010-08-09 15:11:32 22

22 为了实时获取生产线上大量按键并发动作状态,提出一种基于FPGA的多按键状态识别系统设计。该系统设计采用VHDL语言描述,有效地解决远距离、分散、多键并发状态识别问题,并减

2010-12-23 15:40:22 28

28 FPGA开发中按键消抖与单脉冲发生器电路

FPGA开发中常用到单脉冲发生器。一些文章介绍过产生单脉冲的电路,产生的单脉冲脉宽和相位都不能与时钟同步,只能用在

2009-12-31 10:36:52 2715

2715

Modem的分类和传输模式有哪些?

一般来说,根据Modem的形态和安装方式,可以大致可以分为以下四类: 外置式1、外置式Modem

2010-03-19 14:16:46 3330

3330 这里提出一种利用FPGA的I/0端口数多和可编程的特点,采用VHDL语言的多按键状态识别系统,实现识别60个按键自由操作,并简化MCU的控制信号。

2 系

2010-08-25 17:16:28 1025

1025

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法是: 将以乘积项结构方式构成逻辑行为的器件称为

2010-10-18 10:04:46 743

743 FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理

2011-09-08 17:50:27 1734

1734 下面我就说说两线式的多按键电路的设计与实现,键盘只需两根导线就搞定,前提是你的单片机系统要有多余的一根AD口线

2011-09-29 17:43:55 11790

11790

采用了VHDL语言编程的设计方法,通过FPGA来实现按键消抖的硬件电路。论述了基于计数器、RS触发器和状态机3种方法来实现按键消抖电路,并给出仿真结果。通过下载到CycloneEP1C6T144芯片

2011-12-05 14:13:34 223

223 FPGA 有两种运行模式,即下载模式和烧写模式。下载模式是在上电的情况下通过 JTAG 接口直接把程序( Altera 平台下是.sof文件,SRAM Object File)下载到FPGA中。因为FPGA是基于SRAM结构的,因

2012-05-12 13:17:29 2341

2341 矩阵键盘实现按键显示源程序。

2015-12-23 14:20:08 29

29 Xilinx FPGA工程例子源码:实现在Sparton-3E板卡上的按键及开关的控制

2016-06-07 15:07:45 8

8 本文主要介绍了fpga按键控制数码管显示程序设计。数码管是由多个发光二极管封装在一起组成“8”字型的器件,引线已在内部连接完成,只需引出它们的各个笔划,公共电极。下面我们来了解一下按键控制数码管显示是怎么实现的。

2018-01-16 16:19:41 16280

16280

针对现有的基于模式的序列分类算法对于生物序列存在分类精度不理想、模型训练时间长的问题,提出密度感知模式,并设计了基于密度感知模式的生物序列分类算法-BSC。首先,在生物序列中挖掘具有密度感知的频繁

2018-03-29 13:54:14 0

0 本演示介绍了 Spartan®-3A 入门套件如何让您立即获得 Spartan-3A FPGA 器件的节能模式,高速 I/O 选项,DDR2 SDRAM 存储器接口,商用闪存配置支持,以及利用 Device DNA 实现的 FPGA/IP 保护等特性。

2018-05-22 13:45:01 2484

2484 asean的 FPGA DIY 按键控制LED显示的视频

2018-06-20 14:06:00 6721

6721

按键读取信号视频——FPGA。

2018-06-20 01:20:00 3919

3919

十八笔画的 FPGA_DIY 按键控制数码管。

2018-06-20 02:30:00 5606

5606

asean的 FPGA DIY 按键控制数码管显示的视频

2018-06-20 00:37:00 7441

7441 本文是基于FPGA实现Cordic算法的设计与验证,使用Verilog HDL设计,初步可实现正弦、余弦、反正切函数的实现。将复杂的运算转化成FPGA擅长的加减法和乘法,而乘法运算可以用移位运算代替

2018-07-03 10:18:00 2349

2349

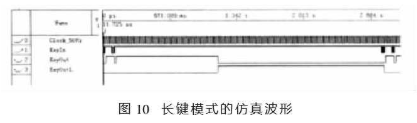

关键词:FPGA , 按键检测 八、 仿真分析 由上图仿真结果可知,当有按键按下时,需要较长一段时间后,Key_Flag会有一个高电平脉冲,同时Key_Value更新为输入按键的反码。 为了确定

2018-09-26 07:31:01 272

272 关键词:FPGA , 按键检测 几乎没有哪一个系统没有输入输出设备,大到显示器,小到led灯,轻触按键。作为一个系统,要想稳定的工作,输入输出设备的性能占了很重要的角色。本实验,小梅哥就通过一个独立

2018-09-26 07:40:01 459

459 实现按键控制 LED 亮灭。通过这个实验,掌握采用 Verilog HDL 语言编程实现按键控制 LED 亮灭及按键消抖方法

2019-06-11 16:50:06 13

13 按键开关主要是指轻触式按键开关,也称之为轻触开关。使用时以满足操作力的条件向开关操作方向施压开关功能闭合接通,当撤销压力时开关即断开,其内部结构是靠金属弹片受力变化来实现通断的。主要由嵌件、基座、弹片、按钮、盖板组成。

2019-09-06 10:35:45 9401

9401 的手动弹奏和自动演奏功能。本系统主要由音频发生模块,键盘控制模块和存储器模块组成。选择手动弹奏模式按键时,按下音符键后就会选通相应的频率输出;选择自动演奏模式按键时,储存器会将编写好的音乐信息依次取出,去选通各个对应的频率输出,实现自动演奏。音频发生器由分频器来实

2020-07-24 16:51:00 18

18 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 按键是FPGA设计当中最常用也是最简单的外设,本章通过按键检测实验,检测开发板的按键功能是否正常,并了解硬件描述语言和FPGA的具体关系,学习Vivado RTL ANALYSIS的使用。

2021-01-25 08:27:38 5

5 所有现代FPGA的配置分为两类:基于SRAM的和基于非易失性的。其中,前者使用外部存储器来配置FPGA内的SRAM后者只配置一次。 Lattice和Actel的FPGA使用称为反熔丝的非易失性配置

2021-07-02 16:01:40 2781

2781

FPGA实现,按键控制,四个按键实现波形转换(三角波,正弦波,方波),频率可调,电压可调。

2023-08-07 11:47:04 3

3 51单片机键盘接口-独立按键和矩阵按键按键的分类键输入原理独立式键盘矩阵键盘消抖键码识别键盘程序按键的分类按键按照结构原理可分为两类:一类是触点式开关按键,如机械开关、导电橡胶开关等;一类是无触点

2021-11-12 12:36:01 13

13 STM32——不同的按键对应实现不同功能的灯闪烁功能介绍程序解读总结功能介绍本程序使用STM32F103VE板子实现功能:按键1:实现单个灯闪烁按键2:实现全部灯闪烁按键3:实现流水灯按键4:实现

2022-01-13 12:44:10 22

22 如何实现单片机用一个I/O采集多个按键信号

使用模数转换(ADC)的特点就可以实现单片机用一个I/O采集多个按键信号。

一、单片机的I/O口检测按键简说

我们知道,一般情况下单片机的一个I/O口作为

2022-02-11 14:23:22 11

11 典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2022-03-14 14:02:50 1366

1366 我有基于一个电极的非触摸程序,如何实现4个按键的手势组合?

通过4路波形判断手势

即使在在一一个手势中有许多不同的波形模式

软件开发困难

2022-05-27 11:01:46 892

892

这是FPGA之旅的第二个设计实例了,按键在项目中的作用是非常大的,使用的很频繁,本例将带大家设计一个实用的按键模块。

2022-09-05 09:19:20 1985

1985 尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2022-10-10 14:37:57 1272

1272 之前做过很多仿真仪表盒,经常遇到盒子上既有大量LED指示灯,又有很多按键的情况,主芯片使用的SiliconLabs的一款单片机,管脚资源有限,如何应对如此多的指示灯和按键呢?当时选用了max7219来实现多个LED灯的控制,而按键则是通过矩阵扫描实现的。

2023-03-27 14:05:30 4049

4049

) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。 在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射;主模式根据比特流的位宽又可以分为:串行模式( 单比特流) 和并行模式( 字节宽度比

2023-03-29 14:50:06 535

535 在电子产品中我们会经常用到按键,比如电脑的键盘,手机的按键等等,按键就是人机交互的一种工具。 本文使用 FPGA 程序来检测与按键对应的 I/O口的电平高低来判断按键是否按下或松开,通过点亮/点灭开发板上相应的 LED 灯来指示按键的动作。

2023-04-18 14:47:13 1537

1537

实现的任务就是用LCD做一个菜单,用按键控制不同的LED流转模式。

2023-07-26 16:53:50 450

450

通常的按键所用开关为机械弹性开关,当机械触点断开、闭合时,由于机械触点的弹性作用,一个按键开关在闭合时不会马上稳定地接通,在断开时也不会一下子断开。因而在闭合及断开的瞬间均伴随有一连串的抖动,为了不产生这种现象而作的措施就是按键消抖。

2023-09-05 10:43:10 631

631

FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,它可以通过编程实现各种数字电路功能。FPGA技术以其灵活性、高性能和低功耗等特点而受到广泛关注和应用。本文将介绍FPGA的基本原理、分类、特点以及应用领域。

2023-09-14 17:28:45 1789

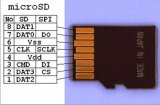

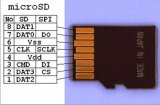

1789 在这篇文章,进入正题,说一说怎么通过FPGA采取SD模式来实现Micro SD 卡的驱动,也就是怎么去读写 Micro SD 卡。

2023-09-19 11:48:41 930

930

电子发烧友网站提供《基于FPGA的模式匹配系统设计.pdf》资料免费下载

2023-11-08 09:26:42 0

0 单片机的GPIO如何实现触摸按键的功能呢? 触摸按键是一种使用触摸电容技术实现的按键,它通过利用人体的电容来实现按键的检测和触发。在单片机中实现触摸按键功能需要使用特定的引脚和软件算法来进行

2023-12-07 11:43:10 2000

2000 STM32怎么实现按键开关机 STM32是一种嵌入式系统,可以编程实现按键功能,包括按键开关机。在本文章中,我将为你提供一个详实和细致的步骤,以帮助你实现STM32的按键开关机。 总结来说,实现

2023-12-07 15:17:44 1203

1203 单片机作为一种微处理器,在各种嵌入式系统中扮演着核心控制器的角色。其中,按键输入作为单片机控制中常见的交互方式,实现模式切换是常见的需求。本文将详细介绍如何在单片机中实现按键切换模式。 一、硬件准备

2023-12-13 11:07:19 993

993 单片机按键切换模式命令的原理、实现方法和应用场景。 一、原理与概述 单片机系统是由单片机芯片、外部器件和外围电路组成的一个完整的嵌入式系统。在系统设计中,为了使系统更加灵活、多样化,通常需要设计多种工作模式。通

2023-12-15 10:31:12 655

655

电子发烧友App

电子发烧友App

评论