对于2018年的5G网络来说,最重要的五大无线技术中的两个—多重输入多重输出(MIMO)和波束成形(beamforming)——对5G网络一直都非常重要。

2018-03-01 07:08:00 16316

16316

随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2015-02-02 17:32:52 2204

2204

,所以只进行SGMII和SerDes进行对比。 由于SerDes在PCIe部分起着非常重要的作用,所以这部分详细内容会放到PCI-e部分详解,这里只是简单介绍一下: SerDes,是

2020-10-09 11:31:29 29959

29959

在过去的几十年里,电子通信行业一直是 FPGA 市场增长背后的重要推动力,并将继续保持下去。这背后的一个主要原因是 FPGA 中内置了许多不同的高速接口,以支持各种通信标准/协议。实现这些标准所涉

2023-02-22 13:37:54 1151

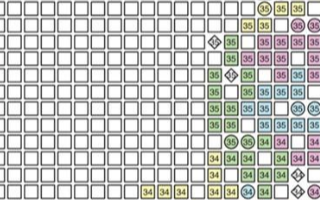

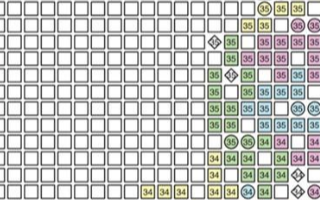

1151 在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

2023-11-21 15:03:06 548

548

的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

2019-10-23 07:16:35

FPGA 管脚分配需要考虑的因素FPGA 管脚分配需要考虑的因素 在芯片的研发环节,FPGA 验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好

2012-08-11 10:27:54

求FPGA内部资源{:soso_e100:}相关资料,发lishenghhuc@126.com,谢谢

2012-09-27 16:55:44

)是两种不同的硬件实现方式。

FPGA是一种可编程逻辑器件,其内部资源可以根据需要进行配置和重新配置。这些资源包括但不限于:

逻辑单元(Logic Cells):这些是FPGA的核心计算资源,可以实现各种

2024-02-22 09:52:22

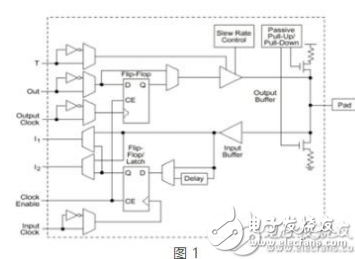

,实际上每一个系列的FPGA都有其相应的内部结构),FPGA芯片主 要由6部分完成,分别为:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌

2017-05-09 15:10:02

了 100 GFLOPS。在所有信号处理算法中,对于只需要动态范围浮点算法的很多高性能 DSP应用,这是非常重要的优点。选择 FPGA并结合浮点工具和 IP,设计人员能够灵活的处理定点数据宽度、浮点数据精度和达到的性能等级,而这是处理器体系结构所无法实现的。

2019-08-13 06:42:48

FPGA为了简化BOM成本(如安路半导体)不需要用户特别关注上电时序,用单电源供电,芯片内部控制上电时序。虽然不合理的上电时序有时候也能让FPGA正常工作,但不正常的上电或掉电过程有可能会造成瞬时电流

2019-07-18 14:26:01

等都属于SRAM结构)的上电时间会比FLASH结构的(Microm,Actel等)上电时间要长。有些国产FPGA为了简化BOM成本(如安路半导体)不需要用户特别关注上电时序,用单电源供电,芯片内部控制

2023-11-03 11:08:33

FPGA验证是其中的重要的组成部分,如何有效的利用FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑

2024-01-10 22:40:14

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用 FPGA 的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从

2017-03-25 18:46:25

II、Vivado等)、仿真软件(ModelSim等)的使用5、熟悉FPGA设计流程(仿真,综合,布局布线,时序分析)。6、熟练掌握资源估算(特别是slice,lut,ram等资源的估算)。7、同步

2020-10-22 17:08:15

实现规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加

2021-07-04 14:16:15

规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富

2021-07-25 11:09:06

规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富

2021-07-26 14:47:48

规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富

2021-11-22 10:04:03

实现规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加

2021-07-09 14:24:42

规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富

2021-07-09 14:34:18

规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富

2021-08-10 14:51:33

规模较大、频率较高、寄存器较多的设计。使用FPGA/CPLD设计时,应该对芯片内部的各种底层硬件资源,和可用的设计资源有一个较深刻的认识。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富

2020-08-02 10:45:07

高速收发器(SERDES)的运用范围十分广泛,包括通讯、计算机、工业和储存,以及必须在芯片与芯片/模块之间、或在背板/电缆上传输大量数据的系统。但普通高速收发器的并行总线设计已无法满足现在的要求。将收发器整合在FPGA中,成为解决这一问题的选择办法。FPGA高速收发器设计时,我们需要注意哪些事项呢?

2019-08-07 06:26:42

亲爱的Xilinx论坛,我正在实现基于SERDES协议的序列化传输。我需要在Kintex7上接收8个差分对,这些差分对承载由另一个Kintex7串行化的64位字,主时钟为100MHz。将托管FPGA

2020-03-17 09:53:11

的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。 本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8

2019-05-29 17:52:03

用户在产品选型和方案设计之初,对于硬件接口资源分配不熟悉,不遵守芯片规范使用导致项目出现问题,造成了严重损失。本期我们就此系列平台的SerDes资源分配做一篇文章。LS系列产品的资源不可为不丰富,其中最让人头晕的当属于SerDes协议。百度百科这样解释,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

2021-07-28 07:02:12

,Excel被提升到了非常重要的地位,除了OLAP前端外,Excel还充当起SSAS中的DM和未来PPS的客户端软件。再加上MOSS,Excel成为了集分析、报表、发布为一体的BI客户端工具。

2019-07-11 07:17:16

你好。我正在写一篇技术论文和需要知道LUT和Kintex 7 FPGA芯片中的FF所需的资源。资源可以是晶体管数量,栅极数,芯片面积大小等等。我在一个网站上听说LUT需要2.5倍的“FPGA门”,但

2019-02-27 13:49:58

什么是STM32?STM32F103ZET6芯片的内部资源有哪些?

2021-08-16 06:09:19

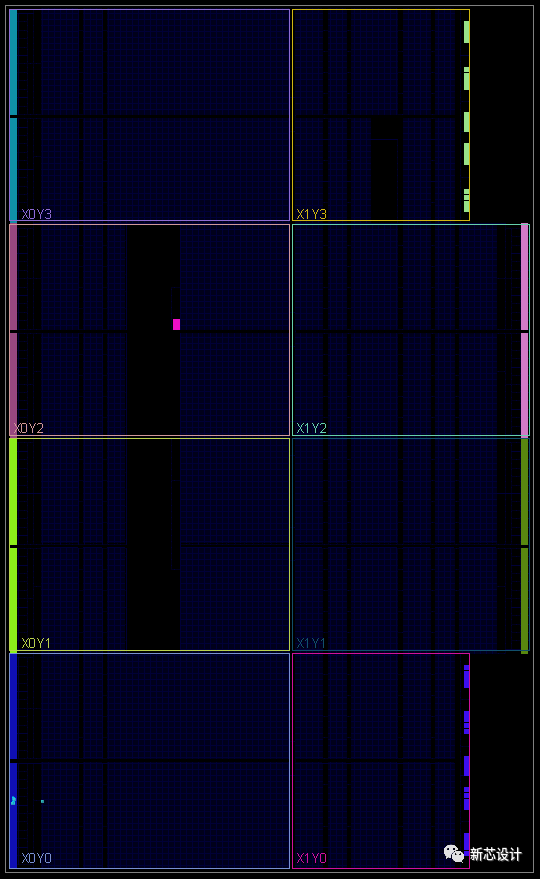

很多人开始学FPGA,就是拿着开发板就开始写verilog,但对FPGA内部怎么构成的却没有概念。我们在做FPGA选型的时候,通常需要考虑FPGA有多少资源,你有没有想过你关注的这些资源,在芯片

2020-03-24 19:26:04

cpld fpga设计时要注意的规范cpld ,fpga 设计时大家要注意coding 规范 cpld ,fpga 设计时大家要注意coding 规范,的确很重要工作过的朋友肯定知道,公司里是很强

2012-08-10 18:51:22

⑴ 结合Xilinx、Altera 等公司的FPGA 芯片,简要罗列一下FPGA 内部的资源或专用模块,并简要说明这些资源的一些作用或用途。(至少列出5 项,越多越好)⑵ 如果,对内部特定资源,曾有

2012-03-08 11:03:49

首先回忆一下power 组成power组成由dynamic power和leakage power组成。leakage power是指的电路在没有跳变时所产生的功耗。dynamic po...

2021-07-29 08:04:49

MOSFET的安全工作区为什么SOA对于热插拔应用非常重要?

2021-03-08 07:49:01

掐头去尾只取中间1秒的。那么根据公式,采样率(fs)的高低,只取决于采集内存(L)的大小。这就是为什么我们要特别关心这个非常低调的参数。采集内存这个参数,恰如数码相机的像素,其性能的扩展,并不仅仅是缓存器件

2019-12-13 10:46:50

很好的应用笔记,用于在spartan fpgas中实现serdes但是对Virtex5没什么用?任何人都可以指出我使用V5 fpgas正确实现serdes(lvds)的一些资源。我将从主设备向10个从

2020-07-13 15:54:49

(吸尘器)。除了支持高电流消耗,内部电池组电路需要实现超低功耗,以延长电池寿命和整体运行时间。这就是bq77905 6μA的平均电流消耗的方便之处。工业消费应用通常包括3S(小型电动工具或无人机),4S

2019-08-01 04:45:02

QuartusII ,或ISE 就可以了,这两个基本是相通的,会了哪一个,另外的那个也就很Easy了。功能仿真建议使用Modelsim ,如果你是做芯片的,就可以学学别的仿真工具,做FPGA的,Modelsim

2024-02-22 10:57:13

器件中的重要创新之一,2D NoC 为 FPGA 设计提供了几项重要优势,包括:· 提高设计的性能,让 FPGA 内部的数据传输不再成为瓶颈。· 节省 FPGA 可编程逻辑资源,简化逻辑设计,由

2020-09-07 15:25:33

我们特别加以关注,它们是:电路板表面材料,射频/微波设计和射频传输线。PCB材料PCB一般由叠层组成,这些叠层可能用纤维增强型环氧树脂(FR4)、聚酰亚胺或罗杰斯(Rogers)材料或其它层压材料制造

2018-09-20 10:28:25

传经授道。他们将就一系列大家非常关心的关键设计问题发表他们的独到见解,包括:什么是目前FPGA应用工程师面对的最主要设计问题?如何解决?当开始一个新的FPGA设计时,你们会推荐客户采用什么样的流程?对于I/O

2012-02-27 15:18:09

因为Android兼容性,不同手机会有不同的bug出来, 而且很难复现,因此一个好的捕获错误机制对debug来说是非常重要的。

2019-07-11 07:16:26

生成的时钟计时的路径”,如果是这种情况,DDR SerDes的情况下的偏移约束有什么用处。我可以理解逻辑,因为DDR时钟仅在专用内部线路上运行到该组的IOB块,因此已经优化并且非常静态。3)我们所有

2019-08-09 09:54:33

用户特别关注上电时序,用单电源供电,芯片内部控制上电时序。虽然不合理的上电时序有时候也能让FPGA正常工作,但不正常的上电或掉电过程有可能会造成瞬时电流过大,无法保证上电期间FPGAIO为三态,甚至损坏芯片

2020-12-23 17:44:23

Verilog等硬件语言描述更加容易。当进行嵌入式系统设计时,绝大部份的设计时间可能花费在除错阶段,因此缩短发现问题并解决问题的时间非常重要。作为一款整合除错器,Computex公司的F-Sight同时具备

2019-09-17 07:42:45

在做射频的时候,选择电感电容时特别关注他们的Q值,那什么是Q值呢?Q值是什么意思,它为什么重要?

2021-03-11 07:57:31

主要用于原型IC系统.当设计完成后,设计人员可以将逻辑转换为以更高速度工作的硬连接线IC.为了能正常工作,FPGA必须采用适当的电源管理技术. FPGA有哪些供电要求? FPGA的电源取决于内部电路

2012-04-28 15:05:10

,比如时钟域、模块复用、约束、面积、速度等问题,在系统上模块的优化最为重要。比如FPGA一般触发器资源丰富,CPLD的组合逻辑资源更加丰富。FPGA/CPLD一般是由底层可编程硬件单元、BRAM、布线资源

2020-09-18 10:32:44

其他因素。发烧友做的相位补偿技术以及热效应的影响都要考虑在内。ADC输入端的开关信号带来的影响也是放大器电路需要当心的问题。优化所有的这些问题会是个棘手的事情。当然,仿真运放工作时,压摆率在二阶系统中的影响也很重要。

2018-09-20 16:32:36

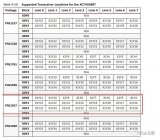

Xilinx 的 CPLD 和 Altera 的 FPGA ,其速度等级的数值越大,反而代表芯片性能越差 温度等级: 4.价格 在芯片选型时,价格也是特别重要的一个因素,毕竟不同芯片的价格可能相差数倍至数十倍、数百倍。应该在满足要求的芯片中,挑选性价比最高的一款。

2020-12-23 17:21:03

怎么通过VDD脚看芯片是内部供电还是外部供电求通俗易懂的解释

2022-12-07 14:27:21

傻瓜式嵌入式机器学习设计-ARM特别版,展示了往任何设备添加机器学习不仅是可能的而且非常简单。本书重点关注关键实现点并解释为什么在计划的早期这些点非常重要。这本书解释了怎样实现平台配置并解释了为什么软件重要。最后,阐述了生态系统在机器学习中的重要性,且给出了在网络边缘使用机器学习的有趣例子。

2021-12-20 08:00:19

为 EMI 敏感和高速 SERDES 系统供电

2019-05-21 14:34:36

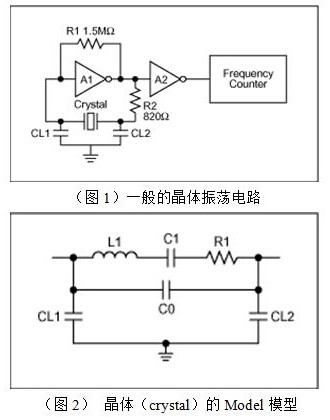

关于时钟时钟对于一款芯片非常重要,其作用相当于人的心脏,人只有在心率正常稳定的情况下才能健康生活,同样的,芯片只有工作在合法正常的时钟频率下才能保证程序得到正常的运行。本章就将从时钟树开始分析

2021-08-02 06:16:49

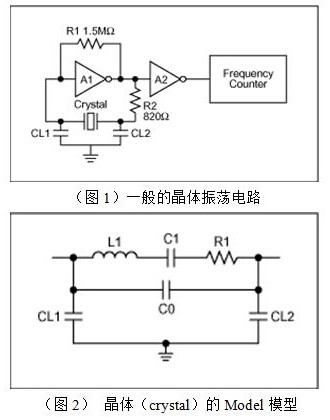

计算机系统中起着非常重要的作用,是保证系统正常工作的基础。在一个单片机应用系统中,时钟有两方面的含义:一是指为保障系统正常工作的基准振荡定时信号,主要由晶振和外围电路组成,晶振频率的大小决定了单片机

2012-11-28 21:53:41

1.电缆比较。电磁兼容性(EMC)对车辆安全性非常重要。电缆组件必须通过严格的EMC测试。双绞电缆由仔细的双绞线组成,以确保耦合和辐射的电磁场消除。图2.潜在的UTP EMC问题。在理想条件下,受控扭转

2017-04-26 11:53:02

无线电通信、广播、电视、雷达、导航、电子对抗、遥感、射电天文等工程系统,凡是利用电磁波来传递信息的,都依靠天线来进行工作,由此可见天线的重要性。因此,选择能完全满足系统性能指标的天线是非常重要

2019-07-17 06:19:37

为什么功率控制在CDMA系统中非常重要?

前面提到,CDMA系统的功率控制尤为重要,功率控制被认为是所有CDMA关键技术核心。要解释功率控制的重要

2009-06-01 20:26:25 1156

1156 本文简要的分析FPGA芯片中丰富的布线资源 。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。

2012-12-17 17:28:41 3491

3491 FPGA SERDES的应用需要考虑到板级硬件,SERDES参数和使用,应用协议等方面。由于这种复杂性,SERDES的调试工作对很多工程师来说是一个挑战。

2013-03-15 14:55:13 10360

10360

本文重点分析芯片内部不同硬件资源对于SEU效应敏感性的问题。以SRAM型FPGA为研究对象,设计进行了两种颗粒度不同的故障注入实验。结果表明,在FPGA内部资源中,Slice资源对于SEU效应

2017-11-16 19:58:01 3058

3058

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

2017-11-28 14:41:06 14538

14538

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别。第一类

2017-12-05 11:48:44 8

8 王志勤表示,5G中频是5G解决覆盖和容量问题的非常重要的一个核心频段,所以我国中频段频率使用规划的率先发布对中国乃至全球5G发展都起到了一个重要的引导作用。

2017-12-28 09:43:44 21336

21336 在使用FPGA过程中,通常需要对资源做出评估,下面简单谈谈如何评估FPGA的资源。

2019-02-15 15:09:05 3580

3580 谈及如火如荼的中国市场,张至伟指出,中国市场一直是爱立信在全球非常重要的一个市场,我们对中国市场的重视不言而喻,例如在中国大量的资源投入,包括从研发到生产,再到安装再到服务等等;甚至现在爱立信更多是把研发力量向中国转移,贴近本地客户需求快速反应。

2019-02-25 10:09:53 762

762 在本周举行的“爱立信MWC 2019预分享会上”,爱立信东北亚区首席市场官张至伟在接受C114专访时表示,5G的成功在中国有非常重要的土壤,我们会在这里植根,争取越做越好!

2019-02-26 15:16:24 2556

2556 本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-05-24 15:33:25 4073

4073

管脚是FPGA重要的资源之一,FPGA的管脚分别包括,电源管脚,普通I/O,配置管脚,时钟专用输入管脚GCLK等。

2019-06-28 14:34:07 3703

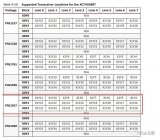

3703 带温度补偿RTC芯片的需求正在不断增加,其应用涉及电表、工业、通信等带有部分嵌入式付费系统的设备、全球卫星导航接收机及其他行业应用。准确计时取决于几个重要参数,当然其他参数也会影响时间计时精度,但初始精度、长期稳定性、温度系数这3个参数是最终用户需要特别关注的指标。

2020-02-27 09:30:40 10911

10911

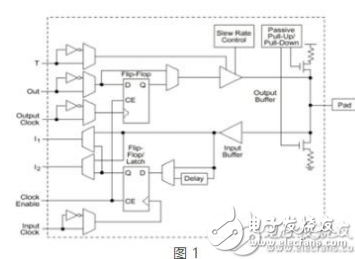

虽然很多 FPGA 工程师都是写代码,但是作为硬件编程工程师,如果不熟悉 FPGA 的底层资源和架构,是很难写出高质量的代码——至少很难写出复杂逻辑的高质量代码,也很难站在系统的层面去考虑芯片的选型等问题。那熟悉 FPGA 架构,首先最主要的一点,我们先来了解 FPGA 的 IO。

2020-07-16 17:53:02 9031

9031

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

2020-09-02 09:20:21 12353

12353

更进一步,在芯片制造过程中依然需要EDA软件的辅助,在芯片的良率分析、加工工艺仿真等环节,EDA软件依然起到了非常关键的作用。

2020-09-23 16:30:26 79188

79188 因为摄像头输出的LVDS信号速率会达到600Mbps,我们将不能够通过FPGA的I/O接口直接去读取这么高速率的信号。因此,需要使用Xilinx FPGA内的SerDes去实现高速数据的串并转换。

2020-12-30 17:24:00 39

39 本文档的主要内容详细介绍的是Xilinx 7 系列FPGA中的Serdes总结。

2020-12-31 17:30:58 25

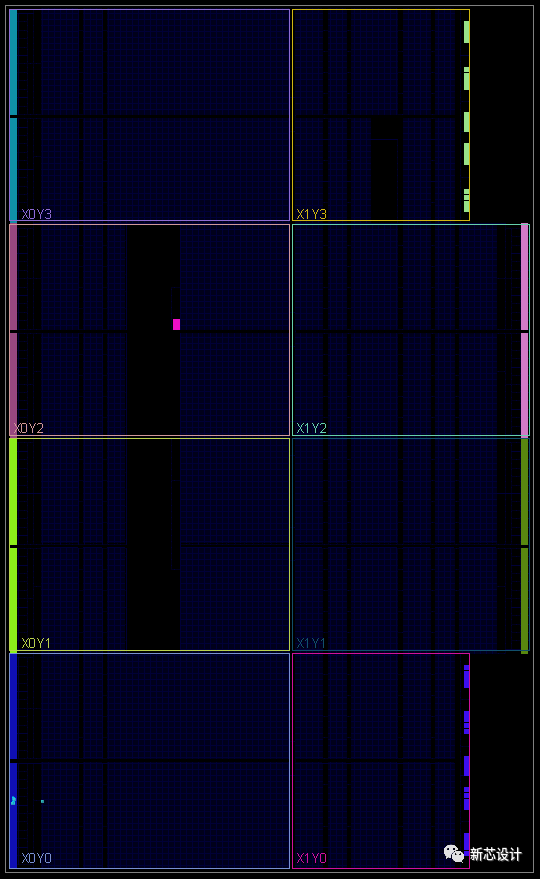

25 DDR3。 2.FPGA架构设计问题 我们知道,FPGA片上分布着各种资源,如时钟,serdes,RAM,LUT,IO等。在进行FPGA规划时候,应当需要知道项目设计需求,以及需求各模块之间的数据交织情况,这样可以避免

2021-01-07 10:15:31 4645

4645

利用 FPGA 实现大型设计时,可能需要FPGA 具有以多个时钟运行的多重数据通路,这种多时钟FPGA 设计必须特别小心,需要注意最大时钟速率、抖动、最大时钟数、异步时钟设计和时钟/数据关系。设计过程中最重要的一步是确定要用多少个不同的时钟,以及如何进行布线,本文将对这些设计策略深入阐述。

2021-01-13 17:00:00 11

11 为 EMI 敏感和高速 SERDES 系统供电

2021-03-19 04:23:54 12

12 FPGA芯片本身就具有可以反复擦写的特性,允许FPGA开发者编写不同的代码进行重复编程,而FPGA可重构技术正是在这个特性之上,采用分时复用的模式让不同任务功能的Bitstream文件使用FPGA芯片内部的各种逻辑资源

2022-04-26 10:38:54 2872

2872 FPGA芯片实现V-by-One的收发,同时例化V-by-One 及SerDes IP即可实现V-by-One通信。由于SerDes和V-by-One是分开的,所以频率可在要求范围内灵活调整, 同时FPGA内部还可以进行OSD叠加等处理并控制其他外设,从而充分利用FPGA资源。

2022-11-18 11:02:36 1459

1459 和FieldComm Group标准框架下共同努力,使以太网APL能够跨工业以太网协议使用,并加速其部署。 以太网APL为何非常重要?以太网APL将通过实现高带宽,以及与现

2023-06-01 03:10:02 447

447

通信电源系统故障造成通信设备供电中断,通信设备无法运行,将造成通信电路中断,通信系统瘫痪,造成重大的经济和社会效益损失。因此,通信电源系统在通信系统中占有非常重要的

2023-03-23 11:25:03 540

540

Resource:两片FPGA通过X12 gth互联;每片FPGA使用48路serdes走光口与板外连接;

2023-06-20 09:10:23 621

621

松野博一表示:“个别投资的判断由jic来做。该事业是产业竞争力的核心——尖端半导体开发和生产能力的核心——半导体材料的核心,因此,为了加强产业竞争力,结构改革和事业重组非常重要。”

2023-06-28 11:17:50 293

293 FPGA 芯片架构是非常重要的,如果你不了解 FPGA 芯片内部的详细架构。

2023-07-04 14:36:07 811

811

的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。 本方案是以CME的低功耗系列FPGA的HR03为平台,实现

2023-07-27 16:10:01 1565

1565

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO

2023-10-16 14:50:37 558

558

。FPGA 的性能和功能主要由内部的晶振频率决定。因此,在 FPGA 设计中,选择合适的晶振非常重要。 晶振的作用是为 FPGA 提供一个稳定的时钟信号。FPGA 的内部逻辑由时钟信号驱动,如果时钟信号不稳定,就会导致 FPGA 内部逻辑错误,从而影响其性能和正确性。因此,选择合适的晶振频率至关重要。 晶

2023-10-18 15:28:37 1732

1732 尽管设计和验证很复杂,SERDES 已成为 SoC 模块不可或缺的一部分。随着 SERDES IP 模块现已推出,它有助于缓解任何成本、风险和上市时间问题。

2023-10-23 14:44:59 449

449

中,时钟是很重要的一个因素,而时钟配置芯片则是为了提供时钟信号而存在。 时钟是FPGA中非常重要的因素,因为FPGA必须在时钟边沿上完成一次操作。时钟信号决定了FPGA内部计算和通讯的速度,因此时钟信号的稳定性和精度至关重要。 FPGA实现时钟同步通常有两种方式:一种是通过外部时钟输入

2023-10-25 15:14:20 1045

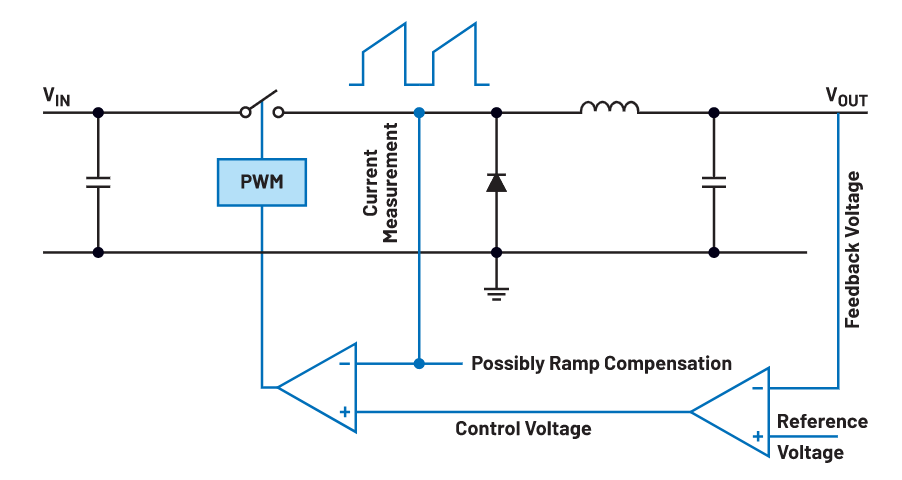

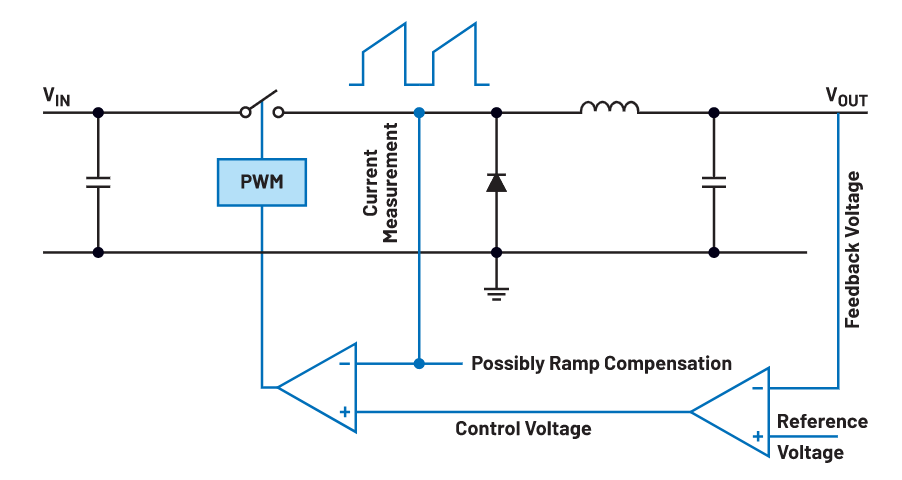

1045 为何在开关稳压器中,电流模式控制非常重要?

2023-11-30 17:31:21 199

199

在AI发展下,服务器的选择非常重要。以下是一些选择服务器时需要考虑的因素。

2023-12-07 10:06:43 187

187

电子发烧友App

电子发烧友App

评论