USB 3.0的传输编码方式与USB 2.0有所不同,从USB 3.0规范中我们了解到,USB 3.0采用的是8b/10b编码方式

2011-11-22 16:22:57 8333

8333

为了在USB 3.0中实现数据的8 b/10 b编解码,把8b/10b编解码分解成5 b/6 b编解码和3 b/4 b编解码,然后在FPGA上实现了具体的硬件电路。

2011-11-30 11:38:18 2803

2803

Modbus是一种串行通信协议,是Modicon公司(现在的施耐德电气 Schneider Electric)于1979年为使用可编程逻辑控制器(PLC)通信而发表。Modbus已经成为工业领域

2022-09-02 10:58:37 1099

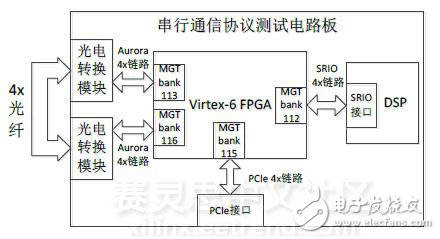

1099 无线电系统,基带信号处理,无线仿真平台,高速图像采集、处理等。支持热插拔,设计芯片可以满足工业级要求。 2、处理板技术指标SRIO 4X交换网络连接两片DSP以及两片Virtex-6 FPGASRIO

2015-05-19 17:34:31

4X交换网络连接两片DSP以及两片Virtex-6 FPGASRIO 4X交换网络连接4组SRIO 4X至VPX P1;具备一个SRIO 4X交换芯片;具备高速RocketIO数据传输链路;具备

2014-05-30 11:36:40

UD PCIe-402全国产化信号处理模块为标准PCIe全高半长的结构,对外支持PCIe2.0×8通信,也可以采用千兆以太网接口进行通信,模块为100%国产化设计。FPGA芯片选用国产

2023-05-09 20:07:51

协议不仅充当通信媒介,还为物联网网络提供增值功能。诸如Zigbee之类的物联网协议实现了无干扰,低功耗的通信,而像Profinet这样的开源协议可以促进与各种工业单元和设备的无缝和快速通信。 本文介绍了8种物联网通信协议,这些协议已广泛部署在众多现有和新兴的物联网应用中。

2020-12-24 06:13:35

8b/10b编码用的控制字是K28.5,但是解码时用非K28.5的控制字能把数据解码出来吗?

2019-01-02 14:47:15

小弟最近在调用Aurora 8b/10b IP模块时,在用modelsim功能仿真时,一切正常。 但是直接使用了例化后的example,并将Tx和Rx形成了回路下到FPGA板子上

2015-03-09 10:58:03

使用ISE 14.1,我试图在Virtex-4 FX中生成一个简单的Aurora 8B / 10B内核。核心似乎生成(生成完整的.vhd函数模型文件),但不会在.vho文件中生成任何代码以实例化到我

2019-03-20 15:43:41

我开发了一个应用程序,包括Userapp,Aurora IP 8b10b v8.3,两个FIFO(Tx和Rx)和sram模块。我使用ISim模拟了总应用程序。我得到了所需的结果。现在,我的疑问

2020-03-30 08:49:04

(Virtex-5)或19.2Gbps(Virtex-6)2. 高速LVDS数据发送:训练序列产生,数据成帧,8B/10B编码,数据并行转串行,随路时钟产生等3. 高速LVDS数据接收:接收时钟检测(检测接收时钟

2012-05-21 09:32:15

Virtex-6 FPGA主要特性有哪些?

2021-05-25 06:31:24

你好。如今,我设计了使用Virtex-6的主板。我想知道Virtex-6是否有专用的PLL输出引脚(clkout引脚)。我检查了Virtex-6系列概述Virtex-6 FPGA时钟资源用户指南

2020-06-12 10:05:21

嗨,XilinxIDF站点表明IDF仅支持Virtex-4,Virtex-5,Spartan-6和7系列FPGA。我可以在Xilinx Virtex-6 FPGA上使用IDF吗?有没有人尝试过使用IDF和Virtex-6 FPGA?谢谢,季米特里斯

2020-07-08 15:56:53

三种常见嵌入式设备通信协议是什么?

2021-12-23 08:17:02

串行总线协议PCIe、ASI和sRIO之间有什么不同?

2021-05-25 07:05:09

通信协议是指什么?串行通信和并行通信的优缺点分别有哪些?串行通信的通信方式有哪几种?

2021-12-10 06:36:27

嵌入式通信协议:分为“大协议”和“小协议”两种“大协议”:主要用来进行系统外的整个系统之间的通信,协议如Ethernet、USB、SATA、PCIe等,传输速率在数百甚至上千MB/s。 “小协议

2021-12-24 08:15:01

ADM3053数据手册上说明芯片符合ISO 118981标准,请问该芯片是否可以同时支持CAN 2.0A 和 CAN 2.0B?

2024-01-05 06:24:05

之间传输单独的RGB颜色、音频数据和辅助数据。视频传输格式采用TMDS编码,二进制数据采用8b/10b算法编码。 HDMI 2.0规范允许TMDS比特率高达6gbps,TMDS时钟率为TMDS比特率

2020-04-26 15:51:14

一.CAN简介CAN是ControllerArea Network的缩写(以下称为CAN),是ISO国际标准化的串行通信协议。在当前的汽车产业中,出于对安全性、舒适性、方便性、低公害、低成本的要求

2021-08-19 08:44:19

你好, 我正在使用Aurora 8B / 10B v5.3 IP内核,Virtex 5 FPGA用于使用SFP电缆的GB收发器。我使用核心生成器创建了IP核,获得了示例设计(所有文件)。我模拟了示例

2020-04-07 14:52:25

Express(PCIe)是一种高速串行总线标准,用于在计算机内部传输数据。FPGA可以通过实现PCIe协议来支持高速数据传输和通信。USB协议:USB是一种通用的串行总线标准,用于连接计算机

2023-03-27 09:01:46

HDMI1.4b/2.0的测试难点是什么?FRL模式如何实现带宽的增加?怎么解决源端测试的难点?

2021-06-17 11:15:23

I2C通信协议I2C通信原理I2C通信原理:I2C是一种半双工通信方式,主要时钟线SCL和数据线SDA构成,速率一般为400Mbps总线信号有三种:开始信号;结束信号;应答信号当时钟线SCL和数

2022-02-17 07:16:28

主要目的是扩展 IMX8MM 上的串口数量。

为此,选择了 PCI Express 2.0 串行端口。

主要问题是我收到以下消息:

[2.184834]imx6q-pcie

2023-04-28 07:36:10

,SPI,UART,RS-232,Audio(I2S,LJ,RJ,TDM),CAN,LIN,FlexRay,MIL-STD-1553,SATA,PCIe,8b/1b,USB2.0等总线触发和解码l 支持

2021-07-01 10:52:45

QC2.0协议,并且QC2.0分为A级和B级两种行业标准。A标准:5V、9V、12V输出电压;B标准:5V、9V、12V、20V输出电压。现在大部分支持快充的手机基本上都是QC2.0A标准,QC2.0充...

2021-07-27 06:08:27

的逻辑1或逻辑0有多个位没有变化时,信号的转换就会因为电压位阶的关系而造成信号错误。直流平衡的最大好处便是可以克服以上问题。8B/10B编码是目前许多高速串行总线采用的一种编码机制,如1394b

2018-12-11 11:04:22

RocketIO高速串行接口本人在北京工作6年以上,从事FPGA外围接口设计,熟练使用Virtex-5/Virtex-6 FPGA,非常熟悉RocketIO GTP/GTX协议,Aurora协议

2014-03-01 18:46:35

请让我知道SRCC,VIRTEX-6的MRCC可以计时的频率。以上来自于谷歌翻译以下为原文 Please let me know upto what frequency can SRCC,MRCC of VIRTEX-6 can be clocked.

2019-02-13 10:52:04

通道上最大记录长度为 32 M样点- 在所有四条通道上实时取样速率为 20 GS/s- 高达 3.125 Gb/s的串行码流触发功能,支持 8b/10b 协议触发 - 串行数据分析和一致性测试,提供 Windows XP操作系统的内置联网- 速率可达 6.25 Gb/s 及更高 OpenChoice?软件

2022-03-09 14:51:57

USART串行通信协议STM32 USART串口介绍USART配置流程

2020-12-18 06:34:17

Xilinx Virtex-6系列选型1 Xilinx公司Virtex-6 FPGA共有3个系列:Virtex-6 LXT – 高逻辑密度,高速串行收发器,高密度IOVirtex-6 HXT – 高

2012-02-28 14:56:59

imx6q 开发板, 使用forlinx.com 上对应的内核linux 4.1.15-2018.10.23, uboot-2016.03-r0, 插入pcie2.0的卡开机后,dmesg报错

2022-01-10 07:23:12

3.125 Gb/s的串行码流触发功能,支持 8b/10b 协议触发串行数据分析和一致性测试,速率可达 6.25 Gb/s 及更高 OpenChoice®软件,· 提供 Windows XP操作系统

2020-11-10 11:20:30

我们首先要了解的信息有以下五点:1、充电机和BMS之间通信网络采用CAN2.0B通讯协议。2、在充电过程中,充电机和BMS监测电压、电流和温度等参数,同时BMS管理整个充电过程。3、充电机和BMS

2021-09-14 06:07:38

嗨,我想知道Virtex-6 FPGA可以预期多少时钟抖动。我已经阅读了有关Virtex-6 FPGA的所有文档,但没有找到数值。我发现的唯一的事情是它具有低抖动但不低或数值。

2020-06-12 14:56:20

UART、 I2C 和 SPI 是单片机系统中最常用的三种通信协议。1、初步介绍SPI 是一种高速的、全双工、同步通信总线,标准的 SPI 也仅仅使用 4 个引脚,常用于单片机和 EEPROM

2021-11-18 09:22:58

单片机系统中最常用的三种通信协议是什么?

2022-02-17 06:03:46

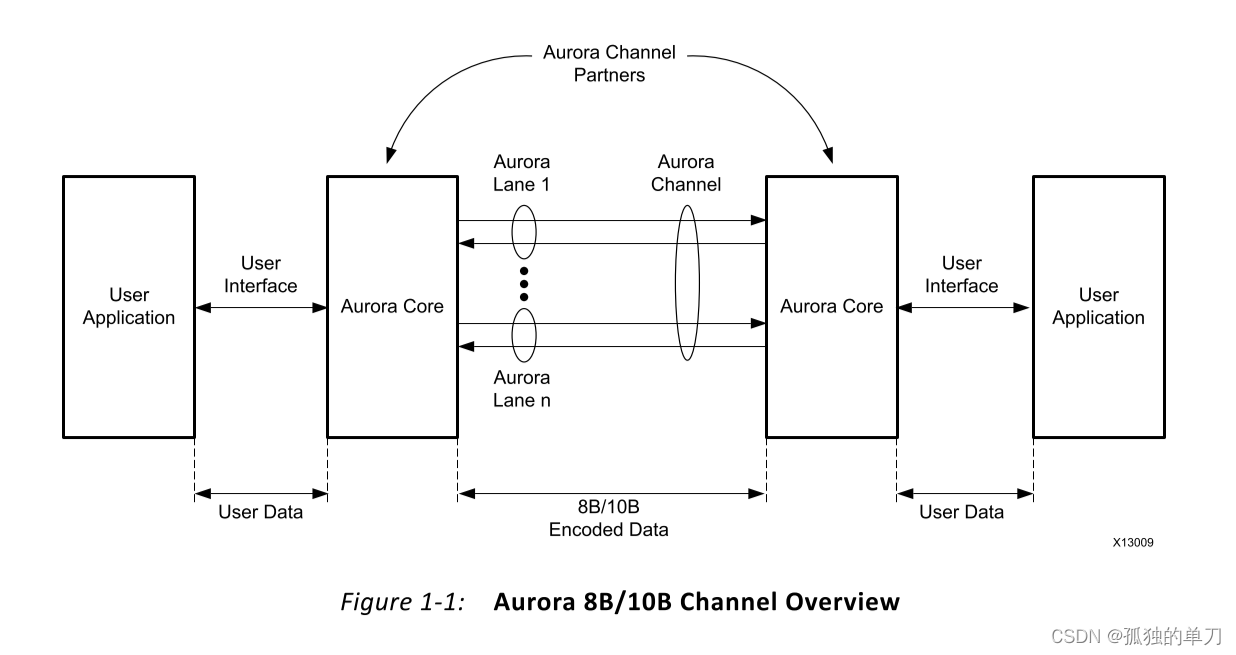

兼容性测试和独立的第三方验证。为了有助于产生“轻量级”串行协议设计,Xilinx还推出了Aurora协议—它特别适用于要求最大限度地降低开销、优化芯片资源利用率的比较简单的设计。由于以太网和PCIe技术

2019-04-16 07:00:07

(Virtex-5)或19.2Gbps(Virtex-6)或22.4Gbps(Kintex-7)2. 高速LVDS数据发送:训练序列产生,数据成帧,8B/10B编码,数据并行转串行,随路时钟产生等3.

2014-03-01 18:47:47

(Virtex-6)或22.4Gbps(Kintex-7)2. 高速LVDS数据发送:训练序列产生,数据成帧,8B/10B编码,数据并行转串行,随路时钟产生等3. 高速LVDS数据接收:接收时钟检测(检测接收

2014-03-20 22:58:55

你好,我正在尝试使用Aurora 8B / 10B建立仅传输(流媒体)。现在使用Vivado 2014.4进行模拟阶段。我知道GTXE2_COMMON原语需要在设计中使用以包含一个QUAD PLL

2020-08-14 08:49:13

嗨,我正在尝试将Aurora与Virtex-6 LX240t配合使用。示例设计是由核心生成器(11.5和12.1)生成的测试代码。当我使用环回模式(近端PCS和PMA)进行测试时,两者都能正常工作

2020-06-02 13:14:40

本方案是以CME最新的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data

2019-10-21 07:09:44

“HTG-V6-PCIE”。赛普拉斯CY7C67300 EZ-Host™可编程嵌入式USB Hostand外设控制器提供USB 2.0接口。是否可以通过赛普拉斯USB配置Virtex-6 FPGA?当我尝试

2020-07-08 07:17:34

RXD。RS232和RS485协议:RS485、RS232都是基于串口控制器的协议,只不过他们俩只是对串口控制器加了一些电气上面的处理使得串口传输的数据更远和更稳定而已。举个形象的例子:串口、RS485、RS232这三种协议都是表示从A车站发送100个旅客到B车站的,串口协议只是规定100个旅客从A车站到

2021-12-14 06:22:31

通过研究CAN2.0B协议规范,对报文格式的分析和标识符的分配,设计出了基于CAN总线的智能建筑监控系统的通信协议。

2021-06-02 06:48:03

大家好,我使用的是Vivado 2016.4和Virtex 7 XC7VX485T FPGA。我需要知道是否有一个选项可以禁用Aurora IP Core 8B / 10B中的时钟补偿功能。我可以看到IP核心文件,但它们都是只读的。谢谢,马诺

2020-08-18 09:43:40

亲爱的先生,我正在使用Vivado 2015.4。我想在收发器向导中使用通道绑定,但CB在手册中是灰色的。另外,我找不到在收发器向导中启用8b / 10b编码器的方法。如果你能给我一些建议,我将不胜感激。问候,泰迪王

2020-08-04 08:32:57

(不知何故)和GTPE2_CHANNEL的TxOutClkLock = 1和aurora_8b10b_v8_3_CLOCK_MODULE的PLL_NOT_LOCKED为0。在没有GTREFCLK

2020-06-18 11:25:45

作者:黄刚上文说完了8B/10B之后,我们再来说说貌似更复杂的64B/66B编码。很多人可能在想,8B/10B编码主要作用的优化直流平衡,从8bit中插2个bit进去,这样的话最终效果能够使长0或者

2019-07-19 07:35:57

用于高速串行设计和一致性测试的专用配置的数字串行分析仪型号 探头尖端的增强带宽扩展到支持多个带宽步骤以实现高级信号完整性独特的串行码型触发高达 3.125 Gb/s 和 8b/10b 标准协议触发,用于

2021-12-22 14:40:11

用ASM1184e和RTL8111HS做的一个PCIE2.0转四口网卡,目前网卡识别不到,有做过类似的可否指导一二,必有重谢!

2023-10-31 17:22:10

大家好,Vivado版本:15.2FPGA:Artix 7 xc7a50tAurora 8b / 10b IP v11.0(Rev 1) - 使用VHDL创建车道:1我最近一直面临着Aurora

2020-08-06 09:34:12

, SATA 和 8B/10B· 串行物理层应用软件包括 USB 2.0、DDR 1/2/3 和以太网· 抖动分析应用软件包括 InfiniiScan、EZJIT 和 EZJIT Plus· 查看和分析应用软件包括用户定义函数和串行数据均衡

2020-04-03 12:36:25

顾名思义,他是一个bus,即总线协议,如果你接触到这种协议,相信你所处的行业很可能是工业方面或者你的产品用于工业。Modbus是一种串行通信协议,是Modicon公司(现在的施耐德电气

2022-02-16 07:25:23

你好我对DSP和SRIO之间的通信感兴趣。有人知道virtex-6 FPGA是否有srio引脚,以及如何配置?

2020-06-14 14:22:51

通信协议的三要素是什么?

2021-10-27 07:32:48

我在ML605板(Virtex-6)上实现了一个系统。现在我正在尝试测量FPGA的功耗。有什么建议吗?非常感谢。p.s不是ISE中的XPower

2020-06-12 08:16:37

到b111。但是,我们在所有情况下都失去了渠道。实验设置#2:在同一背板上,但是另一块板(板#2)有一个Virtex5 FX100T器件,我们试图实例化两个4通道Aurora_8b / 10b端点

2019-10-25 09:33:25

针对virtex-6有多少Pinout微光泽?或者如何在Xilinx XPS / EDK中为virtex-6获得确切数量的微纤维I / O引脚?

2020-05-08 09:32:11

一、高速接口8B/10B的作用? 在数字通信中编码和加扰的作用是不同的。编码通常有信源编码和信道编码,8b/10b是信道编码,信道编码的作用是通过增加冗余(此外冗余为2b)以提高数据传输的可靠性。加

2022-01-18 06:16:43

采用Xilinx 公司Virtex- II Pro 系列FPGA 内嵌得SERDES 模块———RocketIO 作为高速串行协议的物理层, 利用其8B/10B的编解码和串化、解串功能, 实现了两板间基于数据帧的简单高速串行传输

2010-09-22 08:44:28 28

28 探讨了一种基于串行通信的简单、高效的通信协议制定方法。实验结果证明,该协议有效提高了串行通信的通信效率。

2010-12-03 17:22:53 18

18 此课程将教会你:1)描述Spartan-6 和Virtex-6 FPGA的6输入LUT和CLB建设的所有功能;2)指定Spartan-6 和Virtex-6的CLB资源和可用的Slice配置;3)定义可用的RAM和DSP资源块;4)正确设计I/O块和S

2010-12-14 15:09:48 0

0 赛灵思最新一代Virtex-6 FPGA系列兼容PCI Express 2.0标准

赛灵思公司宣布其最新一代Virtex-6 FPGA系列兼容PCI Express 2.0标准,与前一代产品系列相比功耗降低

2009-07-29 14:39:46 846

846 赛灵思最新一代Virtex-6 FPGA系列兼容PCI Express 2.0标准

赛灵思公司宣布其最新一代Virtex-6 FPGA系列兼容PCI Express 2.0标准,与前一代产品系列相比功耗降低50%,与竞争产品相

2009-11-11 16:46:51 816

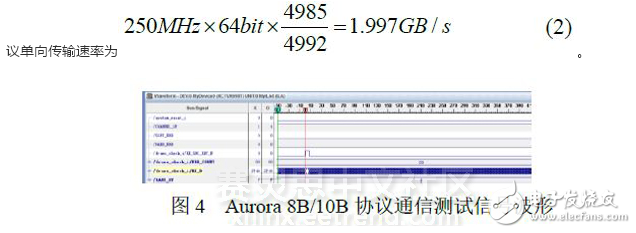

816 摘要:为提高8B/10B编解码的工作速度和简化逻辑方法,提出一种基于FPGA的8B/10B编解码系统设计方案。与现有的8B/10B编解码方案相比,该方案是一种利用FPGA实现8B/lOB编解码的模块方

2011-05-26 11:08:20 3364

3364

PCIE 3.0相对于它的前一代PCIE 2.0的最主要的一个区别是速率由5GT/s提升到了8GT/s。为了保证数据传输密度和直流平衡以及时钟恢复,PCIE 2.0中使用了8B/10B编码,即将每8位有效数据编码为10位

2012-12-03 11:45:13 55

55 CAN_2.0中文_通信协议。

2016-03-30 16:51:06 23

23 汉邦DVR通信协议规范2.0

2017-01-04 14:19:49 0

0 基于减少8B/10B编码器占用的逻辑资源和保证该编码器误码率为0的目的,采用查表法和组合逻辑实现相结合的方法设计实现了符合嵌入式互连规范Rapidl0协议的8B/10B编码器,通过伪随机二进制序列

2017-11-06 17:04:21 7

7 论序 8b/10b编码/解码是高速串行通信,如PCle SATA(串行ATA),以及Fiber Channel中常用的编解码方式。在发送端,编码电路将串行输入的8比特一组的数据转变成10比特一组

2021-09-26 09:56:22 7402

7402

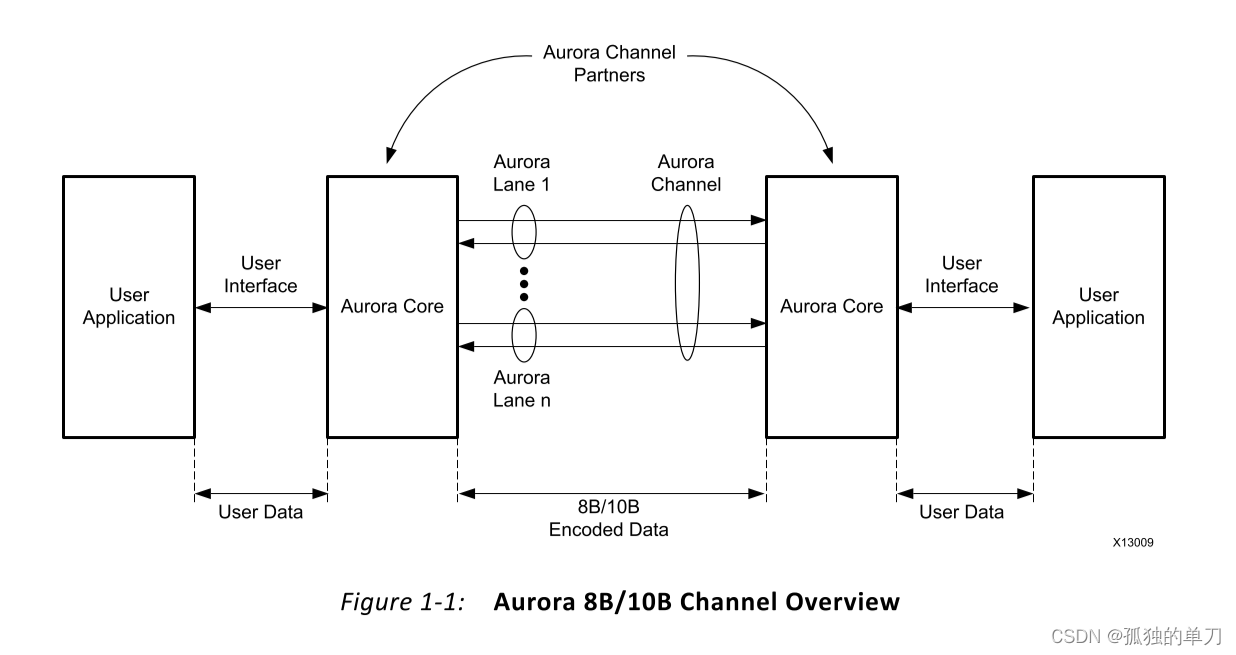

Aurora 协议是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议(由Xilinx开发提供)。这为物理层提供透明接口,让专有协议或业界标准协议上层能方便地使用高速收发器

2022-02-16 16:21:24 5810

5810

数据从远程设备(假设为DSP的SRIO端)传输过来,FPGA端(假设我们这端为FPGA的SRIO端口)通过RX接收到串行数据,先到达物理层进行时钟恢复,串并转换,之后进行8b/10b解码操作、CRC校验,这一系列的操作都在物理层完成,之后进入传输层

2023-03-03 10:19:53 725

725 各代 PCIe 标准之间的主要差异。 PCIe 3.0 PCIe2.0的传输速率为5 GT/s,但由于8b/10b编码方案的开销占比为20%,因此单lane的传输带宽为4Gb/s。PCIe 3.0及以后

2023-07-26 08:05:01 867

867

本文介绍一个FPGA常用模块:SRIO(Serial RapidIO)。SRIO协议是一种高速串行通信协议,在我参与的项目中主要是用于FPGA和DSP之间的高速通信。有关SRIO协议的详细介绍网上有很多,本文主要简单介绍一下SRIO IP核的使用和本工程的源代码结构。

2023-09-04 18:19:18 683

683

SRIO(Serial RapidIO)交换芯片是一种高性能的通信芯片,专门设计用于实现基于SRIO协议的数据交换和传输。SRIO是一种点对点串行通信协议,广泛应用于嵌入式系统、高性能计算、网络通信

2024-03-16 16:40:42 1567

1567

电子发烧友App

电子发烧友App

评论