本文主要介绍Xilinx FPGA的配置模式。

2021-01-01 10:12:00 21578

21578

的任何存储部位,包括:Flash、硬盘、网络,甚至在其余处理器的运行代码中。JTAG 模式为调试模式,可将PC 中的比特文件流下载到FPGA中,断电即丢失。此外,目前赛灵思还有基于Internet 的、成熟的可重构逻辑技术System ACE解决方案。

2022-09-22 09:13:59 3375

3375 5G核心网极简开局技术架构 5G核心网自动化集成极简开局应用 5G核心网极简开局行业推广及市场实践

2020-12-22 07:40:12

进行编程。用户可以根据不同的配置模式,采用不同的编程方式。FPGA 的使用非常灵活。目前,大部分的 FPGA 在使用时都需要外接一个 EPROM 保存其程序,加电时,FPGA 芯片将 EPROM 中

2018-09-06 09:11:58

如何得到LUT与REG的使用比例?如何分析FPGA芯片上的组合逻辑(LUT)和时序逻辑(REG)的利用率?

2021-09-17 07:01:26

由潘文明先生开创的IC/FPGA至简设计法,具备划时代的意义。这种设计方法不仅将IC/FPGA学习难度降到了最低,同时将设计过程变得简单,并规范了代码避免了混乱,将出错几率降到最低。下面我们来看

2017-12-15 15:10:57

FPGA至简设计法案例2例2. 当收到en=1后,dout间隔3个时钟后,产生宽度为2个时钟周期的高电平脉冲。 如上面波形图所示,在第3个时钟上升沿看到en==1,间隔3个时钟后,dout变1,再过

2019-08-01 09:58:24

至简设计法经典案例学习FPGA,最关键的是学什么?有读者学了大半年时间的FPGA,学了串口就只懂串口的设计,学了SPI就只懂SPI接口的设计。每个接口、每个功能,都只是学一个懂一个。换个功能需求

2018-09-14 10:18:01

请教大家一个问题,板子上有两个FPGA,想用一个PROM配置,将PROM和两个FPGA用边界扫描下载方式连起来可以吗? 就是下图这种模式,可不可以再多串一个FPGA呢?

2014-03-24 15:53:09

FPGA配置模式

2012-08-17 22:24:05

78 ps。这意味着总延迟约为 2.469 ns。IDELAY 和 ODELAY 原语可以在四种模式下运行:FIXED——延迟在此模式下是固定的,不能在运行时更改。VARIABLE – 这是一个可变

2022-10-12 14:19:39

到底什么是UART?Introduction: UART中文名:通用异步收发器,是Universal Asynchronous Receiver/Transmitter的简称,之所以称为异步(Asynchronous)是因为其将并行数据转换成串行数据进行发送。举个栗子,小明一个月的零花钱是30元,并行通信就是小明的爸爸在月初直接给30元,串行通信就是把30元拆开,每天给小明1元。由此可见,串行通信的效率较并行通信效率低,这也是串行通信的主要缺点。可是,加入小明的爸爸每天给小明1块钱,剩余的钱就可以用在别的地方(比如买烟....),所以串行通信节省传输线,这也是串行通信的主要优点。除此之外,串行通信适合于远距离传输,几米到几千公里。并行通信的传输距离一般小于30米。 由于UART总线的数据接收与发送口是独立的,所以数据接收与发送可以同时进行,专业一点叫做全双工传输与接收,这一点主要是区别IIC,iic属于半双工的传输,内部通过上拉电阻的配置进行双向传输。为了更好的理解,我们分别写UART中的RS232类型的数据接收与发送,最后在一个统一的顶层文件中调用两个子模块理解这种通用异步收发方式。引脚简写意义说明2RXDReceiver接收数据3TXDTransmit发送数据else(略)[/td][td] 补充说明:(一)、一些关键参数 (1)、UART通信在使用时需要设置一些参数,主要有数据位数(此处指的是有效数据位)、波特率(baudrate)、奇偶检验位和起始停止位。(2)、数据位:指的是单词UART数据传输期间的数据有效位数。(3)、波特率:英文名baudrate,单位是bps(就是bit per second),典型的波特率有9600,19200,115200。一般通信两端设备都设置相同的波特率。(4)、奇偶检验类型:是一种保证数据传输准确性的一种方式,比CRC(循环冗余校验)简单一些,类似于求和校验,分为奇(Odd)校验与偶(Even)校验,校验位一般加载有效数据位的左侧或者右侧。以偶校验为例,通过使检验位置1或0使得传输的数据中1的个数为偶(even)数,如: 1(校验位) 0100,0101(有效数据位),1的个数为偶数。(5)、停止位:每个字节发送完毕后发送停止位,标志着一次数据传输的结束,默认为1位,也可设置为1.5,2位,这个几位按照发送的时间来理解,所谓的1.5位就是说发送停止位的时间是1位的1.5倍,1.5个时间单位的bps,比如接下来的例程中设置波特率为9600bps,每1/9600秒发送一个bit,1.5停止位就是1.5/9600s发送一个bit。UART_RX(数据接收模块设计)1、接收端通过检测电平“1”到“0”的下降沿来确定一个数据包的开始,确定开始接受之后,依次接收数据,完成数据采集,数据的接收是先接受数据的低位,依次到最高位,接收完数据位后,继续接受奇偶校验位和停止位。2、模块构成(1)、波特率生成时序:以本实验为例,系统时钟为100Mhz(根据个人系统时钟确定),拟采用的baudrate=9600bps,也就是1s传输9600个bit。波特率时钟通过计数分频方式来得到,100_000_000/9600=10416,即分频系数=系统时钟/波特率。目前常用的数据采集有两种方式,一种是通过中心点采样,另一种的多个点概率采样的方式,核心语句是assgin uart_rx[x]=(a+b+c+d+e)>3;(2)、串口传输时序:在波特率设置完毕的情况下,根据串口传输时序进行解调,空闲状态时,数据接收端口为逻辑高电平,等待起始位逻辑低电平的到来,确定起始位后,依次接收起始位、数据低位....数据高位、停止位。 [code]`timescale 1ns / 1ps// Engineer:Lu// Module Name: uart_rx_path// Tool : Vivado2017//date:2019/09/06/*宜:嫁娶、祭祀、祈福、求嗣、出行忌:入宅、作梁、安门、伐木、修造*///////////////////////////////////////////////////// module uart_rx_path(input clk_i,input uart_rx_i,output[7:0] uart_rx_data_o,output uart_rx_done );//传输波特率设置为9600bit per secondparameter[13:0]BAUD_DIV=14'd10416;parameter[13:0]BAUD_DIV_CAP=14'd5208;reg[13:0]baud_div;//分频计数寄存器reg baud_bps;//接收时钟reg bps_start=0;//接收数据开始控制寄存器//产生接收时钟baud_bps模块always@(posedge clk_i)begin if(baud_div==BAUD_DIV) beginbaud_bps

2019-09-06 20:22:09

简牛通常为四方塑胶围墙座和若干排列整齐的四方排针组成。简牛和牛角牛角连接器的区别在简易牛角去掉了两侧的耳扣。

2019-10-21 09:02:31

简谈FPGA的片内资源

2024-01-08 22:12:08

大侠带来简谈基于FPGA的千兆以太网设计,话不多说,上货。今天我们来简单的聊一聊以太网,以太网在FPGA学习中属于比较高级的内容了,有些大侠肯定会感觉以太网学习起来非常不容易。其实,我可以告诉大家,前期

2023-06-01 18:39:46

当我运行 FPGA 然后将 img 加载到 FX3 时出现了黑屏,我使用了 amcap.exe。 FPGA 输出动态模式。 请帮我解决我的问题。

我附上了 chipscope 和 amcap.exe

2024-02-26 08:36:23

咨询一个初级A/D问题:AD9684中DCO时钟的用法(FPGA控制)。AD9684与FPGA用LVDS模式接口互联时,FPGA端如何使用?手册中没有详细说明,是DCO上升沿捕获数据,作为数据同步

2023-12-13 09:01:52

1、Armv8.1-M PAC和 BTI 扩展简析Armv8-M通过Trustzone for Armv8-M, Memory Protection Unit (MPU) 和Privileged

2022-08-05 14:56:32

,会触发一次水印中断,通过标志位的检测,可以知道 FIFO 即将满了,必须及时的将数据取走,避免触发 FIFO 满中断,导致的数据丢失)1 新消息接收中断CANFD 的消息通过中断模式接收,在不进

2022-04-14 15:43:18

1、Linux内核网络之网络层发送消息之IP分片简析本文分析下ip的分片。行 IP 分片。IP分片通常发生在网络环境中,比如1个B环境中的MTU为500B,若的数据长度超过

2022-07-20 15:34:09

自由运行准谐振运行的PWM电流模式控制器

2022-11-04 17:22:44

一、核心技术理念

图片来源:OpenHarmony官方网站

二、需求机遇简析

新的万物互联智能世界代表着新规则、新赛道、新切入点、新财富机会;各WEB网站、客户端( 苹果APP、安卓APK)、微信

2023-09-22 16:12:02

产品需求。

典型应用场景:

影音娱乐、智慧出行、智能家居,如烟机、烤箱、跑步机等。

*附件:OpenHarmony智慧设备开发-芯片模组简析RK3568.docx

2023-05-16 14:56:42

降噪,自动调色系统和梯形校正模块可以提供提供流畅的用户体验和专业的视觉效果。

典型应用场景:

工业控制、智能驾舱、智慧家居、智慧电力、在线教育等。

、*附件:OpenHarmony智慧设备开发-芯片模组简析T507.docx

2023-05-11 16:34:42

PCB的报价是怎么来的?简析PCB价格的组成_华强pcb PCB的价格是很多采购者一直很困惑的事情,很多人在华强pcb网站在线下单时也会疑问这些价格是怎么算出来的,下面我们就一起谈论一下PCB

2018-01-29 10:36:46

RF-SOI技术在5G中的应用前景简析

2021-01-04 07:02:15

1、RT5640播放时的Codec寄存器列表简析Platform: RockchipOS: Android 6.0Kernel: 3.10.92Codec: RT5640此文给调试RT5640播放

2022-11-24 18:12:43

1、Rockchip RK3399 Linux4.4 USB DTS配置步骤简析本文档提供RK3399 USB DTS的配置方法。RK3399支持两个Type-C USB3.0(Type-C PHY

2022-08-10 16:10:16

STM32定时器功能如下通常使用的是PWM模式,可以通过PWM功能可以生成频率和占空比可调的方波信号,有时候需要生成初始相位可调的方波,PWM功能就就不能满足要求了。可以通过输出比较模式来实现。输出

2021-12-06 06:22:17

stm32--GPIO一 相关寄存器一 相关寄存器STM32 的IO 口相比51 而言要复杂得多,所以使用起来也困难很多。首先STM32 的IO 口可以由软件配置成如下8 种模式:1、输入浮空2、输入上拉3、输入下拉4、模拟输入5、开漏输出6、推挽输出7、推挽式复用功能8、开漏复用功能...

2022-02-25 07:10:05

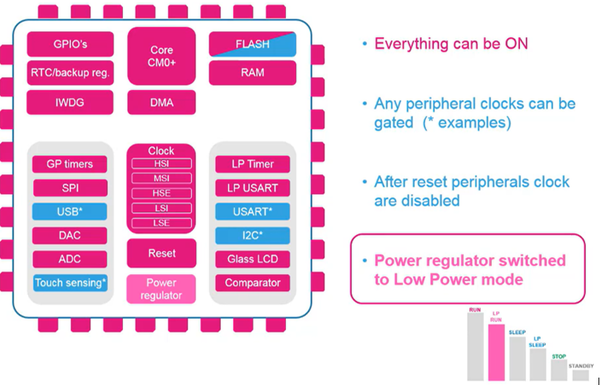

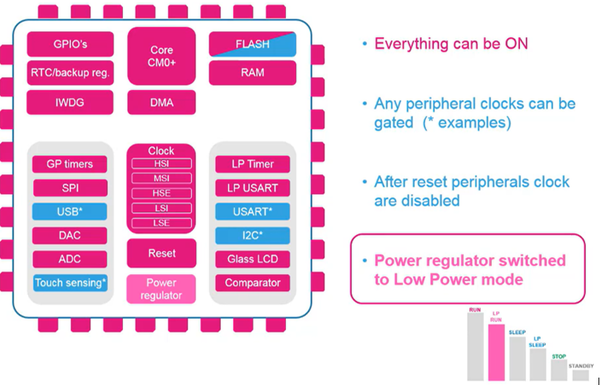

系统或者电源复位后,微控制器出于运行状态之下,HCLK为CPU提供时钟,内核执行代码。当CPU不需要继续运行时,可以利用多种低功耗模式来节省功耗,例如等...

2022-02-23 06:03:42

请问一下STM32的复位源是如何使引脚复位置位的?

2021-09-24 14:15:06

在STM32中分别有哪几个时钟源呢?AHB分频器输出的时钟送给哪几大模块使用呢?

2021-11-24 06:50:12

(69)Verilog HDL测试激励:时钟激励21.1 目录1)目录2)FPGA简介3)Verilog HDL简介4)Verilog HDL测试激励:时钟激励25)结语1.2 FPGA简介FPGA

2022-02-23 07:31:44

` 本帖最后由 chunfen2634 于 2017-6-29 15:27 编辑

大家好,这里潘老师将精心录制和编辑的fpga学习系列教程——《至简设计法视频教程》分享给大家。教程充分考虑0

2017-06-29 15:19:35

rtos的核心原理简析rtos全称real-time operating system(实时操作系统),我来简单分析下:我们都知道,c语句中调用一个函数后,该函数的返回地址都是放在堆栈中的(准确

2019-07-23 08:00:00

串联谐振耐压试验装置的参数简析串联谐振试验方案如何指定,我们先来看看串联谐振的一些基本参数和需求串联谐振耐压装置主要由变频控制器,励磁变压器,高压电抗器,高压分压器等组成。变频控制器又分两大类

2018-10-23 10:04:59

1、使用FPGA驱动ADDA开发板上的ADC工作原理简析本实验设计使用FPGA驱动10位并行AD芯片工作,将正弦模拟信号转化为数字信号,并由FPGA内部逻辑分析仪观察得到的数字信号的波形。与实验二类

2022-07-19 15:31:11

,如果它需要某些依赖库,你还需要手工下载、编译这些依赖库。 如果想做一个极简的文件系统,可以使用Busybox手工制作。 使用Buildroot自动制作 它是一个自动化程序很高的系统,可以在里面

2022-11-04 15:41:57

:我是按照官方手册的主串模式连接的电路,请问这样可以实现上述功能吗?还有模式选择端口M0,M1,M2是直接都接地呢,还是说要通过跳冒来设置?都接地为主串模式,这种情况下,能否实现方式一那样直接下载程序到FPGA呢?求高手解答。谢谢。

2013-10-18 10:06:47

简析用电阻设定增益的单端至差分转换器

2021-02-25 06:53:02

如何移植FreeRTOS最简源码?

2021-11-29 08:00:40

获取地理位置技术简析 一、 手机定位原理: 手机定位是指通过特定的定位技术来获取移动手机或终端用户的位置信息(经纬度坐标),在电子地图上标出被定位对象的位置的技术或服务。定位技术有两种,一种

2011-11-30 16:09:45

目前针对FPGA按键模式讨论的文章很少,因此本文专门探讨FPGA有哪几类按键模式?

2021-04-08 06:48:32

插值滤波器设计-明德扬至简设计与应用FPGA

2019-08-16 10:34:20

目录ASIC工程师面试经验分享商汤(一共4面,全程微信语音)- FPGA自动驾驶优化验证百度(一共3面,全程微信)- 芯片验证寒武纪(一共3面)- 芯片验证华为海思(一共3面)- 芯片在面经下的问答

2021-07-23 07:40:16

潘文明至简设计法介绍潘文明至简设计法,是以发明者名字命名的FPGA设计方法,综合采用多种科学、严谨的方法,将整个设计过程规范化,实现“至简”设计。其专著《手把手教你FPGA》2017年由北京航天

2019-07-25 16:50:44

本帖最后由 W陈老师 于 2022-3-3 10:13 编辑

潘文明至简设计法,是以发明者名字命名的FPGA设计方法,综合采用多种科学、严谨的方法,将整个设计过程规范化,实现“至简”设计。其

2022-02-18 15:30:26

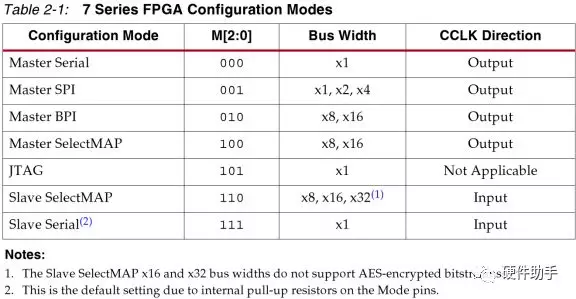

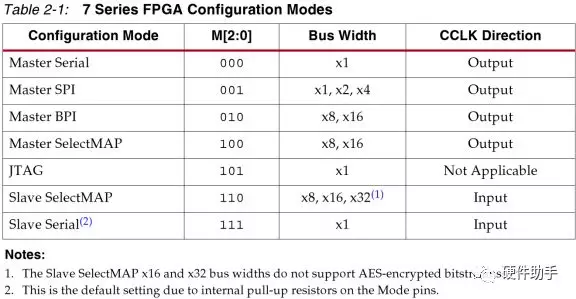

FPGA是由存放在片内的RAM来设置其工作状态的,因此工作室需要对片内RAM进行编程。用户可根据不同的配置模式,采用不同的编程方式。FPGA有如下几种配置模式:1、并行模式:并行PROM、Flash配置

2018-11-12 15:11:39

明德扬FPGA01 时序约束步骤http://v.youku.com/v_show/id_XMjg3NjY2ODU0MA==.html?spm=a2hzp.8253869.0.0潘文明至简设计法系

2017-07-27 17:05:14

LoRa模块有哪些优点?LoRa模块的应用有哪些?LoRa模块有哪几种工作模式?

2021-09-02 07:19:30

低功耗休眠,所以当在线模式时,一直没机会进入休眠模式,程序运行正常。而一旦离线运行,系统无任务时就会休眠,这样我的按

2022-01-13 07:29:46

、消防电梯、消防应急照明和疏散指示系统等。当火灾发生时,能否及时灭火、快速疏散人群、隔离火灾区域,很大程度上取决于这些消防设备能否正常运行。因此,公安部消防部门高度关注如何用技防手段实现对消防设备供电电源

2020-05-11 06:33:15

本帖最后由 chunfen2634 于 2017-6-22 14:31 编辑

我们的至简设计法,综合了运用多种科学、严谨的代码设计方法,将整个设计过程完整化、规范化,令学习方法至简、设计过程至

2017-06-22 10:20:39

,应用最为广泛,电气驱动可分为步进电机驱动、直流伺服电机驱动、交流伺服电机驱动、直线电动机驱动。交流伺服电机驱动具有大的转矩质量比和转矩体积比,没有直流打击的电刷和整流子,因而可靠性高,运行时几乎不需要维护,可用

2021-09-13 06:02:45

简析电源模块热设计注意事项

2021-03-01 06:39:03

至简设计原理与应用目录简介: 本书收集整理了作者在FPGA项目实践中的经验点滴。既有常用FPGA设计技巧;也有多个项目案例分析,小到闪烁灯,大到边缘检测,AD采集等项目,并且这些案例大都以特定

2019-07-24 12:00:04

舵机的控制原理是什么?stm32CubeMx界面该怎样去配置呢?

2021-10-22 09:12:36

可以在百度搜索蓝牙调试器可下载。里面分基础模式和专业模式,基础模式基础模式非常的简单,设置相应的按键的值就可以显现发送数据,例如用按键控制灯的亮灭。具体设置1、点击编辑模式就可以编辑相应的按键值。2

2021-12-07 06:42:07

1. 改代码,reset_vector不做判断,直接都是连接到rom起始地址。

2. 在rom代码中去修改跳转地址到QSPI(0x20000),下载到FPGA后运行正常。

仿真环境中也按上述进行

2023-08-12 08:18:01

简析运放并联的可行性

2021-03-18 08:06:57

上EasyGo FPGA Solver中的FPGA Coder解算软件,可以将用户灵活搭建的模型直接下载至FPGA中运行,而不需要进行FPGA的编译,最

2022-05-19 09:16:05

UPS单机运行模式

当有市电时,市电220VAC(或380VAC)经隔离、滤波

2006-06-08 17:55:00 7308

7308 什么是FPGA?FPGA是什么意思,本内容详加描述了FPGA的相关知识包括FPGA配置模式,PPGA特点及应用

2011-12-07 13:39:00 79099

79099 FPGA有多种配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多片FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理

2011-09-08 17:50:27 1734

1734 MSP430低功耗运行模式原理及应用,参考下。

2016-02-17 10:33:27 11

11 华清远见FPGA代码-在Xilinx的FPGA开发板上运行第一个FPGA程序

2016-10-27 18:07:54 23

23 华清远见FPGA代码-在Altera的FPGA开发板上运行第一个FPGA程序

2016-10-27 18:07:54 16

16 FPGA运行时重构的延迟隐藏机制研究与实现_刘伟

2017-01-07 19:08:43 0

0 中,而没有依赖外部架构。 下文将讲述我们是如何借助这种模式,部署和运行其中一种常被认为难以在Docker容器中运行的复杂、有状态的应用:MySQL。 运行MySQL 我们从常见的MySQL部署开始:从主节点到副本节点执行异步复制。客户端查询副本节点,或对主节点

2017-10-12 11:44:29 0

0 本演示介绍了 Spartan®-3A 入门套件如何让您立即获得 Spartan-3A FPGA 器件的节能模式,高速 I/O 选项,DDR2 SDRAM 存储器接口,商用闪存配置支持,以及利用 Device DNA 实现的 FPGA/IP 保护等特性。

2018-05-22 13:45:01 2484

2484 单片机是基于FLASH结构的,所以单片机上电直接从本地FLASH中运行。但SRAM 架构的FPGA是基于SRAM结构的,掉电数据就没了,所以需要借助外部电路来配置运行的数据,其实我们可以借助Vivado来学习FPGA的各种配置模式。

2018-11-05 15:12:57 7298

7298 Altera FPGA支持AS,PS,JTAG等几种较常见的配置方法。 当为AS配置模式时,FPGA为主设备,加载外部FLASH中的数据至内部RAM中运行。当为PS配置模式时,FPGA为从设备,外部

2018-11-18 18:05:01 481

481 在此Xilinx研究实验室演示中,解释了单源SYCL C ++示例以及生成在Xilinx FPGA上运行的硬件实现的方法。

2018-11-20 06:30:00 2918

2918 网络摄像机监控一般来说都是围绕四种方式运行,即网关模式、网桥模式、旁路模式及旁听模式。

2020-03-22 17:21:00 896

896 在安防监控工程的工作模式中,网络摄像机监控一般来说都是围绕四种方式运行,即网关模式、网桥模式、旁路模式及旁听模式

2020-03-22 22:07:18 1796

1796 赛灵思公司的FPGA芯片具有IEEE 1149.1/1532协议所规定的JTAG接口,只要FPGA上电,不论模式选择管脚M[1:0] 的电平,都可用采用该配置模式。JTAG模式不需要额外的掉电

2020-12-31 17:30:55 13

13 ,FPGA作为传统的处理器加速方案,工程师必须要解决空间、I/O延迟和带宽之类的问题。 而近些年来,eFPGA(嵌入式FPGA)的概念正在不断兴起。与将芯片与必要的I/O和电源管理电路封装在一起的FPGA不同,eFPGA推行的是卖IP模式。任何厂商都可以将这些eFPGA I

2021-11-17 09:10:58 1413

1413 一. 认识低功耗运行模式低功耗运行模式,是降低了功耗的运行模式,CPU 依然处于运行状态,只是这个时候的频率降低了,导致运行速度变慢,但是功耗同时也下降了。通过上图可以得到信息:电压调节器设置

2021-12-07 18:36:10 4

4 典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2022-03-14 14:02:50 1366

1366 在 Windows 下,我喜欢在批处理模式下运行 Vivado 仿真器。 我创建了仿真批文件 (.bat) ,包含以下命令。当我运行批文件,执行第一条命令后脚本中止。如何正确在批模式下运行 Vivado 仿真器?

2022-08-01 09:43:01 728

728 电子发烧友网站提供《安路EG4X FPGA从动串行加载模式.pdf》资料免费下载

2022-09-27 10:55:18 1

1 电子发烧友网站提供《安路EG4X FPGA从动并行加载模式.pdf》资料免费下载

2022-09-27 10:44:27 1

1 尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

2022-10-10 14:37:57 1272

1272 数据模式。 FPGA配置方式 根据FPGA配置过程控制者的不同,我们将配置方式主要分为三类: FPGA控制配置过程 第一种最常见的模式是,从片外FLASH中加载配置所需的比特流,FPGA内部产生时钟,整个过程有FPGA自主控制。FPGA 上电以后,将配置数据从FLASH中,读入到

2022-11-21 21:45:10 955

955 典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

2023-02-15 09:57:24 618

618 当系统时钟频率降至 2 MHz 以下时,可实现此模式。代码从 SRAM 或闪存中执行。稳压器处于低功耗模式以最小化其工作电流。 3.2配置低功耗运行模式 3.2.1 STM32CubeMX

2023-03-23 14:40:05 432

432

服务器已安装Windows Server操作系统,通过配置BIOS和电源选项可使CPU在超频模式下运行。

2023-03-27 10:52:42 1495

1495 总结Xilinx FPGA 的上电模式可以分为以下4类型: 主模式 从模式 JTAG模式(调试模式) 系统模式(多片配置模式) 1、主模式 典型的主模式都是加载片外非易失( 断电不丢数据

2023-03-29 14:50:06 535

535 今天的教程讲下MSPM0L系列的运行模式。

2023-05-29 11:21:08 1383

1383

电子发烧友网站提供《基于FPGA+DSP模式的智能相机设计.pdf》资料免费下载

2023-10-08 10:37:16 0

0 电子发烧友网站提供《基于FPGA的模式匹配系统设计.pdf》资料免费下载

2023-11-08 09:26:42 0

0 动态无功补偿装置作为电力系统中重要的设备,扮演着优化功率因数、改善电网稳定性的关键角色。在实际运行中,动态无功补偿装置通常有三种主要运行模式,分别为“手动模式”、“自动模式”和“半自动模式”。深入

2024-02-28 14:17:39 140

140

电子发烧友App

电子发烧友App

评论