深入理解AES算法的底层原理。

2017-10-26 14:40:07 45505

45505 AES加密算法流程图如下图所示: 明文P:未加密的原始数据;密钥K:加密原始数据密码,对称算法中,加密与解密所需的密钥相同,该密钥不能直接进行传输,否则会造成密钥泄露; 常规的做法是使用非对称算法

2022-11-21 19:29:45 1858

1858

牢不可破。 AES加密核能同时用于FPGA核本身以及独特 FlashROM (FROM) 内存的加密中。每个FPGA都被分成两部分:FPGA阵列和FlashROM,两者都可独立编程,容许在不改

2019-07-09 09:11:44

AES算法包括哪些?AES算法的流程是怎样的?AES 256算法是如何被破解的?

2021-11-12 07:56:55

本帖最后由 发烧友LV 于 2014-12-29 20:13 编辑

在FPGA中实现PID算法,面临着小数的计算,请问大家一般是怎么处理的?

2014-12-03 21:59:29

设备替换功能是浩辰CAD电气软件中的一个基础功能,此功能可以完成不同种类设备之间的相互替换。之前的CAD新手教程中给大家介绍了强电平面的设备替换功能使用技巧,那么你知道弱电平面设计中设备替换功能

2022-05-11 14:05:30

LT1963AES8

2023-03-28 13:19:59

1、M487芯片CRYPTO模块中对称加密AES功能测试本次测评主要测试新唐M487芯片CRYPTO模块中对称加密AES功能及其性能,性能方面会使用硬件加速和纯软件实现直接的效率差异。M487中

2022-04-22 17:52:48

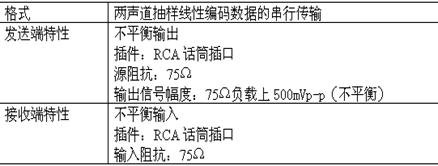

`广播专业AES系列数字音频光端机,采用先进的广播和通信专业芯片。使用先进的FPGA、多路时分复用和时钟恢复技术。输入自动均衡,时钟恢复,低抖动,透明传输完整AES格式信息。在1芯光纤上,传输10路

2011-03-13 22:54:43

正文 AES(Advanced Encryption Standard,高级加密标准)算法,是一种最常见的对称加密算法。AES 在密码学中又称 Rijndael 加密法,是美国联邦政府采用的一种区块

2022-10-28 08:06:00

我从OpenCores下载了vhdl中的aes代码但有些代码我不明白这里的所有代码aes_pkg.vhdl aes_enc.vhd key_expansion.vhdl aes_dec.vhd你

2019-02-21 11:13:01

字节传输的具体实现流程如图 4-6 所示。图 4-6 字节传输控制模块流程图字节传输控制模块控制以字节为单位的数据传输。它根据命令寄存器的设置将数据传输寄存器中的内容传输到外部节点,将外部节点的数据

2018-10-10 10:34:14

。本方案以FPGA实现AES加密算法为目的,硬件角度加速AES加密。不知道这个方案有没有吸引力,如果有的话就继续写设计方案了

2012-06-12 23:12:59

字节的数据。大多数的液晶显示模块HD44780的芯片或兼容的基础上。提供一个良好的信息页。【FPGA设计实例】FPGA接口实现文本液晶显示模块[hide] [/hide]`

2012-03-14 11:11:15

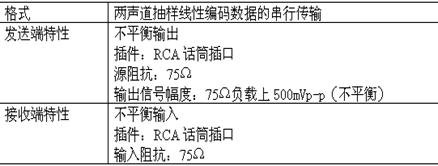

非常重要。通道状态存储器描述了在AES/EBU数据流通道中比特分配及其含义。例如的字节0的比 特0表示是家用级还是专业级,如果通道用于消费,字节0中比特0置0;用于专业时置1。奇偶校验比特(P):通常为

2009-08-01 08:17:09

什么是AES算法?如何对AES算法进行优化?怎样快速实现AES算法?

2021-04-28 06:51:19

本人想雇人用VHDL编写一个用AES对一段文字或者图像进行加密和解密。再实现的同时想看一下加密和解密所用的时间和速度。有哪位前辈有意,可以回复 价格再议。

2014-02-19 15:04:49

过程算不算是一种系统调用?在这篇博客中,我们会先简单探究AES加解密的原理,然后对比ruby和golang的实现过程。产生的疑问在项目开发的过程中,我们时常会用户会用到AES加解密, 但也仅仅是利...

2021-07-22 08:25:36

基于FPGA的可编程AES加解密IP

2021-01-21 07:39:11

嗨,我是一名本科生,也是使用FPGA套件的新手。在我的最后一个学期项目中,我使用Spartan 3A-3400 DSP套件实现AES,但我在查找AES-192和AES-256的verilog代码

2019-09-11 11:24:58

在FPGA中遇到的一个疑难问题,求解答!我在Stratix II GX 中要实现这样一个功能:用20M时钟采集100路数据,然后将这些数据组成每字节10bit,每11字节一帧的数据,其中包括一个帧头

2014-11-17 14:45:36

1、在FPGA中实现串口协议的设计在FPGA中实现串口协议,通过Anlogic_FPGA开发板上的“UART2USB”口接收从计算机发来的数据。实验设计思路UART串口是一种类似于USB、VGA

2022-07-19 11:09:48

加密。库中的示例代码“aes”不在 ESP 上运行,因为它涉及源代码中包含的一些 avr 库,但我隔离了库的主要加密和解密部分,并设法编译和运行代码。使用我的代码,我能够定义纯文本字符串,使用预定

2023-02-27 09:21:41

如图,在custom_aes函数中,得到的结果是一个128位的数据,但是C却不能定义这么大的数据,从而只定义32位的变量来接收这个结果,但是只能接收到低位的32位,请教各位大神,有没有什么方法可以实现呢?

2023-08-16 07:53:24

Programmable AES Encryption IP可编程AES加密IP可以集成到FPGA中,实现了AES(Advanced Encryption Standard) Rijndael加解密

2018-11-15 09:28:49

我在 S32K118 硬件上启用了 Csec 模块。上位机需要执行软件AES128-CMAC算法,然后将CMAC值发送给ECU进行校验。但是我不知道如何实现AES128-CMAC,你能给我一些建议吗?

2023-05-04 08:06:21

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一个单独的奇偶校验写使能位,但在FPGA RAM中没有单独的Pariaty写使能位。 如何实现ASIC RAM奇偶校验写入启用ino FPGA RAM。谢谢娜文G K.

2020-04-24 09:37:05

大家好,我正在研究Spartan 6(xc6slx45csg324-2)评估板,我正在尝试从xapp1014实现AES3串行数字音频接口。AES3输入和输出按照AES3-Spec中的规定连接。我

2019-08-08 10:03:48

美国国家标准与技术局(National Institute ofStandard and Technology,NIST)于1997年1月提出发展AES(Advanced Encryption

2019-08-06 06:19:10

为了系统的扩展性和构建良好的人机交互,如何利用FPGA的硬件描述语言来实现AES的加解密算法?

2021-04-08 06:01:05

如何去实现AES算法走D1芯片硬件CE模块补丁呢?有哪些步骤?如何去测试?

2021-12-28 06:59:42

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。那么该如何在低端FPGA中实现DPA的功能呢?

2021-04-08 06:47:08

这一样本代码展示了如何实施软件AES(高级加密标准)以及AES加密/解密如何运作。

您可以在下列时间下载样本代码http://www.nuvoton.com/resources-downlo.1218180400。

nuvoton 核

2023-08-22 06:41:26

应用程序:示例代码是进行 AES 加密和解密,将 AES 的私人密钥储存在 SPROM 中 。

BSP 版本:M480系列BSP CMSIS V3.03.001

硬件

2023-08-22 06:58:43

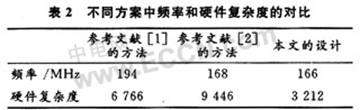

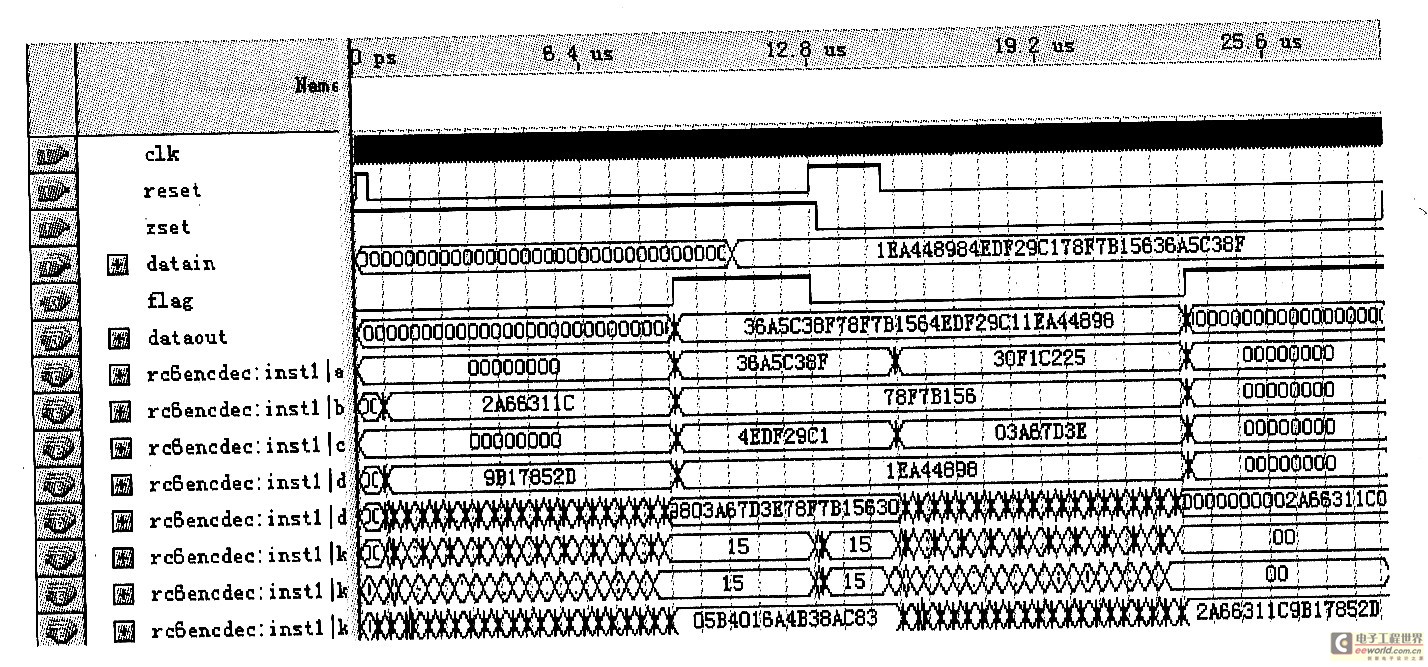

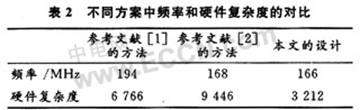

方面不支持64位操作,于是RC6修正这个错误,使用4个32位寄存器而不是2个64位寄存器,以更好地实现加解密。利用FPGA来实现RC6算法,可以提高运算速度。芯片设计为RC6算法处理器,辅助计算机处理器完成加解密操作,可以方便地实现对加解密的分析和研究。因此,此芯片可以作为协处理器来看待。

2019-08-19 07:27:09

目录背景AES加密的几种模式基本运算AES加密原理Matlab实现Verilog实现Testbench此文重点讲述了AES加密算法的加密模式和原理,用MATLAB和Verilog进行加解密的实现。美

2021-07-28 07:34:30

V3.00.0003

硬件:NuMaker-M2354 VER1.1

M2354系列MCU具有超低功率消耗特征,并有一个适合具有安全通信的IoT装置的加密加速器。

该示例代码用于在 AES GCM 中

2023-08-29 07:05:28

请问matlab如何实现文本内容批量替换?

2021-11-19 08:08:53

如何使用Verilog硬件描述语言实现AES密码算法?

2021-04-14 06:29:10

密钥生成方案产生。大多数AES计算是在一个特别的有限域完成的。AES加密过程是在一个4×4的字节矩阵上运作,这个矩阵又称为“状态(state)”,其初值就是一个明文区块(矩阵中一个元素大小就是明文区块中

2016-08-12 11:58:43

,缩写:AES),在密码学中又称Rijndael加密法,是美国联邦***采用的一种区块加密标准。这个标准用来替代原先的DES,已经被多方分析且广为全世界所使用。经过五年的甄选流程,高级加密标准由美国

2016-07-09 17:24:33

接口:标准I2C协议接口算法: 标准AES256 / KAS算法特殊接口:Random Stream Cipher for Interface温度: 工业级 -40°c ~ +85°c擦写次数

2022-04-29 08:56:08

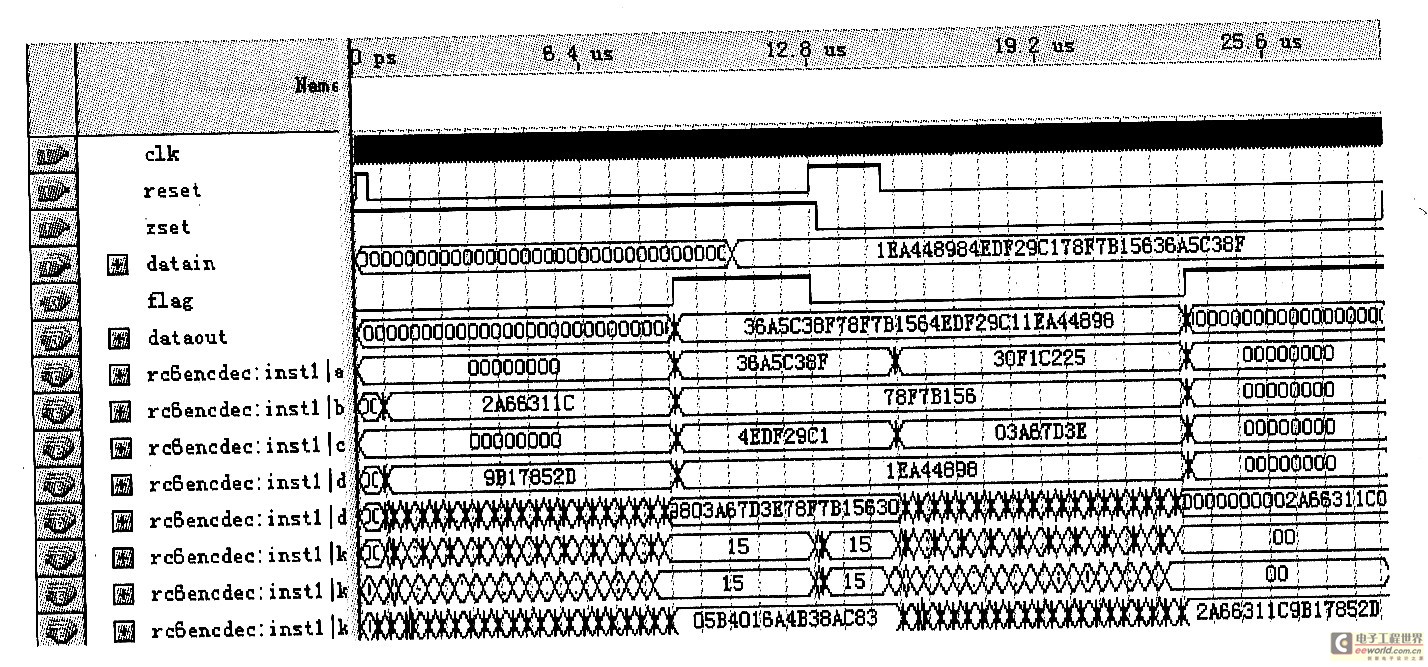

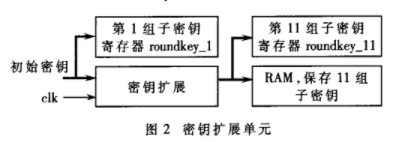

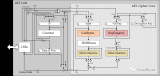

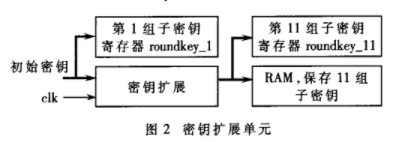

分析AES算法原理,构建基于FPGA的硬件实现框架,描述数据加解密单元和密钥扩展单元的工作机制和硬件结构,引入核心运算模块复用的设计思想,在不影响系统效率的前提下降低芯

2009-04-13 09:48:58 21

21 针对商业加密引擎中硬件资源和电路性能平衡问题,提出一种基于AES的低成本可重构的高速加密引擎的设计方案。该方案在AES加密算法的基础上,根据FPGA内在的结构特点,利用VHDL语

2009-04-16 09:53:49 18

18 AES加密快速实现中利用了查表操作,查表的索引值会影响Cache命中率和加密时间,而查表的索引值和密钥存在密切关系。通过分析AES最后一轮加密过程中查表索引值与密文和最后一轮

2009-04-18 09:42:35 32

32 本文提出了一种基于AES 实现的口令认证方法。该算法不使用公开密钥算法,仅采用AES 进行远程用户的身份认证。该方法具有速度快,安全性高的特点,易于采用令牌(Token)或IC 卡

2009-08-05 10:43:03 14

14 本系统以AES 加密算法为例,使用Xilinx SPARTAN 3E 为开发平台,以xilinx 的嵌入式软核microblaze 为主控制器,调用FPGA 的硬件VHDL 编程实现的AES 加解密和控制CC2420 来实现高速有效的

2009-11-30 14:01:08 18

18 文章简单的介绍了GPON 的体系结构与下行帧的结构,并着重介绍了AES 加密的流程、方法与具体算法,最后对GPON 中的AES 加密,解密方法,AES 计数器模式在GPON中的使用进行了详细

2009-12-14 10:23:11 16

16 AES 算法是新一代加密标准算法,文中对OpenSSL 中AES 算法的基本原理和性能进行了分析,针对其速度慢的缺点,提出了一些改进AES 算法的策略,改进的算法能有效提高加密算法操

2009-12-25 16:06:32 12

12 用硬件实现数据加密已成为信息安全的主流方向。本文提出了一种基于FPGA 的低成本的AES IP核的实现方案。该方案轮内部系统资源共用,减少了系统资源的占用。输入密钥与输入数据

2010-01-06 15:11:03 10

10 本文实现了一种基于AES 算法的无线加密数字传输系统,给出了该系统的结构,完成了AES 算法在FPGA 上的实现,将音频接口集成到FPGA,并用GPRS 网络进行音视频等数据的实时传

2010-01-22 15:09:39 5

5 介绍AES 算法的原理以及基于FPGA 的高速实现。结合算法和FPGA 的特点,采用查表法优化处理了字节代换运算、列混合运算。同时,为了提高系统工作速度,在设计中应用了内外结合

2010-01-25 14:26:51 29

29 介绍AES算法的原理以及基于FPGA的高速实现。结合算法和FPGA的特点,采用查表法优化处理了字节代换运算、列混合运算。同时,为了提高系统工作速度,在设计中应用了内外结合的流水线

2010-07-17 18:09:43 44

44 介绍了AES中,SubBytes算法在FPGA的具体实现.构造SubBytes的S-Box转换表可以直接查找ROM表来实现.通过分析SubBytes算法得到一种可行性硬件逻辑电路,从而实现SubBytes变换的功能.

2010-11-09 16:42:48 25

25 AES/EBU接口标准

AES和EBU一起开发的数字音频传输接口标准:AES/EBU标准,即AES3-1992,ANSI S4.40-1992,或IEC-958标准。它是传输和

2009-08-01 08:15:54 14734

14734

利用FPGA来实现RC6算法的设计与研究

引 言

RC6是作为AES(Advanced Encryption Standard)的候选算法提交给NIST(美国国家标准局)的一种新的分组密码。它是在RC5的基础上

2009-12-28 09:20:15 1022

1022

AES算法中S-box和列混合单元的优化及FPGA技术实现

由于其较高的保密级别,AES算法被用来替代DES和3-DES,以适应更为严苛的数

2010-04-23 09:34:22 2692

2692

本系统以AES加密算法为例,使用Xilinx SPARTAN 3E为开发平台,以Xilinx的嵌入式软核Microblaze为主控制器,调用FPGA的硬件VHDL编程实现的AES加解密和控制CC2420来实现高速有效的数据通信

2011-04-23 11:22:17 1477

1477

本文在分析AES加密算法原理的基础上,着重说明算法的实现步骤,用C语言完整地实现了AES算法的加/解密操作,并在PVR机顶盒中实现应用。

2011-09-24 01:00:58 1831

1831

差分功耗分析是破解AES密码算法最为有效的一种攻击技术,为了防范这种攻击技术本文基于FPGA搭建实验平台实现了对AES加密算法的DPA攻击,在此基础上通过掩码技术对AES加密算法进行优

2011-12-05 14:14:31 52

52 基于AES的加密算法具有速度快、强度高、便于实现等优点和ECC加密算法具有密钥分配与管理简单、安全强度高等优点,采用AES加密算法加密大数据块,而用ECC加密算法管理AES密钥,通过

2012-03-20 10:24:39 42

42 文中介绍了高级加密算法(AES)的基本原理,并给出了基于AES算法硬件加密模块设计方案。通过Modelsim6.le对其进行仿真实现,仿真结果表明,该加密模块能够很好的实现AES算法

2013-02-21 15:52:41 0

0 基于AES加密算法的S盒优化设计_胡春燕

2017-03-19 11:31:31 2

2 AES是一种区块加密标准算法,它的提出是为了升级替换原有的DES加密算法。因此它的安全强度高于DES算法。但不应片面理解,系统和数据的安全不仅与应用的加密算法有关,更与加密应用方案有关。和DES算法一样,AES也属于对称加密算法,对密钥的存储与保护,直接决定了整个系统的安全。

2018-06-29 12:06:00 159716

159716 LORA6500AES 5w LORA AES加密无线数传模块 的资料

2017-09-05 17:46:49 26

26 介绍了AES加密标准的Rijndael实现方法,设计了一种适合应用于嵌入式系统32位数据界面时序紧凑的AES加密IP核。该IP核能以较低的资源消耗实现在低端FPGA上速度为256Mb/s的AES加密,且可将数据位宽扩展为64位或128位等,满足多种数据位宽应用的要求。

2017-09-07 19:14:58 13

13 根据AES算法的特点,从3方面对算法硬件实现进行改进:列混合部分使用查找表代替矩阵变换,降低算法实现的运算复杂度,采用流水线结构优化关键路径一密钥拓展,提升加密速度,利用FPGA定制RAM

2017-11-02 10:59:59 0

0 CC2541是一款基于BLE开发的芯片,该芯片白带的AES协处理器(AES Coproc:essor)可以实现CBC、CFB、OFB、CTR、ECB、CBC MAC等多种加密解密算法。TI官方提供

2017-11-08 14:15:20 33

33 一种AES算法实现是采用轮展开的流水线结构,吞吐量很大可达到10 Gb/s量级,但消耗大量的逻辑面积。考虑在资源少的FPGA上实现AES算法,能满足低端应用的加、解密速度一般不超过100Mb

2017-11-23 11:38:20 2643

2643 1 引 言 AES加密算法的一种优化的FPGA实现方法 随着密码分析水平,芯片处理能力和计算技术的不断进步,des的安全强度已经难以适应新的安全需要,其实现速度、代码大小和跨平台性均难以继续满足

2017-11-30 01:31:26 1789

1789 由于对广泛使用的AES算法的性能要求越来越高,基于软件的密码算法已经越来越难以满足高吞吐量密码破解的需求,因此越来越多的算法利用现场可编程逻辑门阵列( FPGA)平台进行加速。针对AES算法

2017-12-03 09:49:02 7

7 的DES,已经被多方分析且广为全世界所使用。本压缩文件中对于AES的各个步骤分别打包为FUNCTION,便于查找。实现语言为matlab。

2018-05-25 15:18:19 11

11 FPGA 进行物理加密具有很好的防攻击性,实时性好, 可实现高速数据处理,资源占用非常小,是空间数据加密的重要发展方向。

2018-12-30 09:31:00 5156

5156

AES算法作为DES算法的替代者应用非常广泛,其硬件实现方法已有不少讨论,主要是通过提高算法频率来提高吞吐量。但是在实际运行中,为了保证整个加密系统的稳定性,通常全局时钟频率较低,不可能达到算法的仿真频率,如PCI接口电路时钟频率只有33MHz,因此实际数据吞吐量仍然较低。

2019-04-18 08:15:00 3057

3057

idkt是一个高性能的安全存储设备系列,提供2k字节的用户内存,具有先进的内置aes 256安全引擎和加密功能。存储器被分为8个用户区,每个用户区分别设置不同的安全访问权限,或者一起使用为一个或多个数据文件提供空间。配置区域包含用于定义idkt全局安全ic的安全逻辑所使用的aes256密钥的寄存器。

2019-10-22 16:53:13 12

12 是用一个单元数据替换另一个。AES使用了如下几种不同的技术来实现置换和替换。字节替代(SubBytes):通过非线性的替换函数,用查找表的方式把分组的字节矩阵中的每个字节用同一个S-BOX替换成另外一个字节

2019-12-06 21:57:54 6425

6425 AES算法的主要数学基础是抽象代数,其中算法中的许多运算是按单字节(8bits)和4字节(32bits)定义的,单字节可看成有限域GF(2)中的一个元素,而4字节则可以看成系数在GF(2)中并且次数

2020-01-17 14:19:00 16

16 Rijndael算法为高级加密标准AES。AES密码算法的加密速度快,安全级别高,已经成为加密各种形式的电子数据的实际标准。目前,针对AES密码算法的加密技术已成为研究热点。论文提出了一种低成本的AES密码算法的硬件实现方法,并且使用FPGA器件实现了具体的设

2020-03-19 17:16:22 6

6 美国国家标准技术局(NIST)于2001年发布高级加密标准(AES),用来取代DES,从而成为广泛使用的对称分组加密标准。针对AES的硬件实现人们做了许多有意义的研究工作,有的着力于采用流水线结构

2020-04-20 17:59:03 10

10 实现,经过仿真并在Xilinx Spartan 3系列FPGA上进行综合验证,可以将结构简化,使AES电路面积得到优化,明显节约硬件资源。

2021-01-25 14:27:14 19

19 通过将AES算法模块化、运算一般化,给出了类AES算法的统一框架。在此框架下不仅可以同时实现AES的加密、解密,而且可以通过外部参数动态设定分组算法,使得密码算法的使用更加灵活、安全。给出了算法的FPGA实现。结果表明设计方案可行,速度较高。

2021-03-26 15:58:04 16

16 基于FPGA的AES算法中S-box和列混合单元优化

2021-06-08 10:52:39 7

7 密钥的未知字节长度。结合注入故障后输出的错误密文,可通过穷举猜测的方式恢复初始密钥未知字节。攻击测试结果表明,通过该方法执行一次有效故障注入攻击能得到4字节长度初始密钥,即对于128位AES算法,攻击者仅需猜测4×23次就

2021-06-08 14:16:35 4

4 /UltraLite家族、iCE40UltraPlus家族全型号器件详情链接:FPGA.EQ6GL9小型低功耗百万门级FPGA替换XILINX/赛灵思:XC6SLX4、XC6S

2022-03-02 09:26:57 5428

5428

本文档介绍了AES 硬件 IP 功能。高级加密标准 (AES) 是 OpenTitan 协议中使用的主要对称加密和解密机制。 AES 单元是一个加密加速器,它接受来自处理器的请求以加密或解密 16 字节的数据块。它作为外设模块连接到芯片互连总线,符合外设功能的要求指南。

2023-08-03 10:46:50 442

442

电子发烧友网站提供《在Virtex-6 FPGA中使用全数字VCXO替换技术实现三倍速率SDI直通.pdf》资料免费下载

2023-09-14 14:52:17 3

3

电子发烧友App

电子发烧友App

评论