基于eFPGAsim的电机硬件在环测试系统,是面向电驱HIL测试的高精度FPGA的解决方案,利用最新的eHS (Electric Hardware Solver)技术实现,在获得基于FPGA片上仿真

2017-08-09 10:52:21 2930

2930

Block实现32位单精度浮点的卷积运算,而针对定点及低精度的浮点运算,则需要对硬浮点DSP Block进行相应的替换即可。

2018-07-23 09:09:45 7321

7321

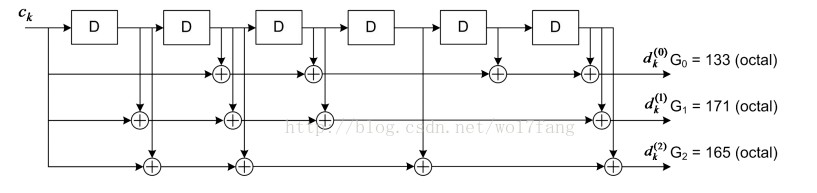

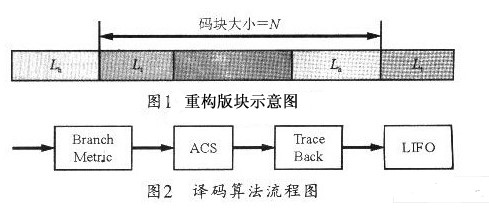

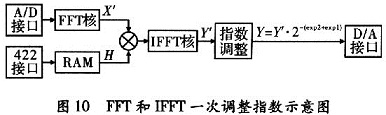

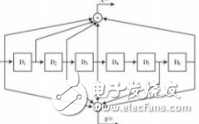

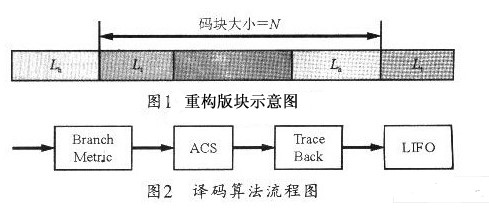

咬尾卷积码的原理是尾卷积码保证格形起始和终止于某个相同的状态。它具有不要求传输任何额外比特的优点。

2018-08-21 09:11:53 6662

6662

一个卷积操作占用的内存 2. PipeCNN可实现性 PipeCNN论文解析:用OpenCL实现FPGA上的大型卷积网络加速 2.1 已实现的PipeCNN资源消耗 3. 实现大型神经网络

2022-07-10 09:24:45 1672

1672 灵思All Programmable FPGA 和 SoC 实现高速无线电设计( Enabling High-Speed Radio Designs with Xilinx All

2017-02-10 17:10:32

本人刚入门FPGA,不知道如何实现FPGA+DSP,FPGA+ARM接口设计,网上查询有的说FPGA+DSP可以通过EMIF,IP核实现,FPGA+ARM可以通过SPI,有没有具体硬件参考的?

2016-08-27 11:30:26

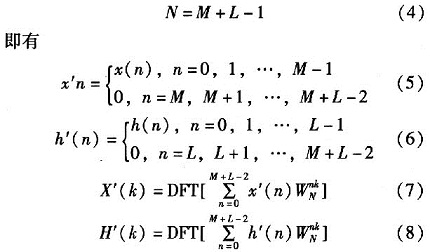

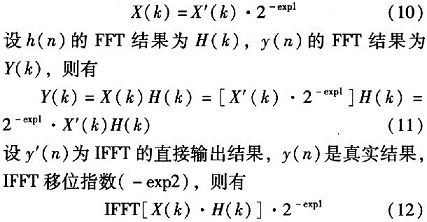

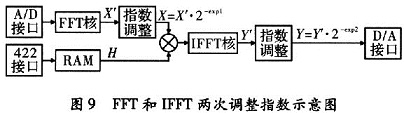

FPGA实现高速FFT处理器的设计介绍了采用Xilinx公司的Virtex - II系列FPGA设计高速FFT处理器的实现方法及技巧。充分利用Virtex - II芯片的硬件资源,减少复杂逻辑,采用

2012-08-12 11:49:01

请问各位大神,我想问一下用FPGA做卷积码有什么注意的地方?

2015-04-07 12:57:40

卷积特性(卷积定理).zip

2017-10-04 11:36:30

这是一个高速硬件除法器,要求画出此硬件的除法器的工作流程图。说明其工作原理特别是高速原理。要求有仿真时序波形图并说出说明在fpga上验证器硬件功能。

2020-12-17 09:10:03

高速移动下OFDM均衡器的FPGA实现

2012-08-17 10:48:23

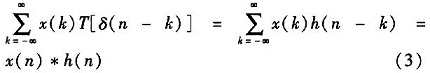

实现线性卷积的原理二 实验内容及要求1.对N=2048或4096点的离散时间信号x(n),试用Matlab语言编程分别以DFT和FFT计算N个频率样值X(k), 比较两者所用时间的大小。 2.对N/2点

2011-12-29 21:52:49

算法的软件实现方式非常低效,所以业界对GNN的硬件加速有着非常迫切的需求。我们知道传统的CNN(卷积神经网络网络)硬件加速方案已经有非常多的解决方案;但是,GNN的硬件加速尚未得到充分的讨论和研究,在

2021-07-07 08:00:00

探索整个过程中资源利用的优化使整个过程更加节能高效预计成果:1、在PYNQ上实现卷积神经网络2、对以往实现结构进行优化3、为卷积神经网络网路在硬件上,特别是在FPGA实现提供一种优化思路和方案

2018-12-19 11:37:22

和概率译码两种。代数译码根据卷积码自身的代数结构进行译码,计算简单;概率译码则在计算时考虑信道的统计特性,计算较复杂,但纠错效果好得多。典型的算法如:Viterbi 译码、序列译码等。随着硬件技术的发展,概率译码已占统制地位。[此贴子已经被作者于2008-5-30 16:09:13编辑过]

2008-05-30 16:06:52

反卷积deconvolution引起的棋盘效应?kernel size无法被stride整除的原因?解决反卷积deconvolution存在的弊端的思路?反卷积deconvolution如何实现更好的采样 ?

2020-11-04 08:08:00

处理,设计出高速高精度 且低功耗的加速方案,并完成相关仿真和FPGA平台的验证,实现一个可以框选出图像中行 人或其他物体位置的硬件电路。

本项目的系统框图如图2-1所示,首先PS端从SD卡读取图片并

2023-06-20 19:45:12

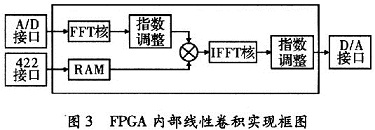

在数字信号处理领域,离散时间系统的输出响应,可以直接由输入信号与系统单位冲激响应的离散卷积得到。离散卷积在电子通信领域应用广泛,是工程应用的基础。

2019-10-16 07:52:21

本帖最后由 gk320830 于 2015-3-8 21:23 编辑

开始科创,老师给了我们一个题基于FPGA的FFT算法硬件实现。但是什么都不会,想找些论文看看,求相关的论文

2012-05-24 22:14:40

我们在此基础上修改,从而实现,基于FPGA的动态图片的Sobel边缘检测、中值滤波、Canny算子边缘检测、腐蚀和膨胀等。那么这篇文章我们将来实现基于FPGA的Sobel边缘检测。图像边缘:简言之,边缘

2017-08-29 15:41:12

基于FPGA的超高速FFT硬件实现介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA

2009-06-14 00:19:55

FPGA 上实现卷积神经网络 (CNN)。CNN 是一类深度神经网络,在处理大规模图像识别任务以及与机器学习类似的其他问题方面已大获成功。在当前案例中,针对在 FPGA 上实现 CNN 做一个可行性研究

2019-06-19 07:24:41

求助!大佬们,问一下用FPGA实现卷积码编解码的难度。

2023-10-16 23:26:26

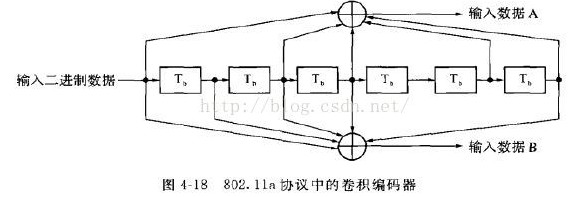

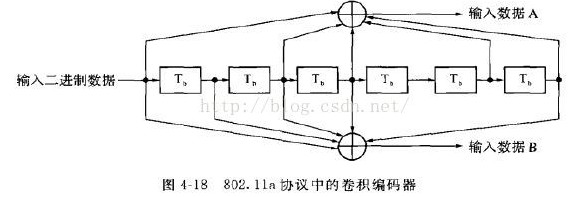

为了缩短卷积编码器设计周期,使硬件设计更具灵活性,在介绍卷积编码器原理的基础上,论述了一种基于可编程逻辑器件,采用模块化设计方法,利用VHDL硬件描述语言实现CDMA2000系统前向链路卷积编码器

2019-08-27 07:41:05

现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操作(在浮点运算中的浮点加法运算几乎占到全部运算操作的一半以上),所以,浮点加法器是现代信号

2019-08-15 08:00:45

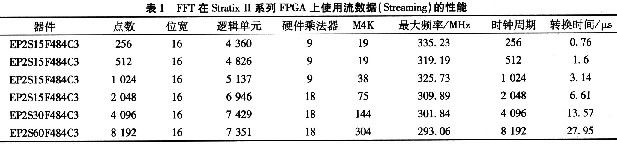

高速连续数据采集系统的背景及功能是什么?如何利用FPGA实现高速连续数据采集系统设计?FPGA在高速连续数据采集系统中的应用有哪些?

2021-04-08 06:19:37

嵌入式测试是什么?如何用FPGA技术去实现嵌入式设计?如何测试FPGA中的高速串行I/O?

2021-04-13 07:03:58

前言FPGA 可以实现高速硬件电路,如各种时钟,PWM,高速接口,DSP计算等硬件功能。这是Cortex-M 处理器软件无法比拟的。要实现FPGA 的逻辑设计,对于嵌入式系统工程师又是比较复杂和具有

2021-12-21 06:13:49

由于卷积码具有较好的纠错性能,因而在通信系统中被广泛使用。采用硬件描述语言VerilogHDL或VHDL和FPGA(FieldProgrammableGateArray——现场可编程门阵列)进行数字通信系统设计,可在集成度、可靠性和灵活性等方面达到比较满意的效果。

2019-10-14 06:02:23

在IPSec协议中认证使用SHA-1和MD5单向散列函数算法实现,通过使用FPGA高速实现SHA-1消息认证算法。

2021-04-13 06:02:01

卷积层实现在上一篇文章中,我解释了卷积层是对图像的过滤过程,但是并没有解释输入输出通道如何处理,过滤时图像的边缘处理等。由于本文旨在实现层面的理解,因此我将详细介绍这些要点。处理 I/O 通道在图像

2023-02-24 15:41:16

本文通过对长BCH码优化方法的研究与讨论,针对标准中二进制BCH码的特性,设计了实现该译码器的FPGA硬件结构。

2021-06-15 09:23:27

本文给出了基于FPGA高速数据采集系统中的输入输出接口的实现,介绍了高速传输系统中RocketIO设计以及LVDS接口、LVPECL接口电路结构及连接方式,并在我们设计的高速数传系统中得到应用。

2021-04-29 06:04:42

结合高速嵌入式数据采集系统,提出一种基于CvcloneⅢ FPGA实现的异步FIFO和锁相环(PLL)结构来实现高速缓存,该结构可成倍提高数据流通速率,增加数据采集系统的实时性。采用FPGA设计高速缓存,能针对外部硬件系统的改变,通过修改片内程序以应用于不同的硬件环境。

2021-04-30 06:19:52

y(n) =x(n)* h(n)上式的运算关系称为卷积运算,式中 代表两个序列卷积运算。两个序列的卷积是一个序列与另一个序列反褶后逐次移位乘积之和,故称为离散卷积,也称两序列的线性卷积。其计算的过程

2012-10-31 22:29:00

,其算法的软件实现方式非常低效,所以业界对GNN的硬件加速有着非常迫切的需求。我们知道传统的CNN(卷积神经网络网络)硬件加速方案已经有非常多的解决方案;但是,GNN的硬件加速尚未得到充分的讨论和研究

2020-10-20 09:48:39

本帖最后由 mr.pengyongche 于 2013-4-30 03:12 编辑

毕业设计_分段卷积MATLAB仿真与DSP实现 常用的线性卷积方法要求两个输入序列的持续时间相同,但在实际

2012-12-25 13:43:20

本文介绍了一种基于FPGA芯片的高速智能节点的硬件结构和软件设计,旨在提高现在LON网络的智能节点的处理能力和通用性。

2021-05-06 08:20:28

本帖最后由 upup11 于 2012-11-21 20:45 编辑

我想请教一个问题:如何用FPGA硬件实现小波变换。 问题的由来:我在做一个不影响语音通信的前提下,电话线感应信号特征提取

2012-11-20 21:35:16

大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、\"行侠仗义\"栏里获取其他感兴趣的资源,或者一起煮酒言欢。

今天

2023-05-25 18:08:24

《数字信号处理》要做课程设计,题目是:线性卷积在DSP芯片上的实现。要求:给出算法原理,写出主程序。

2011-10-08 16:12:58

请问一下高速流水线浮点加法器的FPGA怎么实现?

2021-05-07 06:44:26

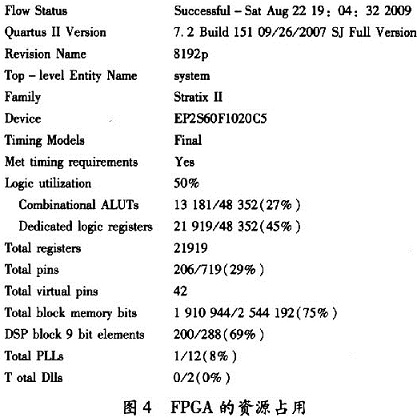

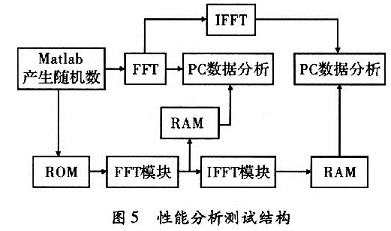

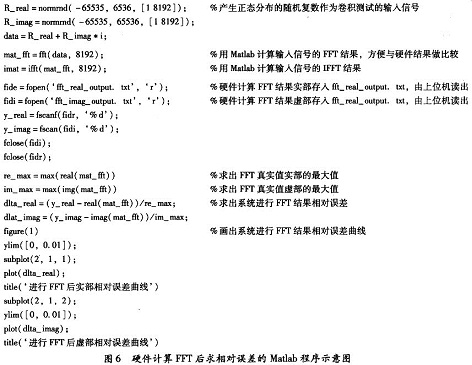

介绍了频域抽取基二快速傅里叶运算的基本原理;讨论了基于FPGA达4 096点的大点数超高速FFT硬件系统设计与实现方法,当多组大点数进行FFT运算时,利用FPGA内部大容量存储资源,采

2009-04-26 18:33:08 26

26 本文介绍了神经网络VLSI硬件实现的基本情况和VerilgHDL硬件设计方法的概念,在此基础上利用FPGA设计出了Kohonen竞争网络硬件电路,其工作频率为33Mhz,并对其工作过程进行了较详细的

2009-06-18 08:49:21 11

11 提出用FPGA 来实现指纹识别算法, 代替了PC 机、通用MCU 或者DSP。算法由硬件来实现, 提高了运算速度。同时具体说明了指纹识别系统的基本原理、系统总体结构、FPGA 模块划分, 以及指

2009-07-22 15:17:27 0

0 本文介绍了一种应用FPGA 器件完成高速数字传输的方法,利用这种方法实现无线收发芯片nRF2401A 的高速数据接口。为进一步提高信息的传输速率,这里还对待传输的数据进行了压缩处

2009-08-04 09:16:20 9

9 本文介绍了一种基于FPGA 的高速多路数据采集系统的设计方案,描述了系统的主要组成及FPGA 的实现方法。在硬件上FPGA 采用ACEX1K100 器件,用于实现A/D 转换器的控制电路、多路

2009-12-19 16:02:33 50

50 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi 译码的实现方案,对译码的各个组成部分作了分析,并在FP

2010-01-06 15:06:59 12

12 介绍AES 算法的原理以及基于FPGA 的高速实现。结合算法和FPGA 的特点,采用查表法优化处理了字节代换运算、列混合运算。同时,为了提高系统工作速度,在设计中应用了内外结合

2010-01-25 14:26:51 29

29 基于FPGA 的LON 网络高速智能节点的设计作者:王传云杨辉 来源:微计算机信息摘要:本文介绍了一种基于FPGA 芯片的高速智能节点的硬件结构和软件设计,旨在提高现在LON 网络的

2010-02-06 12:17:38 16

16 介绍了一种基于新型FPGA的高速数字下变频的实现方法,它充分利用数字下变频的优化算法以及FPGA领域的新技术,去除由于数据速率过高而造成的各种瓶颈,极大地减少了计算量和FPG

2010-07-02 16:49:24 21

21 介绍AES算法的原理以及基于FPGA的高速实现。结合算法和FPGA的特点,采用查表法优化处理了字节代换运算、列混合运算。同时,为了提高系统工作速度,在设计中应用了内外结合的流水线

2010-07-17 18:09:43 44

44 本文探讨了无线通信中广泛涉及的差错控制问题,介绍了卷积码的编译码原理。提出了一种卷积码编码,及其高速Viterbi译码的实现方案,对译码的各个组成部分作了分析,并在FPGA中实现

2010-07-21 17:20:04 22

22 提出了模糊CMAC网络的一种基于FPGA的硬件实现方法。首先,分析了模糊CMAC网络的结构与算法,并以MATLAB仿真为依据,得到模糊CMAC网络的FPGA实现所需的参数;在此基础上,对模糊CMAC

2010-08-09 14:55:03 19

19 为解决目前高速信号处理中的数据传输速度瓶颈以及传输距离的问题,设计并实现了一种基于FPGA 的高速数据传输系统,本系统借助Altera Cyclone III FPGA 的LVDS I/O 通道产生LVDS 信号,稳

2010-11-02 15:27:43 42

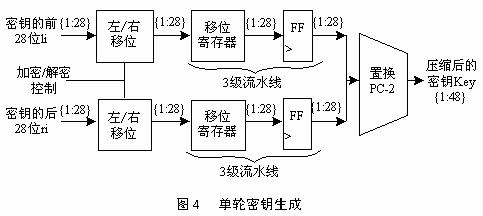

42 摘要:介绍3-DES算法的概要;以Xilinx公司SPARTANII结构的XC2S100为例,阐述用FPGA高速实现3-DES算法的设计要点及关键部分的设计。引 言

2006-03-13 19:36:42 651

651

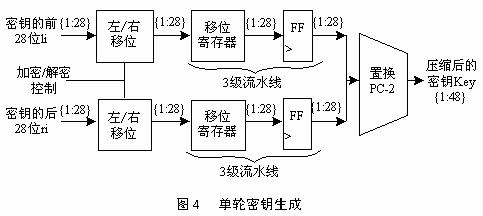

摘要:介绍3-DES算法的概要;以Xilinx公司SPARTANII结构的XC2S100为例,阐述用FPGA高速实现3-DES算法的设计要点及关键部分的设计。

关键词:3-DES

2009-06-20 14:22:00 1317

1317

高速流水线浮点加法器的FPGA实现

0 引言现代信号处理技术通常都需要进行大量高速浮点运算。由于浮点数系统操作比较复杂,需要专用硬件来完成相关的操

2010-02-04 10:50:23 2042

2042

提出了二维模糊CMAC网络的一种基于FPGA的硬件实现方法。首先,分析了模糊CMAC网络的结构与算法,并以Matlab仿真为依据,得到模糊CMAC网络的FPGA实现所需的参数;在此基础上,对模糊CMAC网络进行硬件模块划分,基于VHDL实现了各硬件模块的功能描述,并对模块

2011-03-15 17:19:56 29

29 System Generator 工具由 MathWorks 与 Xilinx 合作开发而成,DSP 设计人员可使用 MATLAB 和Simulink 工具在 FPGA 内进行开发和仿真来完善 DSP 设计。 该工具为系统级 DSP 设计与 FPGA 硬件实现的融合起

2011-05-11 18:36:23 224

224 基于FPGA硬件实现固定倍率的图像缩放,将2维卷积运算分解成2次1维卷积运算,对输入原始图像像素先进行行方向的卷积,再进行列方向的卷积,从而得到输出图像像素。把图像缩放过程

2012-05-09 15:52:04 34

34 TCAM在高速路由查找中的应用及其FPGA实现,TCAM在高速路由查找中的应用及其FPGA实现

2015-11-04 16:32:39 15

15 这是verilog写的可以实现卷积编码1/2码率的代码,附带测试文件0

2016-01-20 18:23:39 1

1 高速专用GFP处理器的FPGA实现,下来看看

2016-05-10 11:24:33 15

15 基于FPGA的高速数据采集硬件系统设计.

2016-05-10 17:06:40 43

43 基于FPGA的高速多通道AD采样系统的设计与实现_徐加彦

2017-01-18 20:23:58 12

12 一种高速卷积编解码器的FPGA实现

2017-02-07 15:05:00 19

19 DSP与FPGA高速的数据传输有三种常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 现场可编程逻辑门阵列) 设计 FIFO的接口电路,即可实现高速互联。

2017-02-11 14:16:10 2487

2487

(Xilinx)FPGA中LVDS差分高速传输的实现

2017-03-01 13:12:04 64

64 采用FPGA实现对AD 输出数据的高速采集

2017-08-30 17:16:02 35

35 基于FPGA的高速DSP与液晶模块接口的实现

2017-10-19 13:46:23 3

3 ,自然语言处理,推荐算法,图像识别等广泛的应用领域。 FPGA云服务器提供了基于FPGA的深度卷积神经网络加速服务,单卡提供约3TOPs的定点计算能力,支持典型深度卷积网络算子,如卷积、逆卷积、池化、拼接、切割等。有效加速典型网络结构如VggNet、GoogLeNet、ResNet等。

2017-11-15 16:56:36 724

724

Verilog HDL硬件描述语言完成其FPGA实现与验证,测试结果表明多速率卷积编码器可以实时地调整码率,高效稳定地进行差错控制,满足L-DACS1 高速传输仍保持稳定的要求,并且用于实际项目中。

2017-11-18 12:26:34 1263

1263

卷积编码是现代数字通信系统中常见的一种前向纠错码,区别于常规的线性分组码,卷积编码的码字输出不仅与当前时刻的信息符号输入有关,还与之前输入的信息符号有关。

2018-08-21 10:26:04 7945

7945

自1955年Elias发明卷积码以来,卷积码作为一种高效的信道编码已被用在许多现代通信系统中。卷积码分为零比特卷积码(Zero Tail CC,简称ZTCC)和咬尾卷积码(Tail Biting

2019-05-03 09:00:00 3784

3784

本文提出了一种实现信号采集方案,介绍了由ARM 处理器S3C2410 和EP2C8 FPGA 组成的高速信号采集系统的系统设计,并着重介绍前端硬件的设计,并就ARM 处理器和FPGA 的互联设计进行探讨。利用FPGA 硬件控制A/D 转换,达到了较好的效果,实现了信号的采集与存储。

2018-11-02 15:46:01 10

10 卷积神经网络是一类包含卷积计算且具有深度结构的前馈神经网络,是深度学习的代表算法之一 。卷积神经网络具有表征学习能力,能够按其阶层结构对输入信息进行平移不变分类,因此也被称为“平移不变人工神经网络” 。

2019-11-25 07:04:00 2030

2030 卷积神经网络仿造生物的视知觉(visual perception)机制构建,可以进行监督学习和非监督学习,其隐含层内的卷积核参数共享和层间连接的稀疏性使得卷积神经网络能够以较小的计算量对格点化

2019-11-14 07:10:00 1640

1640 目前在做FPGA移植加速CNN卷积神经网络Inference相关的学习,使用的是Xilinx公司的ZYNQ-7000系列的FPGA开发板,该博客为记录相关学习内容,如有问题欢迎指教。前面已经介绍

2020-12-25 17:34:36 22

22 本文档的主要内容详细介绍的是如何使用Xilinx的FPGA对高速PCB信号实现优化设计。

2021-01-13 17:00:59 25

25 在电子设计中,由于现场可编程门阵y~J(FPGA)的高逻辑密度和高可靠性以及用户可编程性,受到了广大硬件工程师的青睐。用FPGA来实现某些专用电路,可使整个设计更加紧凑、更小巧、灵活、稳定、可靠

2021-01-15 15:27:00 9

9 针对高速率QPSK数据传输链系统,比较分析了数字中频接收与零中频接收的优、缺点,并提出了一种基于多相滤波的宽带中频正交采样数字零中频接收方案。基于FPGA对此数字零中频正交变换方案进行了实现和验证,同时,对一种全数字零中频QPSK信号的高速解调算法及其FPGA硬件实现进行了介绍。

2021-03-19 17:43:12 11

11 功能.文中将软硬件实现的顺序形态图像处理图片在处理效果和速度两个方面作了比较.算法在FPGA芯片上的高速实现特征使数学形态学在图像实时处理领域的应用成为可能。

2021-04-01 11:21:46 8

8 Xilinx zynq系列FPGA实现神经网络评估 本篇目录 1. 内存占用 1.1 FPGA程序中内存的实现方式 1.2 Zynq的BRAM内存大小 1.3 一个卷积操作占用的内存 2.

2021-04-19 11:12:02 2202

2202

基于FPGA的RBF神经网络硬件实现说明。

2021-04-28 11:24:23 25

25 当前,卷积神经网络已在图像分类、目标检测等计算机视觉领域被广泛应用。然而,在前向推断阶段许多实际应用往往具有低延时和严格的功耗限制。针对该问题,采用参数重排序、多通道数据传输等优化策略,设计并实现

2021-05-28 14:00:22 23

23 基于FPGA的神经网络硬件实现方法说明。

2021-06-01 09:35:16 37

37 电子发烧友网站提供《在FPGA上构建EVM硬件的实现.zip》资料免费下载

2023-06-26 11:50:49 0

0 电子发烧友网站提供《基于FPGA的RBF神经网络的硬件实现.pdf》资料免费下载

2023-10-23 10:21:25 0

0

电子发烧友App

电子发烧友App

评论