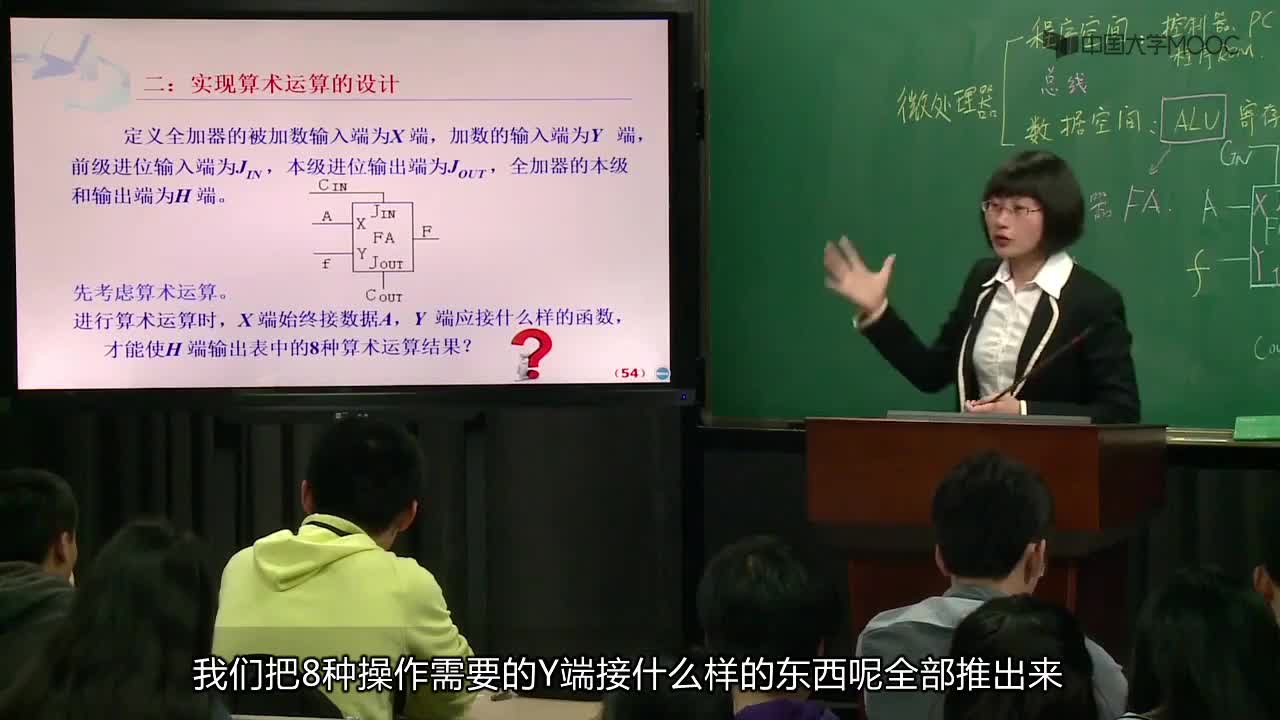

组合逻辑电路实验实验三 组合逻辑电路一、 实验目的1、 掌握组合逻辑电路的功能测试2、 验证半加器和全加器的逻辑功能3、 学会

2009-03-20 18:11:09

做任何模块前,要确定输入输出端口有哪些,有一个整体的概念;方便以后模块调用;

2023-10-10 14:10:56 86

86

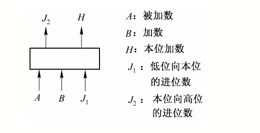

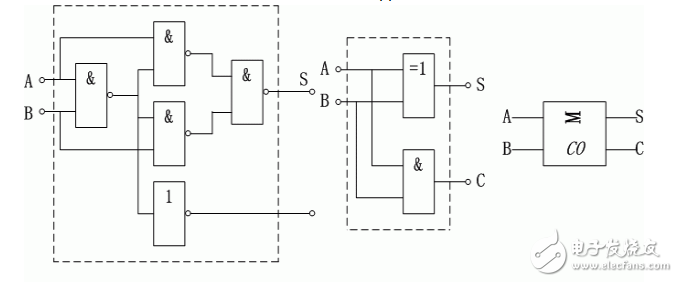

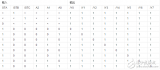

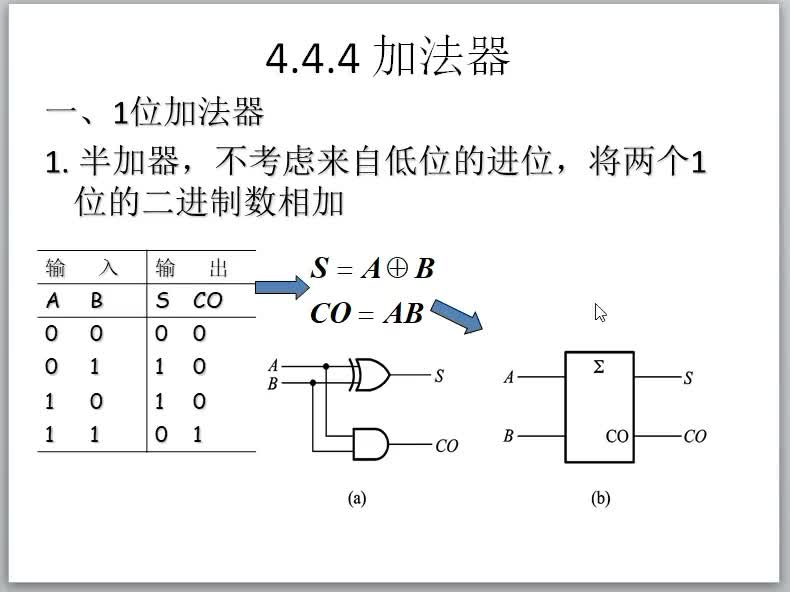

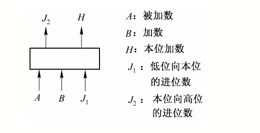

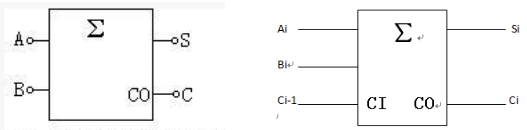

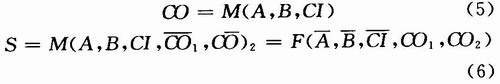

按照半加器和全加器的真值表写出输出端的逻辑表达式,对半加器,输出的进位端是量输入的“与”,输出的计算结果是量输入的异或;对全加器,也按照逻辑表达式做。

2023-06-25 17:38:51 451

451

电子发烧友网站提供《在Spartan 6 FPGA上从头开始实现全加器.zip》资料免费下载

2023-06-15 10:13:28 0

0 大家好!今天给大家分享的是4位全加器的代码以及仿真程序。俗话说:“千里之行,始于足下。”对于初学者来说, 加法器是fpga初学者入门必须掌握的内容。我们很多朋友在入门时囫囵吞枣,一些基础的东西没有

2023-05-23 10:00:10 761

761

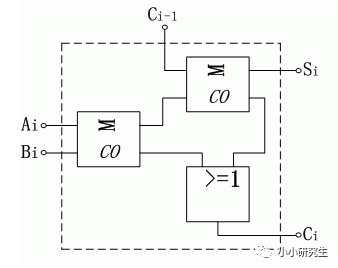

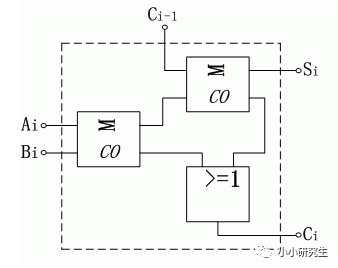

首先半加器是A+B构成了{C,S}。由于全加器多了一个低位的进位,就是将{C,S}再加上Ci-1。

2023-05-22 15:26:35 583

583

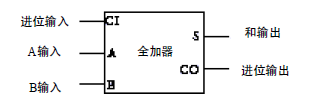

在上一节半加器中,介绍了全加器可看作两个半加器和一个或门组成。

2023-05-14 15:07:47 837

837

Verilog数字系统设计四复杂组合逻辑实验2文章目录Verilog数字系统设计四前言一、什么是8位全加器和8为带超前进位的全加器?二、编程1.要求:2.门级原语实现8位全加器:3.门级原语实现带

2021-12-05 19:06:10 4

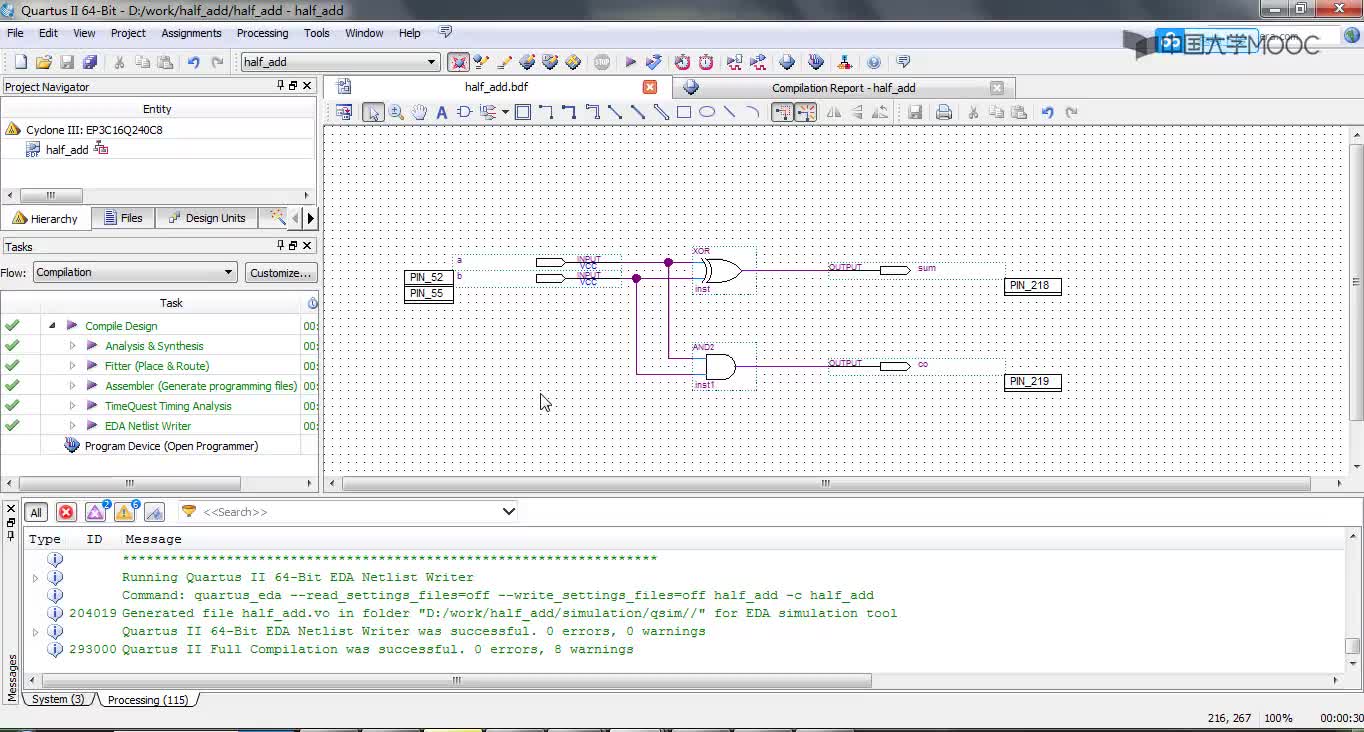

4 过1位全加器的详细设计,掌握原理图输入以及Verilog的两种设计方法。

2021-11-03 12:51:07 8

8 多思计算机组成原理网络虚拟实验系统计算机组成原理实验一全加器实验

2021-10-22 10:36:12 11

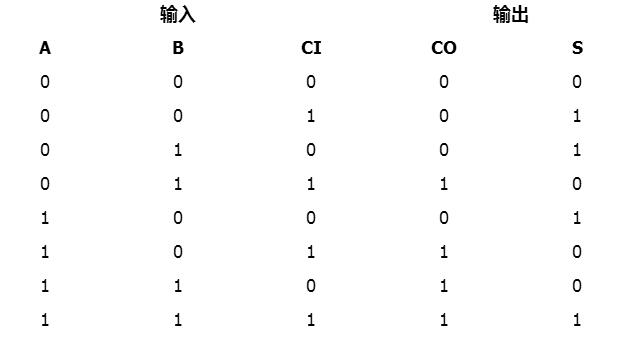

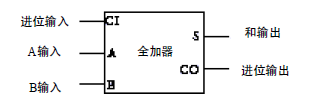

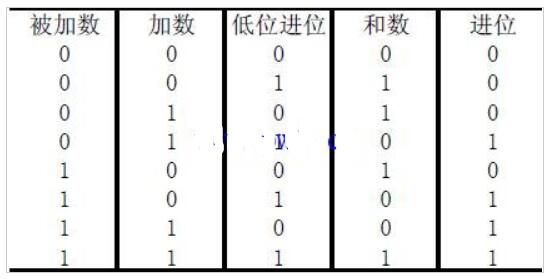

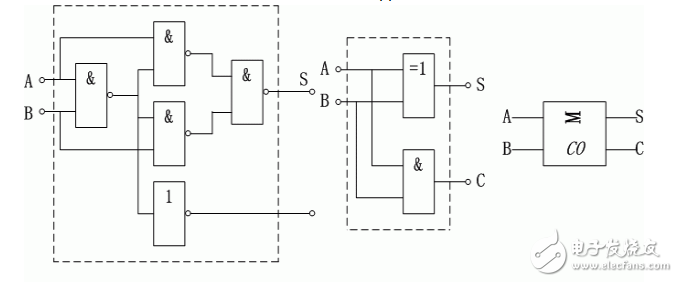

11 全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,多个一位全加器进行级联可以得到多位。全加器是形成三位算术和的组合电路,它由三个输入和两个输出组成。

2021-06-29 09:14:46 53586

53586

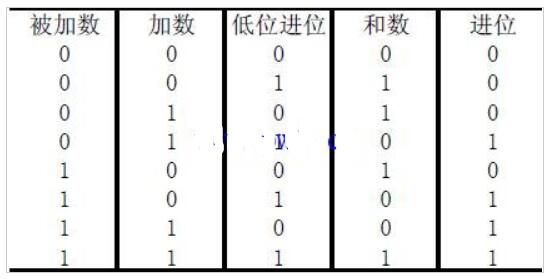

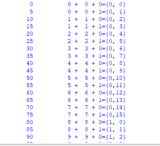

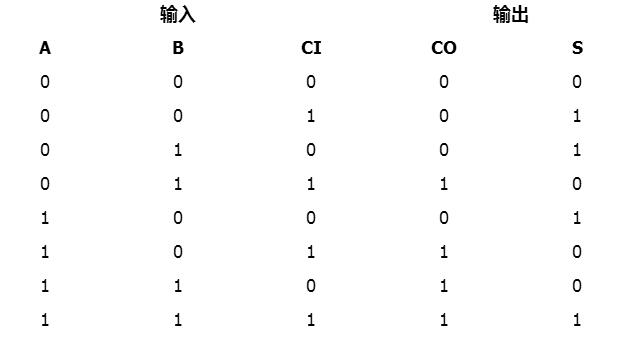

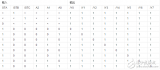

全加器能进行加数、被加数和低位来的进位信号相加,并依据求和作用给出该位的进位信号。依据它的功用,能够列出它的真值表,如表1.2所示。

2021-02-18 14:33:09 52382

52382

主要内容:设计一个一位的全加器,从真值表开始,介绍门级实现,然后形成电路图,对功能进行仿真验证,最后再用行为级描述实现全加器功能,二者形成对比。把 Verilog 代码,硬件电路,仿真波形三者对应起来。

2020-12-10 15:00:32 6

6 个四位串行加法器由4个全加器构成。全加器是串行加法器的子模块,而全加器是由基本的逻辑门构成,这些基本的逻辑门就是所说的叶子模块。这个设计中运用叶子模块(基本逻辑门)搭建成子模块(全加器),再用子模

2020-12-09 11:24:30 27

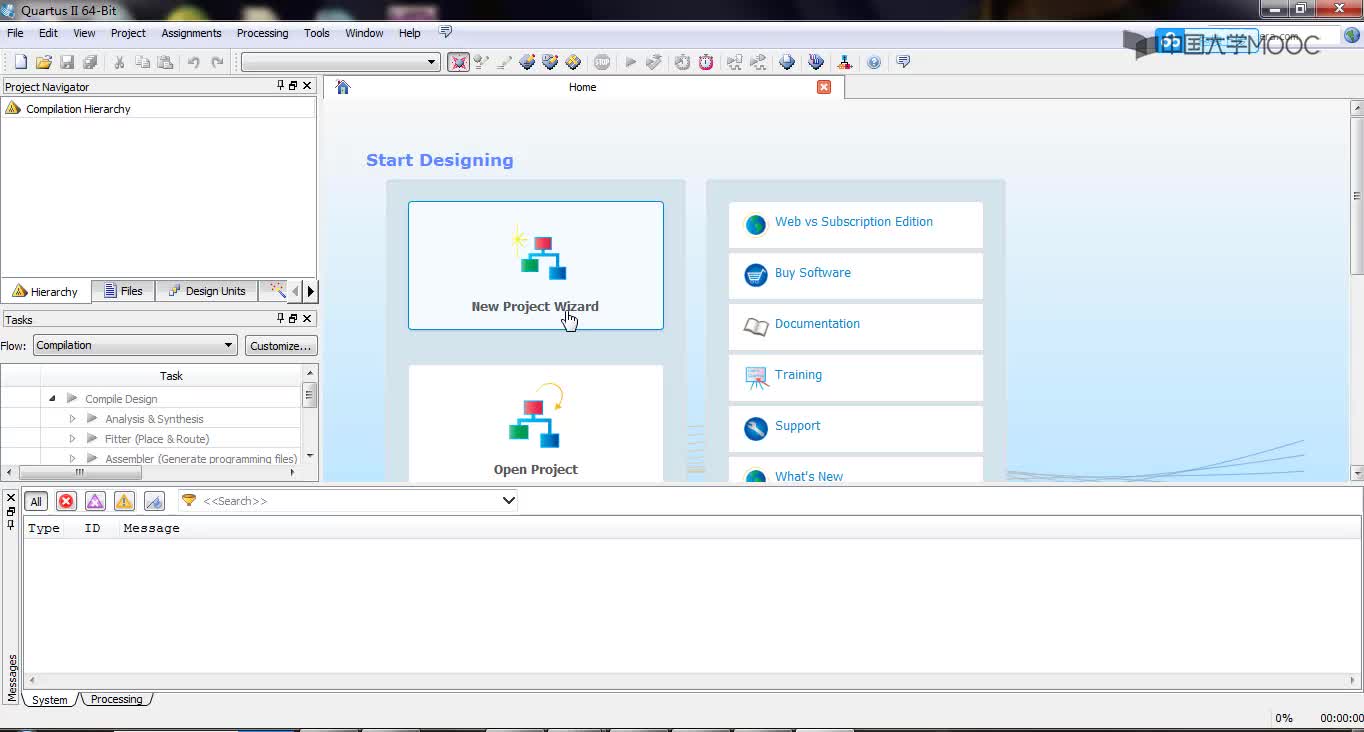

27 通过此实验了解FPGA 开发软件Quartus II 的使用方法及VHDL 的编程方法,学习用VHDL 语言来描述1 位全加器及电路的设计仿真和硬件测试。

2020-12-02 16:34:48 12

12 全加器的输入端有三个,分别为A、B、C(低位的进位);两个输出S(和);C(运算产生的进位)。

2020-04-23 09:59:42 96058

96058

本文主要介绍了全加器逻辑表达式及全加器的逻辑功能。

2020-04-23 09:51:14 105979

105979

全加器是数字信号处理器微处理器中的重要单元,它不仅能完成加法,还能参与减法、乘法、除法等运算,所以,。提高全加器性能具有重要意义。本文分析了两种普通全加器,运用布尔代数对全加器和的数、进位函数进行

2019-07-03 17:11:16 38

38 本文档的主要内容详细介绍的是VHDL语言设计的全加器源代码和工程文件免费下载。

2019-06-03 08:00:00 4

4 电子发烧友网为你提供()MC14008B相关产品参数、数据手册,更有MC14008B的引脚图、接线图、封装手册、中文资料、英文资料,MC14008B真值表,MC14008B管脚等资料,希望可以帮助到广大的电子工程师们。

2019-04-18 21:54:09

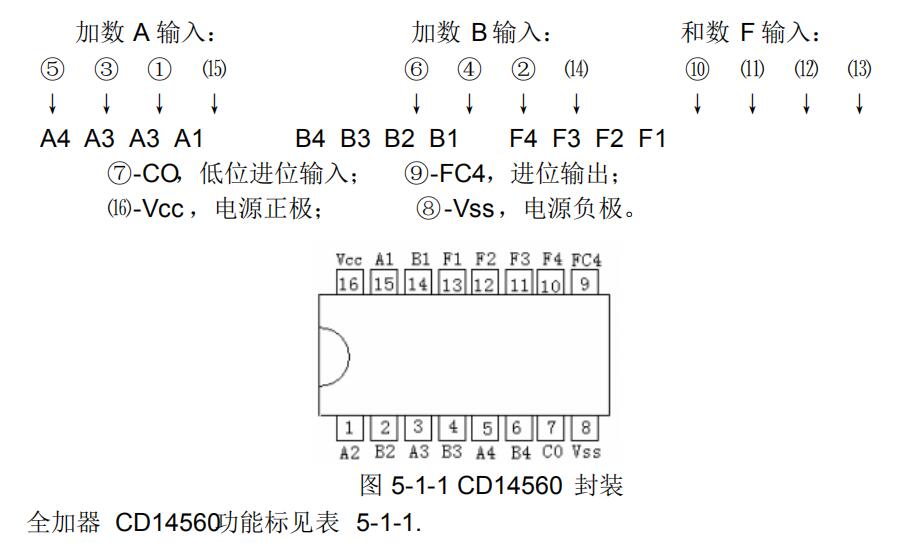

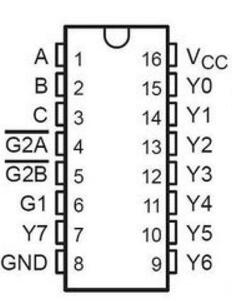

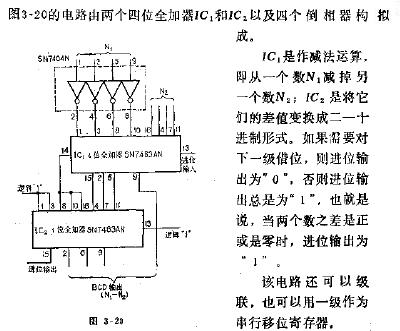

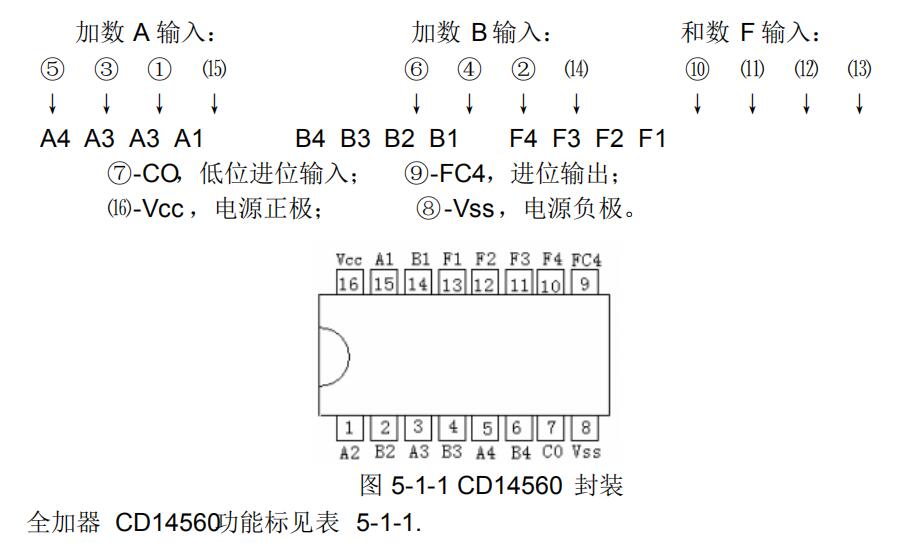

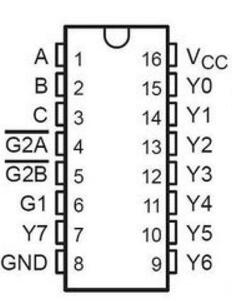

全加器 CD14560的工作原理 CD14560 是一块十进制全加速集成电路,为 16 脚双列直插封装结构,可以完成一位十进制数的全加运算。输入、输出都是 BCD码中的自然数,称为 NBCD全加速。如图 5-1-1 所示为 CD14560全加速的封装。

2018-12-20 18:16:04 4157

4157

本文档的主要内容详细介绍的是74LS153利用双四选一数据选择器实现全加器的电路图资料免费下载。

2018-11-26 08:00:00 502

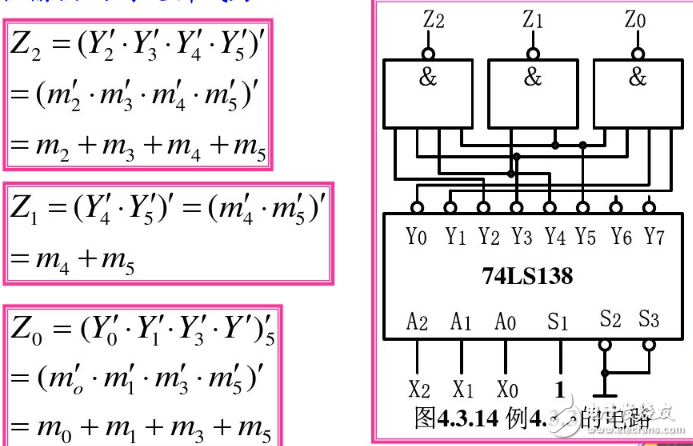

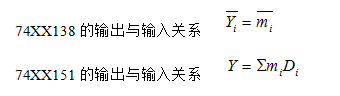

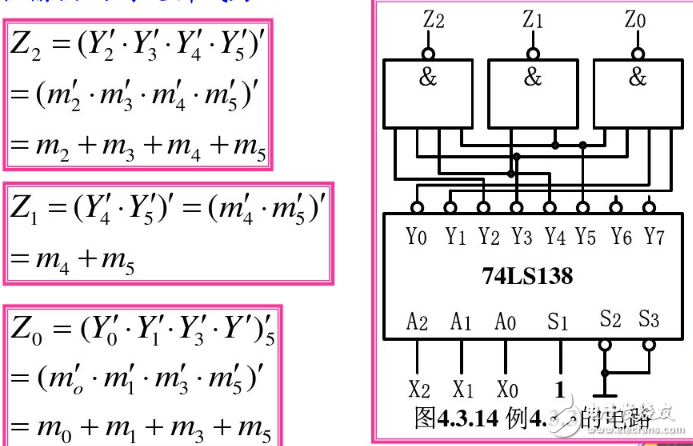

502 上图中所使用的74LS138和74HC138两者功能一样,74HC138采用高速CMOS工艺制作,自身功耗低,输出高低电平范围宽。

2018-08-07 16:50:19 108764

108764

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

2018-07-25 16:03:28 73110

73110 全加器是一个能够完成一位(二进制)数相加的部件。我们先来看一下两个二进制数的加法运算是怎样进行的。

2018-07-25 15:48:44 67834

67834

计算机最基本的任务之一是进行算数,在机器中四则运算——加、减、乘、除——都是分解成加法运算进行的,因此加法器便成为计算机中最基本的运算单元。

2018-07-25 15:14:09 37176

37176

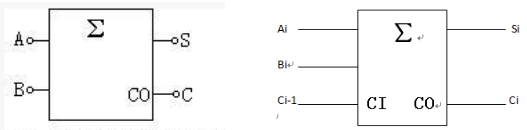

实际上,一个完整的加法器的输入端有3个:A、B和低位的进位结果CI。

2018-07-25 14:52:06 37006

37006

半加器、全加器是组合电路中的基本元器件,也是CPU中处理加法运算的核心,理解、掌握并熟练应用是硬件课程的最基本要求。

2018-07-25 14:39:45 130197

130197

半加器+半加法和全加法是算术运算电路中的基本单元,它们是完成1位二进制相加的一种组合逻辑电路。

2018-07-25 11:37:16 321963

321963

加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器。

2018-07-25 11:15:53 65775

65775

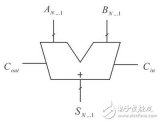

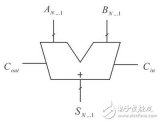

N位全加器将{AN,……,A1}、{BN,……,B1}和进位输入Cin作为输入,计算得到和{SN,……,S1}以及最高位的进位输出Cout(见图1)。每一位得到的和与进位输出都直接受其上一位的影响,其进位输出也会影响下一位。最终,整个全加器的和与输出都受进位输入Cin的影响。

2018-06-08 10:24:00 3995

3995

本文主要详解四位全加器74ls83,首先介绍了74ls83特点及引脚图、真值表,其次介绍了74ls83功能表、典型参数及逻辑图,最后介绍了74ls83推荐工作条件、电性能以及74ls83交流(开关)参数,具体的跟随小编一起来了解一下。

2018-05-31 09:12:06 91346

91346

本文主要介绍了74ls151应用电路图大全(全加器\表决器)。五人表决器,只要赞成人数大于或等于三,则表决通过。因此,只需将每位表决人的结果相加,判断结果值。设五个开关A、B、C、D、E作为表决器

2018-05-07 11:38:47 99110

99110

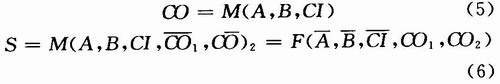

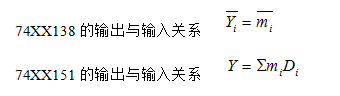

本文主要介绍了用74ls151实现全加器设计电路。根据全加器的定义可知:输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。输出为:S,Co,其中S为本位和数,Co为高位进位数。其逻辑关系为:S=A⊕B⊕Ci;Co=AB+(A⊕B)Ci。

2018-05-07 09:52:22 106645

106645

本文主要介绍了五款74ls138的应用电路图。其中包括了74ls138全加器电路、74ls138抢答器电路、74ls138实现逻辑函数、74ls138全减器电路以及与74LS20组合的三人表决器电路。

2018-05-04 10:31:55 87718

87718

8位全加器可由2个4位的全加器串联组成,因此,先由一个半加器构成一个全加器,再由4个1位全加器构成一个4位全加器并封装成元器件。加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接最高位的输出即为两数之和。

2017-11-24 10:01:45 27671

27671

引言 在全加器设计中运用PG逻辑是非常普遍的,本文在设计和研究全加器时,根据现有的PG逻辑公式推导出了一种新的逻辑公式,并论证了两者之间的等价关系。这一新的公式能够指导全加器设计中的连线方式,灵活

2017-11-06 11:49:57 0

0 用两片74LS138设计一个全加器。在考虑到74LS138译码器为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其74LS138工作原理为:当一个选通端

2017-10-31 15:53:34 137363

137363

一种基于互补型单电子晶体管的全加器电路设计

2017-02-07 16:14:56 8

8 电子类基础芯片资料,很好的手册,工程师必备资料。

2016-05-31 15:42:56 9

9 FPGA学习的好资料,很实用的FPGA教程文档,快来学习吧。

2016-05-12 14:05:52 23

23 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 14:17:45 56

56 FPGA学习资料,有兴趣的同学可以下载看看。

2016-04-07 14:04:26 18

18 实验五 全加器、译码器及数码显示电路 一、实验目的 1、掌握全加器逻辑功能,熟悉集成加法器功能及其使用方法。 2、掌握用七段译码器和七段数码管显示十进制数的方法。 3、掌握

2012-07-16 23:01:22 37

37 加法运算是数字系统中最基本的算术运算。为了能更好地利用加法器实现减法、乘法、除法、码制转换等运算,提出用Multisim虚拟仿真软件中的逻辑转换仪、字信号发生器、逻辑分析仪

2011-05-06 15:55:07 82

82 O 引言 加法运算是算术运算中最基本的运算。减法、乘法、除法及地址计算这些基于加法的运算已广泛地应用于超大规模集成电路(VLSI)中。全加器是组成二进

2010-10-19 10:57:22 5079

5079

基于单电子晶体管的I-V特性和传输晶体管的设计思想,用多栅单电子晶体管作为传输晶体管,设计了一个由5个SET构成的全加器,相对于静态互补逻辑设计的全加器,本文设计的全加器在器

2010-07-30 16:54:22 18

18 摘要:应用CMOS电路开关级设计技术对超前进位全加器进行了设计,并用PSPICE模拟进行了功能验证.与传统门级设计电路相比,本文设计的超前进位电路使用了较少的MOS管,并能保持

2010-05-28 08:18:20 25

25 什么是一位全加器,其原理是什么

加器是能够计算低位进位的二进制加法电路

一位全加器由2个半加

2010-03-08 17:13:33 72422

72422 全加器,全加器是什么意思

full-adder 用门电路实现两个二进数相加并求出和的组合线路,称为一个全加器。

2010-03-08 17:04:58 78218

78218

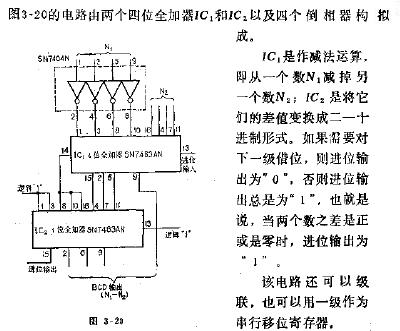

用四位全加器构成二一十进制加法器

2009-04-09 10:34:43 5490

5490

用两个全加器构成二一十进制相减器

2009-04-09 10:34:19 739

739

CC4008中文资料:型由具有段间快速超前进位的4个全加器段组成。

2008-04-07 22:27:03 32

32

54/742834 位二进制超前进位全加器简要说明:283为具有超前进位的 4 位全加器,共有 54/74283,54/74S28

2008-03-15 09:23:23 441

441

电子发烧友App

电子发烧友App

评论