Abstract

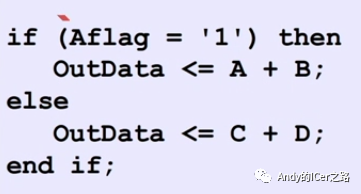

在Verilog中,always block可以用來代表Flip-Flop, Combination Logic與Latch,本文比較在不寫else下,always block所代表的電路。

Introduction

在C語言裡,省略else只是代表不處理而;已但在Verilog裡,省略else所代表的是不同的電路。

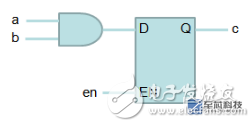

always@(a or b or en)

if (en)

c = a & b;

在combination logic中省略else,由於必須在~en保留原本的值,所以會產生latch。

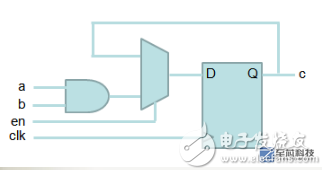

always@(posedge clk)

if (en)

c <= a & b;

雖然也必須在~en保留原本的值,但由於flip-flop就有記憶的功能,所以不會產生latch。if將產生mux,並將flip-flop的值拉回給mux。

Conclusion

在Verilog中,雖然只是小小的差異,但結果卻有天大的差異。

全文完。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1602文章

21320浏览量

593173

发布评论请先 登录

相关推荐

Verilog实现uart串口设计

;// Output parity bit.

else

tx <= tsr[0];//Shift out data bit.

end

end

always @(posedge mclkx16

发表于 04-01 14:41

verilog实现卷积运算

else begin

data_a_reg <= data_in_a;

data_b_reg <= data_in_b;

end

end

// 执行卷积运算

always

发表于 03-26 07:51

verilog语音实现浮点运算

Verilog可以通过使用IEEE标准的浮点数表示来实现浮点运算。下面是一个基本的Verilog模块示例,展示了如何进行加法、乘法和除法等常见的浮点运算操作:

module

发表于 03-25 21:49

assign语句和always语句的用法

Assign语句和Always语句是在硬件描述语言(HDL)中常用的两种语句,用于对数字电路建模和设计。Assign语句用于连续赋值,而Always语句用于时序逻辑建模。本文将详细探讨这两种语句

ZCC4650雙通道 25A 或單通道50A 稳压器替代LT4650

特 點

■ 雙通道 25A 或單通道 50A 輸出■ 輸入電壓範圍:4.5V 至 15V■ 輸出電壓範圍:0.6V 至 1.8V■ 在整個電壓、負載和溫度範圍內具有 ±1.5% 的最大

发表于 01-15 17:56

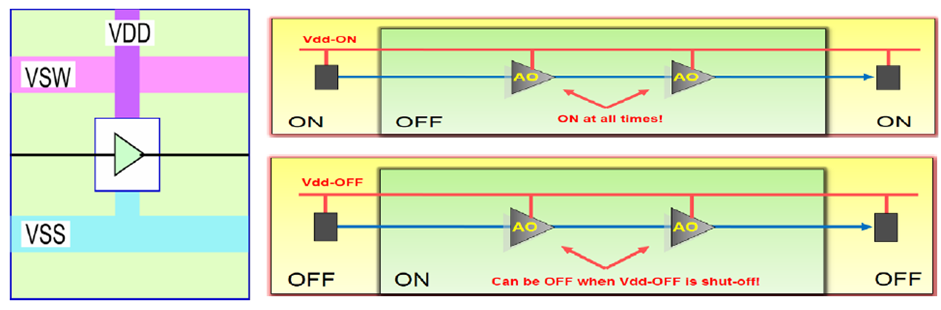

什么是always on buffer?什么情况下需要插always on buffer?

相比普通的buffer cell,always on buffer(AOB)有secondary always on pin,可以让AOB即使在primary power off的情况下保持on的状态;AOB在secondary pg pin off的情况下也是off的。

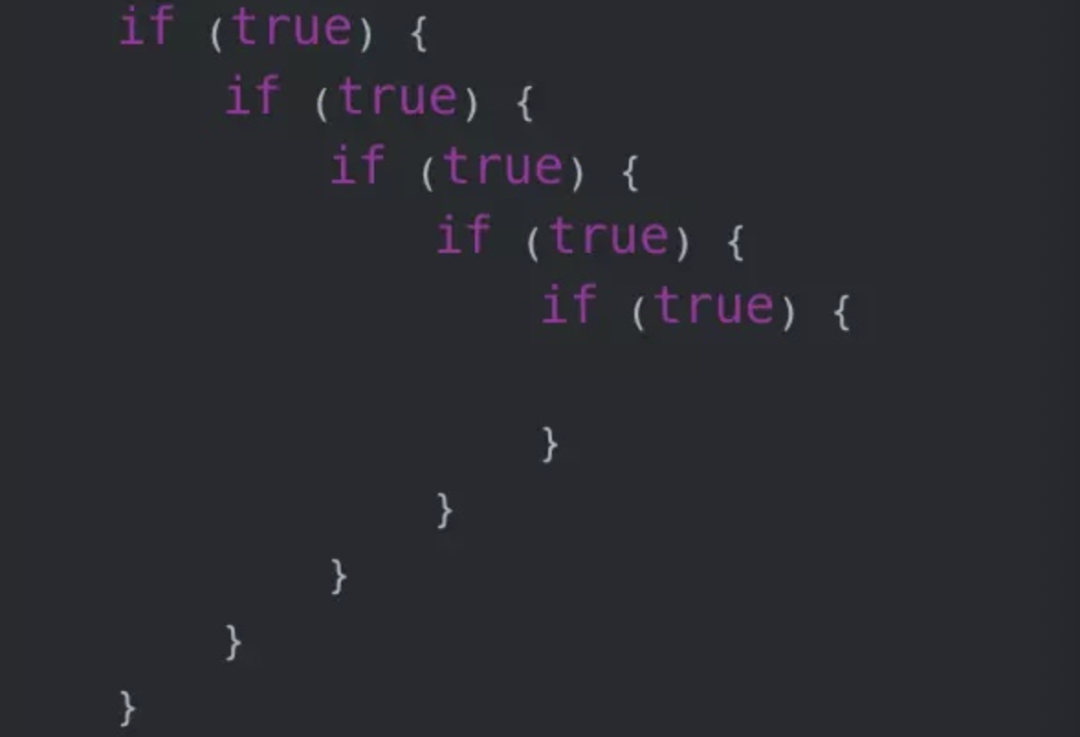

Verilog代码:if-else和case的电路结构和区别

每个if-else就是一个2选1mux器。当信号有明显优先级时,首先要考虑if-else,但是if嵌套过多也会导致速度变慢;if语句结构较慢,但占用面积小。

嵌套的if语句如果使用不当,就会

SystemVerilog相比于Verilog的优势

我们再从对可综合代码的支持角度看看SystemVerilog相比于Verilog的优势。针对硬件设计,SystemVerilog引入了三种进程always_ff,always

如何解决冗长的if...else条件判断(上)

if...else...条件语句我相信学习python的童鞋们都喜欢用,例如下一面这一段 def func ( param ): if param == "cat" : print ( "这是一只

代码如何优化掉多余的if/else?

的if/else? 1. 提前 return 这是判断条件取反的做法,代码在逻辑表达上会更清晰,看下面代码: if (condition) { // do something} else { return xxx

FPGA设计中 Verilog HDL实现基本的图像滤波处理仿真

带来FPGA设计中用Verilog HDL实现基本的图像滤波处理仿真,话不多说,上货。

1、用matlab代码,准备好把图片转化成Vivado Simulator识别的格式,即每行一个数

发表于 06-07 14:48

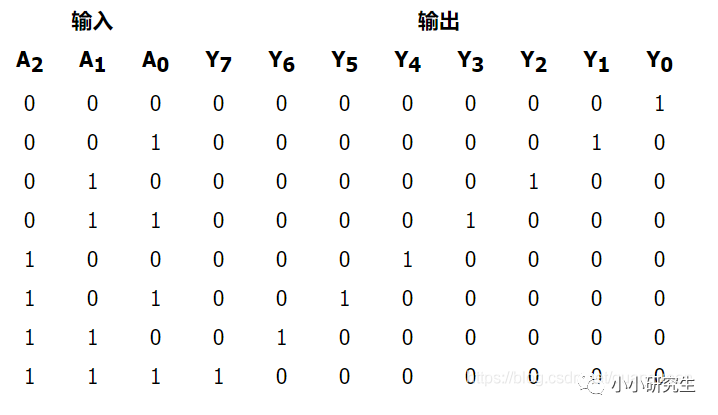

always组合逻辑块的讲解和译码器的实现

always 语句是重复执行的。always 语句块从 0 时刻开始执行其中的行为语句;当执行完最后一条语句后,便再次执行语句块中的第一条语句,如此循环反复。

Verilog中的If语句和case语句介绍

我们在上一篇文章中已经看到了如何使用程序块(例如 always 块来编写按顺序执行的 verilog 代码。

我们还可以在程序块中使用许多语句来控制在我们的verilog设计中信号赋值的方式

always block內省略else所代表的電路 (SOC) (Verilog)

always block內省略else所代表的電路 (SOC) (Verilog)

评论