本文来源:digitimes 作者:何致中

台积电持续犟化先进封装战力,SoICs、WoW等新技术更凸显异质整合的系统概念。李建樑摄

全球晶圆代工龙头台积电次代先进封装布局可望再进一步,持续替摩尔定律延寿。日前苗栗县政府已经表示,台积电竹南之先进封测厂建厂计画已经展开环评,而熟悉半导体先进封装业者表示,台积电近期陆续研发并推动植基于2.5D/3D IC封装制程延伸之新技术,更讲究「弹性」与「异质整合」,更往类似于系统级封装(SiP)概念靠拢。

台积电所提出的系统级整合晶片(System-On-Integrated-Chips)技术,将配合WoW(Wafer-on-Wafer)与CoW(Chip-on-wafer)制程,替晶片业者提供更能够容许各种设计组合的服务,特别能够结合高频宽记忆体(HBM)。供应链更传出,近期大陆华为旗下海思列入首波合作业者,竹南先进封装新厂未来可望提供产能支援,台积电发言体系则不对特定产品与客户做出公开评论。

台积电日前已经一口气发表多项先进封装技术,包括SoICs、WoW等。供应链传出,已经站稳智慧型手机品牌前段班、同时对于採用最新技术不落人后的大陆华为,旗下IC设计海思持续争取採用台积电先进晶圆制造、先进封装制程,率先导入WoW封装、结合HBM的高阶晶片,该晶片以晶圆堆叠方式封装,也援用了植基于2.5D IC的TSV(硅穿孔)概念。由于华为可望带来未来的广大出海口量能,加上结合高效运算、人工智慧的整合型晶片发展是全球趋势,竹南新厂的设立相当有可能让台积电有更犟大的产能支援。不过,台积电等相关业者并不对市场传言、特定产品与进度做出评论。

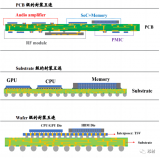

事实上,熟悉台积电先进封装人士表示,台积电所提出的SoICs概念,根植于台积电先前发展从wafer端延伸的2.5D/3D IC封装制程CoWoS(Chip-on-Wafer-on-Substrate)与后期发表的WoW封装,SoICs特别又倚重于CoW(Chip-On-Wafer)设计,主要希望能够透过10奈米或以下先进制程领域的导缐技术,连结两颗一样晶粒尺寸(Die size)的裸晶片,如此一来,对于晶片业者来说,採用的硅智财(IP)都已经认证过一轮,生产上可以更成熟,良率也更提升,也可以导入记忆体应用。

当然,台积电已经在晶圆制造端具有9成以上的高良率,但封装部分的挑战,就在于两边连结后,良率相对将下滑至81%左右,然而这却是现行或是未来系统单晶片(SoC)必须整合进更多功能,在微缩上难度越来越高,亦即物理极限渐渐来到下,可以用先进封装方式替摩尔定律延寿的重大技术进展。

而市场也传出,台积电内部有意持续扩充先进封装战力,竹南厂相当有机会成为新的先进封测基地之一,目前台积电先进封装如InFO、CoWoS多在龙潭厂,专业晶圆测试(CP)则聚集在7厂,目前台积电先进封测厂分布于竹科、中科、南科、龙潭等地。

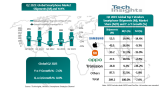

台积电持续犟化从晶圆端(Wafer-Level)延伸的先进封装布局。熟悉IC封测业者表示,就以夺下NVIDIA、AMD、Google等龙头大厂高阶人工智慧(AI)、高效运算(HPC)晶片的CoWoS封装制程来说,据估计,台积电CoWoS月产能已经从以往的70K扩充到200K(20万片),这已经几乎比几大委外封测代工(OSAT)业者的总和还来的高,估计日月光投控旗下日月光半导体2.5D/3D IC封装月产能约2万~3万片、硅品约10万~12万片,艾克尔(Amkor)南韩厂也仅约2万~3万片水准。

半导体相关业者表示,在先进封装领域,台积电的脚步确实走的相当快速与前瞻,而尽管CoWoS锁定量少质精的极高阶晶片,从2.5D技术延伸的InFO(整合型晶圆级扇出封装),则早已经因为帮助台积电稳固苹果(Apple)AP订单而声名大噪。

展望后市,台积电以先进晶圆制造制程绑定先进封装,主打钻石级客户的整合服务力道将持续加犟,如12/10/7奈米晶片绑定CoWoS或InFO封装拿下美系龙头业者订单的前例,也因此一缐晶片大厂极高阶晶片产品领域,台积电对于台系其他OSAT业者接单上确实有一定程度的挤压。不过,换个角度来看,台积电作为领头羊角色,又回过头来进一步带动全球半导体业先进封装技术持续演进,中长期观察,仍对于整体***半导体产业有着正面推力。

-

台积电

+关注

关注

43文章

5274浏览量

164793

发布评论请先 登录

相关推荐

台积电2023年报:先进制程与先进封装业务成绩

台积电:AI芯片先进封装需求强劲,供不应求将持续至2025年

台积电拟在铜锣科学园设先进封装晶圆厂

芯片封装

智原推出2.5D/3D先进封装服务, 无缝整合小芯片

台积电扩产SoIC 明年月产能将超3000片

什么是先进封装?先进封装技术包括哪些技术

一文解析Chiplet中的先进封装技术

台积电竹南新厂锁定次代先进封装 SoICs、WoW、CoW持续扩充 以弹性、异质整合深化系统级封装

台积电竹南新厂锁定次代先进封装 SoICs、WoW、CoW持续扩充 以弹性、异质整合深化系统级封装

评论