声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx

+关注

关注

70文章

2121浏览量

119373 -

Vivado

+关注

关注

18文章

790浏览量

65093

发布评论请先 登录

相关推荐

CYT4BF8CES的SPI通信的SDL中,Slave模式的High level如何修改发送的数据?

英飞凌CYT4BF8CES的SPI通信的SDL中,Slave模式的High level如何修改发送的数据?目前只有初始化buffer能够成功发送,中间如果修改buffer会进中断并且报bus error。

发表于 02-01 07:59

什么是Logic Synthesis?Synthesis的流程

什么是Logic Synthesis?Logic Synthesis用于将输入的高级语言描述(如HDL、verilog)转换为门级电路的网络表示。

Vivado设计套件用户:使用Vivado IDE的指南

电子发烧友网站提供《Vivado设计套件用户:使用Vivado IDE的指南.pdf》资料免费下载

发表于 09-13 15:25

•5次下载

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(4)

(High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx 可编程逻辑器件进行开发,可加速算法开发的进程,缩短

发表于 08-24 14:54

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(3)

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。

Xilinx Vivado HLS (High-Level

发表于 08-24 14:52

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(1)

。

Xilinx Vivado HLS (High-Level Synthesis,高层次综合) 工具支持将 C 、C++等语言转化成硬件描述语言,同时支持基于 OpenCL 等框架对 Xilinx

发表于 08-24 14:40

e² studio 集成开发环境 用户手册: Getting Started Guide

e² studio 集成开发环境 用户手册: Getting Started Guide

发表于 07-10 19:53

•0次下载

e² studio 集成开发环境 用户手册: Getting Started RENESAS MCU RZ Family Rev.1.02

e² studio 集成开发环境 用户手册: Getting Started RENESAS MCU RZ Family Rev.1.02

发表于 07-04 20:13

•0次下载

如何创建一个high-level和object-oriented的模型

UVM register layer classes用于为DUV中的memory-mapped寄存器和内存的read/write操作创建一个 high-level 和 object-oriented

DeepSpeed安装和使用教程

本文翻译了 Getting Started 和 Installation Details 和 CIFAR-10 Tutorial 三个教程,可以让新手安装和简单使用上 DeepSpeed 来做模型训练。

如何在Post Synthesis工程中加入XCI文件

是创建并定制 IP,生成这些 IP 的 output product (包括 IP 的 dcp);然后把第三方生成的网表文件和 IP XCI 的相关文件都加到 Vivado 的 post-synthesis 工程中。

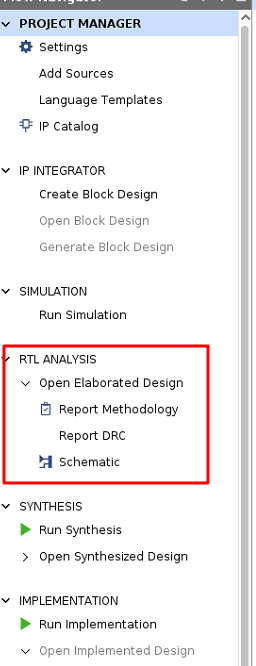

简述Vivado中的Elaborate的作用

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。

Getting Started with Vivado High-Level Synthesis

Getting Started with Vivado High-Level Synthesis

评论