声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx

+关注

关注

70文章

2119浏览量

119368 -

PlanAhead

+关注

关注

0文章

13浏览量

9695

发布评论请先 登录

相关推荐

NUCLEO - H563ZI配置了usart3作为串口,始终接收不到数据是为什么?

我按照规格书配置了usart 3 作为串口,并且电脑可以是被到串口,但是我始终接收不到数据。

并且我还直接接到了串口输出脚PD8 PD9(排除外部连接错误导致的),任然没有数据。

1、确认引脚

发表于 03-14 06:26

在Vivado Synthesis中怎么使用SystemVerilog接口连接逻辑呢?

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接口看作是多个模块共有的引脚集合。

如何通过I2C协议从PSoC™ Creator到Esclipse IDE ModusToolbox™实现和配置引导加载程序?

!w2e3r4t5y6u7i8o9p0||/t5/PSoC-4/PSoC4100Sp-CY8C4147AZI-S475-Bootloader-Implementation/td-p/681249

发表于 02-01 07:21

什么是Logic Synthesis?Synthesis的流程

什么是Logic Synthesis?Logic Synthesis用于将输入的高级语言描述(如HDL、verilog)转换为门级电路的网络表示。

【紫光同创PGL50H】小眼睛科技盘古50K开发板试用体验之DDR读写测试

简单介绍一下紫光的DDR3 IP使用。基于紫光HMIC_S IP,完成对片外DDR3的读写测试。

01 软硬件平台

软件平台:PDS_2022.1

硬件平台:小眼睛科技盘古50K开发板

02 IP

发表于 10-09 19:07

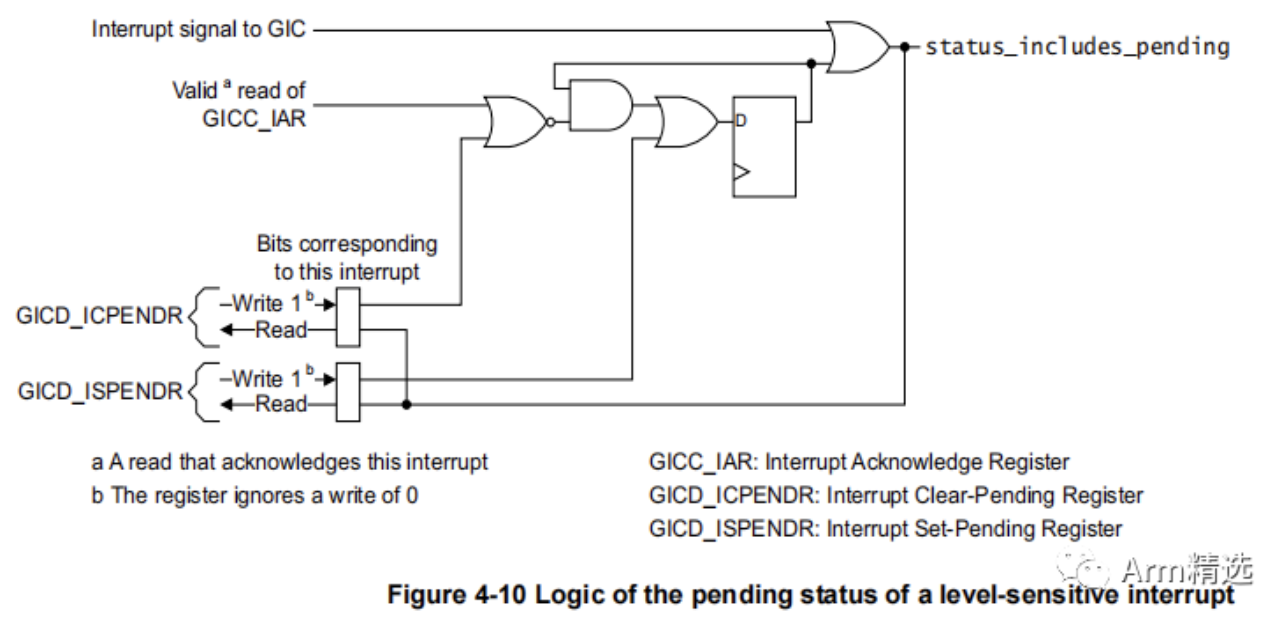

ARM通用中断控制器GIC之中断控制介绍

对于SGI中断是否能通过上述两个寄存器来enable和disable,这个由具体的实现( IMPLEMENTATION DEFINED)来定义。

发表于 09-19 17:09

•833次阅读

嵌入式HLS 案例开发步骤分享——基于Zynq-7010/20工业开发板(3)

Vivado2017.4 、Xilinx Vivado HLS 2017.4 、Xilinx SDK 2017.4。

Xilinx Vivado HLS (High-Level Synthesis

发表于 08-24 14:52

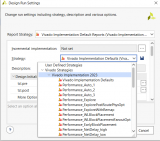

Vivado的Implementation阶段约束报警告?

帮到不经常看群消息的小伙伴,另一方面也算是我们的技术积累。 Q:Vivado的Implementation阶段约束报警告? [Vivado 12-627] No clocks matched

如何在Post Synthesis工程中加入XCI文件

是创建并定制 IP,生成这些 IP 的 output product (包括 IP 的 dcp);然后把第三方生成的网表文件和 IP XCI 的相关文件都加到 Vivado 的 post-synthesis 工程中。

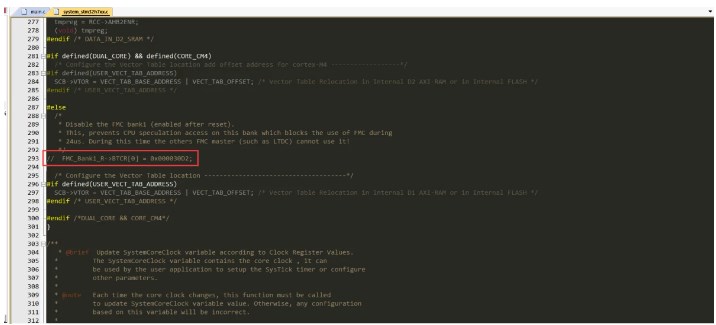

STM32H7实现BootLoader内SDRAM的初始化注意事项

Function Implementation:在 ArtPi 的环境下,实现一个简单的 BootLoader,该 BootLoader 实现了 QSPI 和 SDRAM 功能的初始化

今日说“法”:如何防止reg、wire型信号在使用逻辑分析仪时被优化

wire型号,对于ISE12.3以后的版本,XST综合,以Spartan3为例,可以使用(* KEEP=\\\"TRUE\\\"*) wire[15:0]CPLD_ _AD;这样

发表于 05-16 17:48

【小眼睛科技紫光盘古50K开发板试用体验】之二:LED跑马灯测试

的用于国产fpga开发的一套工具,界面耳目一新,特别容易上手。主要功能包括设计输入(DesignEntry)、综合(Synthesis)、仿真(Simulation)、实现(Implementation)和下载(Download)等。

OK

发表于 05-15 20:54

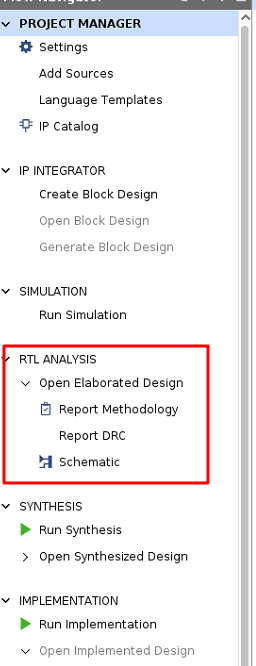

简述Vivado中的Elaborate的作用

在Vivado的界面中,有个RTL ANALYSIS->Open Elaborated Design的选项,可能很多工程师都没有使用过。因为大家基本都是从Run Synthesis开始的。

【PlanAhead教程】-3 Synthesis and Implementation

【PlanAhead教程】-3 Synthesis and Implementation

评论