随着芯片特征尺寸的不断减小,传统的平面MOSFET由于短沟道效应的限制,难以继续按摩尔定律缩小尺寸。因此,引入了FinFET,有效地解决了这个问题。FinFET成为 14 nm、10 nm 和 7 nm 工艺节点的主流的栅极设计。

短沟道效应

在MOSFET中,当沟道长度缩短到接近晶体管源极和漏极之间距离时,会出现阈值电压降低,沟道长度变化,热载流子效应等不利情况。在22nm以下短沟道效应更加严重,因此传统的MOSFET已无法胜任需求。

FinFET是什么

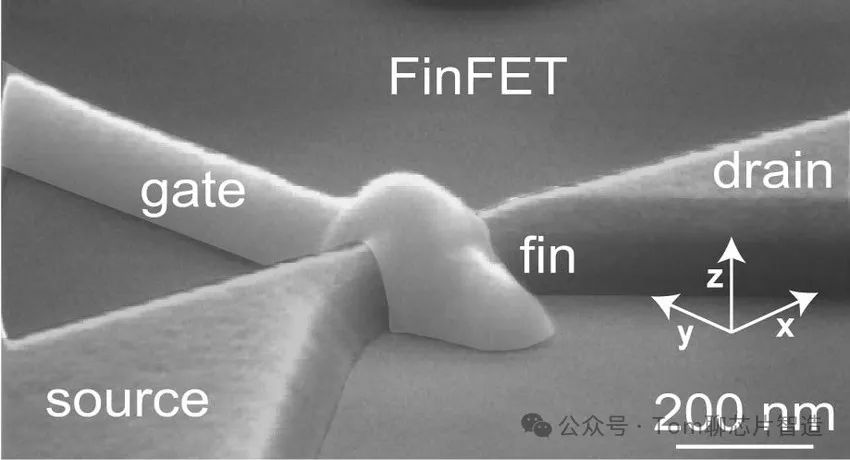

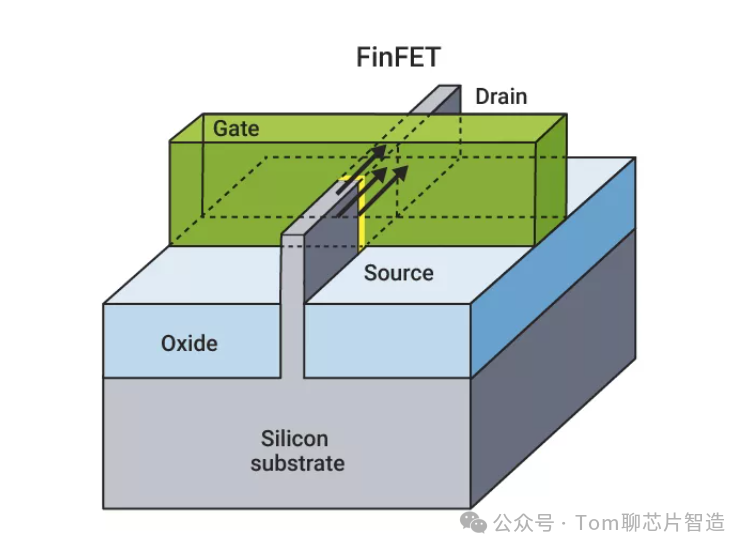

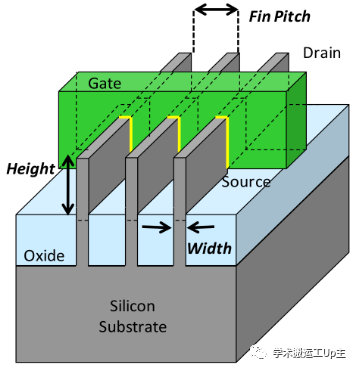

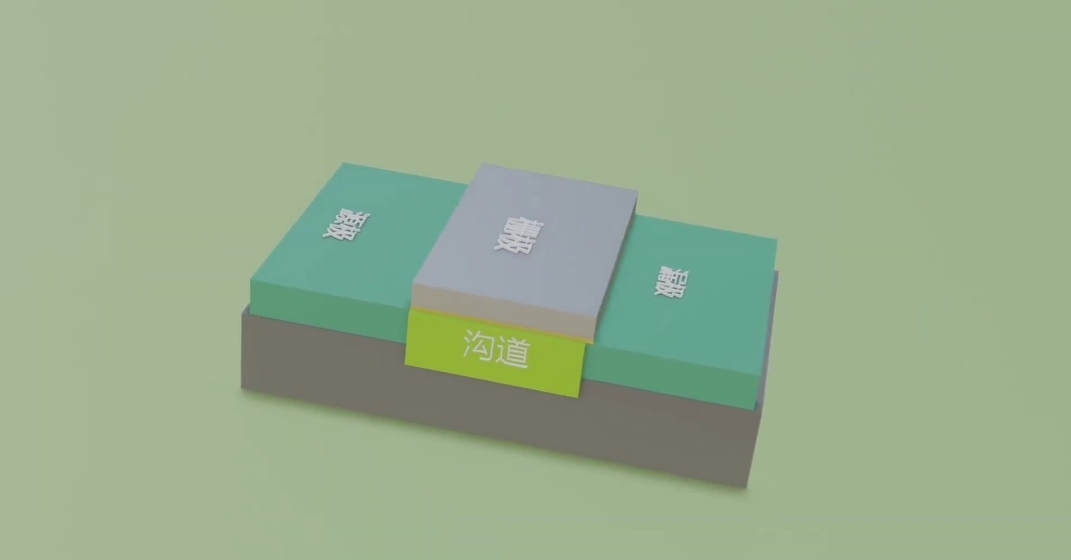

FinFET(Fin Field-Effect Transistor,鳍式场效应晶体管),是MOSFET设计的一次重大进步。其栅极放置在沟道的两侧、三侧、四侧或缠绕在沟道上,形成双栅甚至多栅结构。如下图:

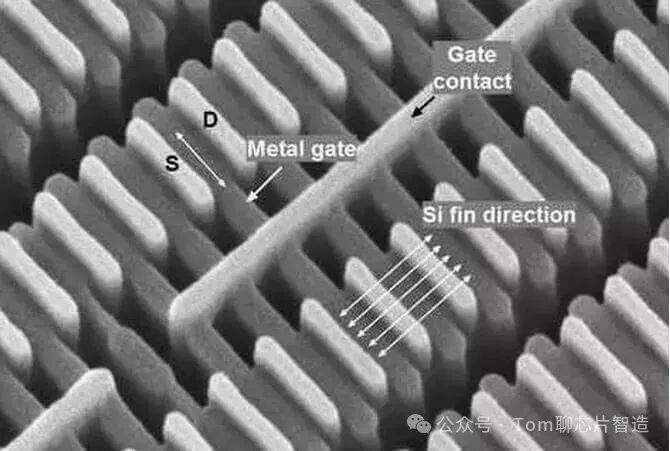

其中,鳍(Fin)位于硅基底上方的细长竖直结构。这个鳍形成了晶体管的沟道区域,电流会在这个区域流动。而鳍的高纵横比增加了栅极控制沟道的表面积,可以更精确地控制电流。

源极(Source)和漏极(Drain):图中标出的源极和漏极分别位于鳍的两端。源极与漏极是晶体管的主要电极,其中源极是电流的入口,漏极是电流的出口。

栅极(Gate):覆盖在鳍的侧面和顶部的是栅极材料,栅极可以通过电压来控制沟道中的电流。

氧化层(Oxide):栅极与鳍之间的氧化层起到绝缘的作用,防止电流直接从栅极流入沟道。在传统的MOSFET中,这一层通常是二氧化硅(SiO2),而在FinFET设计中,这一层可以是高介电常数材料,以提高栅极电容,同时降低栅漏电流。

硅基底(Silicon Substrate):整个FinFET结构构建在硅基底之上。

传统MOSFET是平面工艺,而FinFET 是3D工艺,相对于传统MOSFET来说,其栅极从三个面控制沟道,这使它在栅极和沟道之间形成的表面积更大,可以更精确更紧密地控制电流并减少泄漏,并具有更快的开关速度。

审核编辑:刘清

-

MOSFET

+关注

关注

141文章

6569浏览量

210134 -

摩尔定律

+关注

关注

4文章

622浏览量

78521 -

晶体管

+关注

关注

76文章

9054浏览量

135211 -

漏电流

+关注

关注

0文章

225浏览量

16662 -

FinFET

+关注

关注

10文章

247浏览量

89693

原文标题:22nm以下制程为什么要引入FinFET?

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

联电宣布22nm技术就绪

14nm FinFET的决斗,IBM死磕英特尔

22nm平面工艺流程介绍

22nm技术节点的FinFET制造工艺流程

[转]台积电借16nm FinFET Plus及InFO WLP 通吃英特尔苹果

FinFET(鳍型MOSFET)简介

请问FinFET在系统级意味着什么?

台积电计划于2012年Q3开始试产22nm HP制程芯片

FD-SOI元件与FinFET接近实用化的不断发布

什么是FinFET?FinFET的工作原理是什么?

FinFET是什么?22nm以下制程为什么要引入FinFET呢?

FinFET是什么?22nm以下制程为什么要引入FinFET呢?

评论