本文将讨论AMBA的第三次修订版,该修订版向世界介绍了高级可扩展接口(AXI)协议。

AXI协议最初是为高频系统而设计的,旨在满足各种组件的接口要求,同时允许灵活地互连这些组件。适用于高频,低延迟设计,AXI仍与先前的AMBA版本向后兼容AHB和APB。

了解AXI将使您深入了解SoC的工作原理,同时使您成为一名多才多艺且全面的设计师。

AXI架构

回想一下,AHB(高级高性能总线)是单通道总线,多个主机和从机用于交换信息。优先级仲裁器确定当前哪个主机使用该总线,而中央解码器执行从机选择。突发执行操作可能需要花费多个总线周期才能完成。每个突发传输都包括一个地址和控制阶段,随后是一个数据阶段。

AXI的设计理念相似,但使用多个专用通道进行读写。像它的前身一样,AXI是基于突发的,并且在交换数据之前使用类似的地址和控制阶段。AXI还包括许多新功能,包括乱序事务,未对齐的数据传输,高速缓存支持信号和低功耗接口。

AXI频道

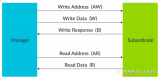

AXI主站和从站之间有五个独立的通道。它们是:

读取地址通道

读取数据通道

写地址通道

写数据通道

写响应通道

地址通道用于在执行主从之间的基本握手时发送地址和控制信息。数据通道是要交换信息的放置位置。

主机从从机读取数据并将数据写入从机。读取响应信息放置在读取数据通道上,而写入响应信息具有专用通道。这样,主机可以验证写事务已完成。

图1显示了通过五个AXI通道连接的AXI主从设备。

图1.AXI通道

每次数据交换都称为事务。事务包括地址和控制信息,发送的数据以及任何响应信息。实际数据以突发方式发送,其中包含多次传输。图1显示了由4个拍子或数据传输组成的读写突发。

我们将在本文后面详细讨论突发。

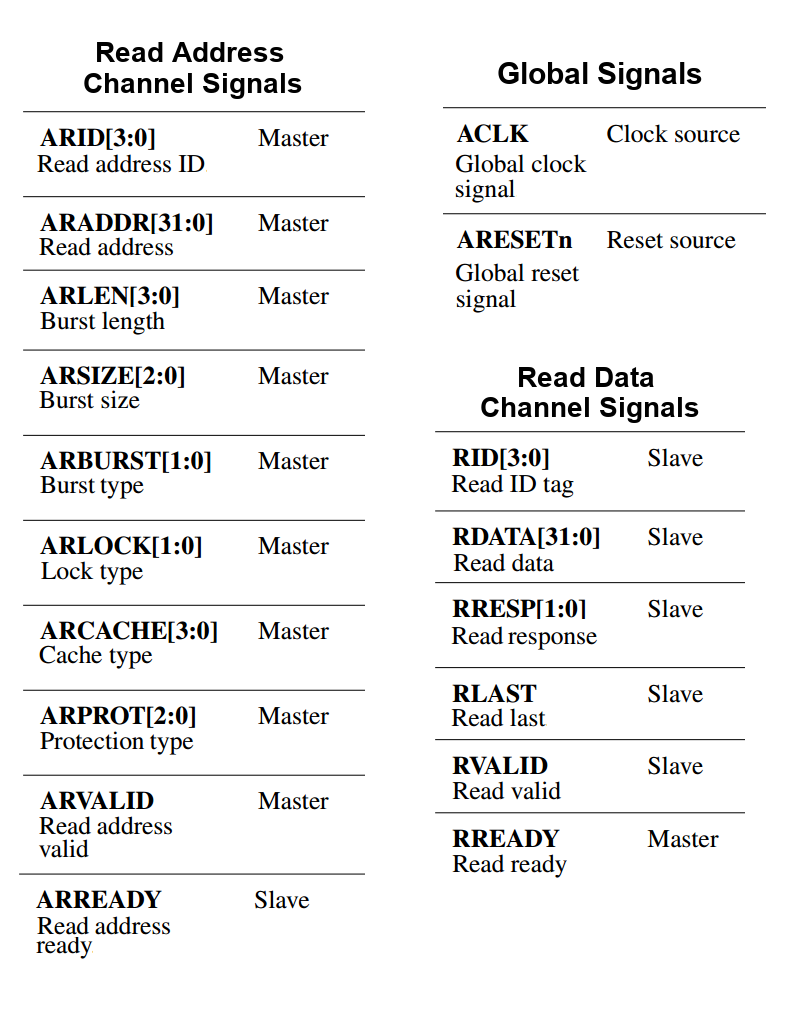

AXI信号

就像以前的AMBA版本中的AHB,ASB和APB信号一样,每个AXI通道都有许多与之相关的信号。有两个全局信号称为ACLK和ARESETn。它们分别是系统的全局时钟和复位信号。ARESETn的后缀“ n”表示此信号为低电平有效。

图2显示了与读取通道相对应的信号以及全局信号。

图2.读取地址,读取数据和全局信号

每个通道都有一个ID标签,用于无序交易。具有相同ID的任何事务都必须保留顺序,但是具有不同ID的事务可以按任何顺序完成。这样,即使较慢的事务首先发出,也可以在较慢的事务之前完成较快的事务。例如,如果一个主设备正在将数据写入多个从设备,则事务ID将允许更快的从设备更快完成。

总线宽度是特定于实现的,但是这些信号以32位总线宽度显示。从机使用RLAST信号向主机发送最后一个数据项正在传输的信号。

其他值得注意的信号包括突发大小,长度和类型。VALID和READY信号用于主机和从机之间的握手。这些将在本文后面讨论。

缓存,锁定和保护信号分别用于缓存,互斥访问(原子操作)和非法访问保护。

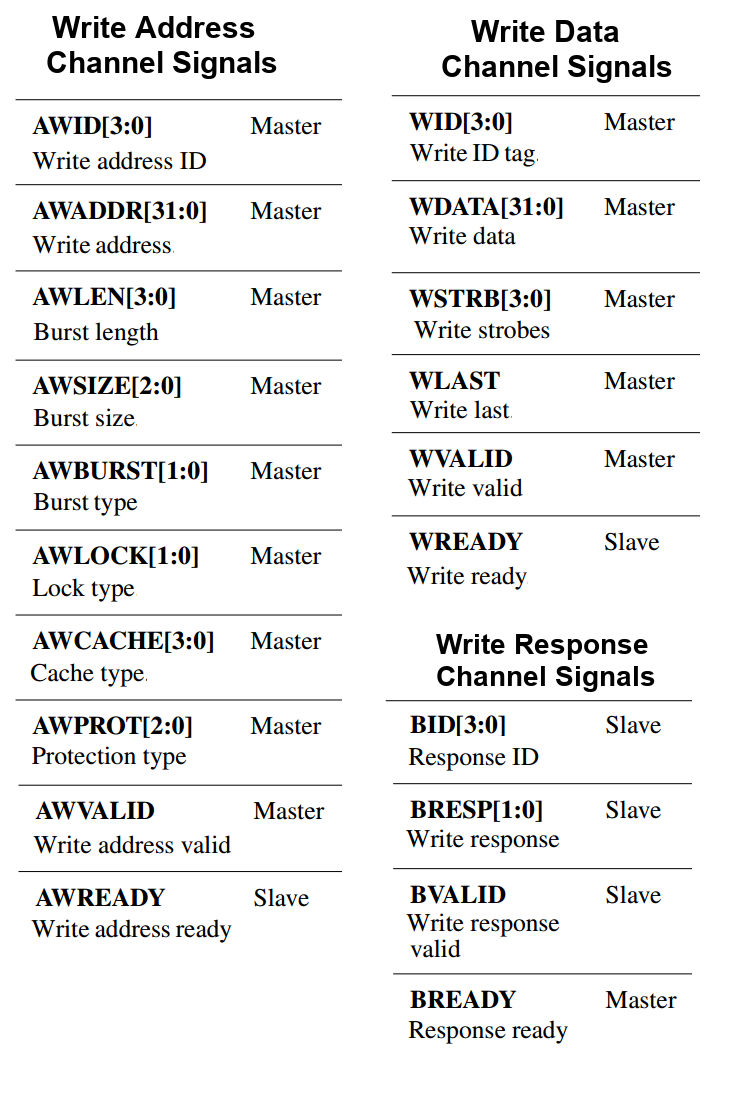

图3.写入地址,数据和响应信号

图3显示了写地址,数据和响应信号。这些信号反映了上面的读取信号,但被主机用来将数据发送到从机。WLAST向从站发出信号,表明正在发送最后一个数据项。专用的写响应信号使主机可以知道写事务已成功完成。

有关这些信号的更详细说明,请参阅AMBA 3.0版,尤其是AMBA AXI协议v1.0规范。

AXI交易

如前所述,AXI数据传输称为事务。事务可以采用读或写的形式,并包括地址/控制信息,数据和响应。数据以脉冲串的形式发送,其中包括多个称为节拍的数据项。为了同步数据的发送和接收,AXI主站和从站在事务开始时使用READY和VALID信号执行握手。

通道握手

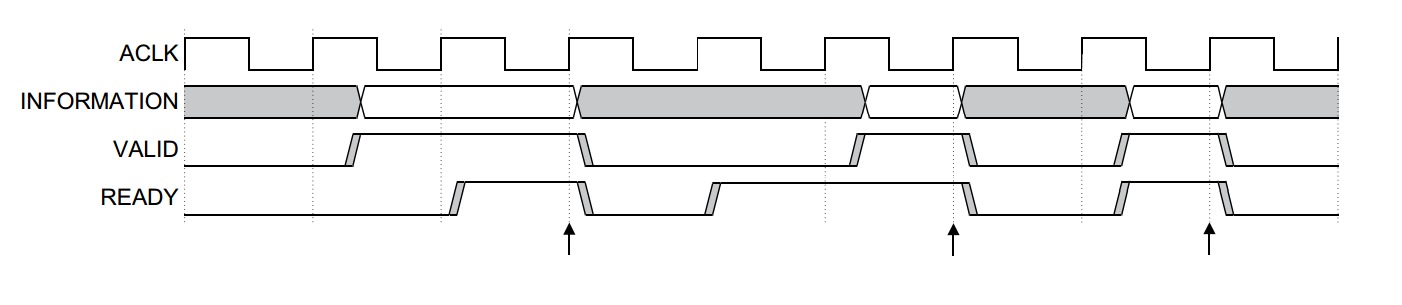

每个AXI通道都包含一个有效信号和一个就绪信号。这些用于同步和控制传输速率。这里要记住的重要一点是,源或发送者使用VALID信号表示数据或控制信息可用。当目的地或接收者实际上能够使用该信息时,它会发出READY信号。因此,只有当VALID和READY信号都有效时,才可以进行传输。

图4显示了工作中的AXI握手。通知信息传输(用箭头表示)仅在VALID和READY都较高时发生,而不管哪个先断言。还要注意,AXI在所有传输中都使用时钟上升沿。

图4.AXI握手机制(改编自AXI规范v1.0)

AXI规范中的一个重要说明是,一个组件的VALID信号绝不能依赖于另一个组件的READY信号。READY可以等待VALID信号,但不是必须的。遵循这些规则消除了发生死锁的可能性。如果VALID依赖于READY,而READY则依赖于VALID,则很容易看到两个信号都不会置为有效,因为每个信号都在等待另一个信号。

AXI爆发

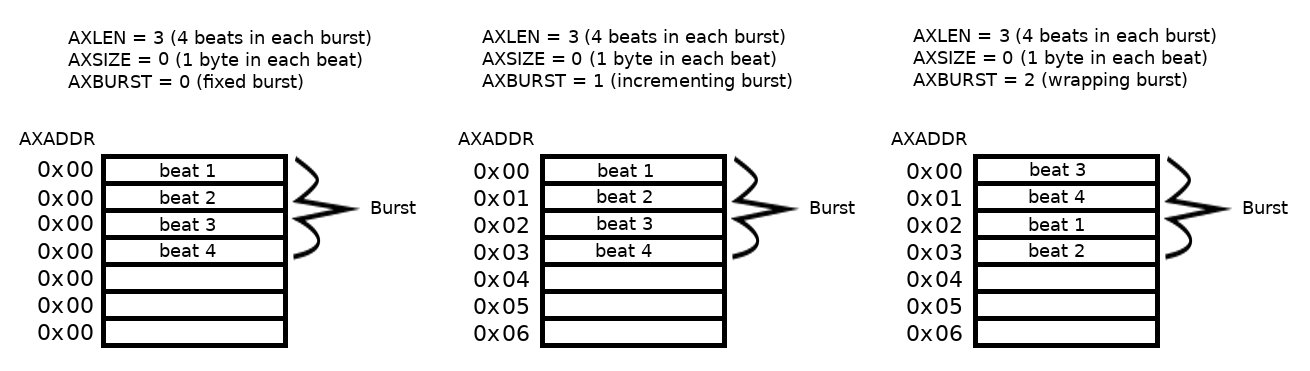

AXI中的数据交换采用突发形式。每个突发包括多个节拍或数据传输。在事务开始时发送的控制信息指示正在传输的突发的长度,大小和类型。

X代表R或W的AXLEN [3:0]表示突发中的拍数。宽度为4位,这意味着一个突发中最多可以进行16次传输。AXLEN = b0000表示每次连发有一个节拍。b0001,b0010和b0011的值分别代表两个拍子,三个拍子和四个拍子。这种模式一直持续到十六岁。组件必须完成AXLEN指定的所有节拍,无论是否使用数据。

AXSIZE [2:0]指定突发的每个拍中有多少个字节。AXSIZE中的每个位代表另一次幂2,“ 000”代表每个节拍1个字节,“ 111”代表每个节拍最多128个字节。这些节拍的大小不能超过母线宽度。

AXburst[1:0]确定将执行的突发类型。

AXI中有三种突发类型。他们是:

固定爆发

突发增加

包装爆裂

在固定的脉冲串中,地址不会随着每个节拍而改变。一个典型的应用是FIFO队列/缓冲区。

增量突发代表更典型的传输类型,其中在每个拍子之后,传输地址都会递增。您可以将其视为与基址的偏移量。

最终的突发类型是包装突发。包装突发与增量突发类似,不同之处在于存在一个包装边界,其中地址一旦增加到该点,它就会缠绕到一个较低的地址。

图5显示了三种不同类型的AXI突发的简化视图。

图5.AXI突发类型

AXI互连

AXI互连允许多个主机和/或多个从机相互连接。AXI规范定义了主机和从机,主机和互连以及从机和互连之间的接口。

实际上,互连包含连接到AXI主设备的从设备接口和连接到AXI从设备的主设备接口。互连中发生的事情(即,不同的主机如何与不同的从机通信)取决于实现方式。互连可以允许共享的地址总线,共享的数据总线都共享或不共享。

在下一篇文章中,我们将研究AXI互连,它们如何工作以及如何在设计中使用它们。

结论

本文是对高级可扩展接口(AXI)协议的基本介绍。我们查看了AMBA第三版中指定的旧版AXI。如前所述,您可以参考AMBA AXI协议v1.0(约一百页),以更深入地了解AXI的第一个版本。随着新版本的AXI(例如AXI4,AXI4-Lite和AXI4-Stream),AXI在AMBA版本4中看到了一些重大变化。

将来的AMBA文章将讨论用于组件之间系统级缓存一致性的AXI4和ACE协议(AXI一致性扩展)。AXI已成为现代SoC设计中广泛使用的协议。在学习AXI时,更简单的总线协议(如Avalon和Wishbone)将变得更加容易。

-

AXI总线

+关注

关注

0文章

65浏览量

14158

发布评论请先 登录

相关推荐

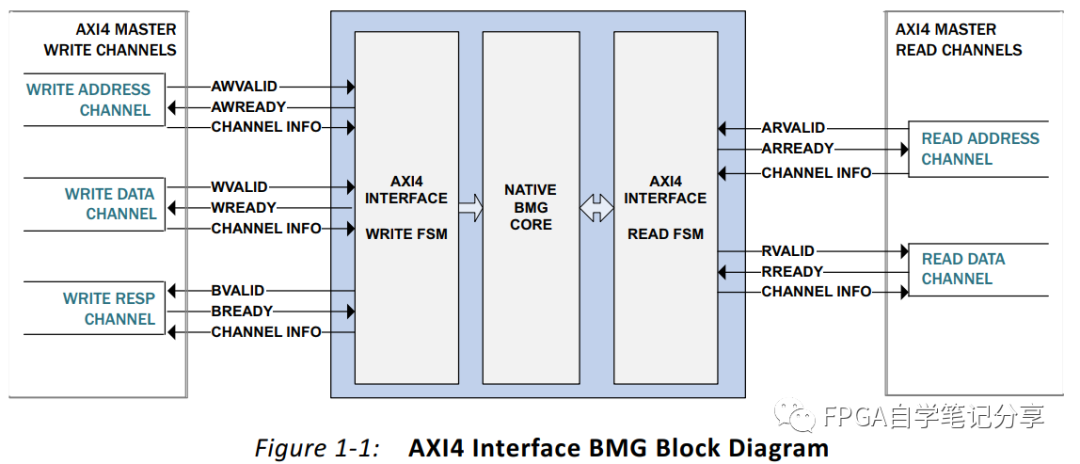

Xilinx FPGA IP之Block Memory Generator AXI接口说明

LogiCORE IP AXI UART 16550内核简介

LogiCORE JTAG至AXI Master IP核简介

AXI IIC总线接口介绍

通用LT-XC2V4000+用户指南

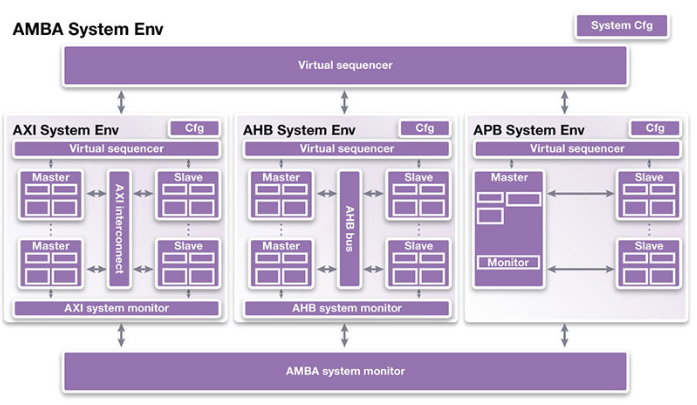

AMBA-PV TLM扩展用户指南

学习架构-AMBA AXI简介

AXI VIP当作master时如何使用?

自定义AXI-Lite接口的IP及源码分析

高级可扩展接口(AXI)简介

高级可扩展接口(AXI)简介

评论