SoC的全称叫做:System-on-a-ChIP,中文意思是“把系统做在一个芯片上”,你可以想像成PC时代的电脑核心CPU,在智能终端时代,手机的核心就是这个SoC。

它包含了计算机上的大部分部件。顾名思义,这是一个在硅芯片上制造的整个系统。SoC的美妙之处在于它将所有组件集成在一个衬底上。在半导体中,衬底是用来制造集成电路的硅薄膜。与传统主板相比,SoC将可更换部件集成到单个芯片上,从而减小了尺寸并提高了效率。与集成电路一起,SoC还包括用于集成的软件和互连结构。软硬件集成方法使SoC体积更小,允许更少的功耗,并且比标准的多芯片系统更可靠。

是什么构成了SoC

SoC可以分为以下类型:

1.围绕微控制器构建

2.围绕微处理器构建

3.针对特定应用构建

一个SoC的组成包括:一个处理器,主、次存储器和输入/输出端口。其他重要部件包括GPU、WiFi模块、数字信号处理器(DSP)和各种外设,如USB、以太网、串行外设接口(SPI)、ADC、DAC,甚至FPGA。通常,它有多个核。根据各种决定因素和偏好,核心可以是微控制器、微处理器、DSP,甚至是ASIP(应用程序特定指令集处理器)。ASIP有基于特定应用的指令集。

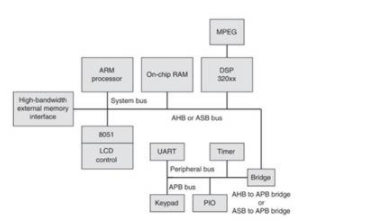

通常,SoC使用ARM体系结构,它属于RISC,需要较少的数字设计,从而使其与嵌入式系统兼容。ARM架构比8051这样的处理器更节能,因为与使用CISC架构的处理器相比,使用RISC架构的处理器需要更少的晶体管。这也降低了散热和成本。

下图显示了一个SoC框图的示例。

处理器

SoC的核心是处理器。它通常有多个处理器核心。多核允许不同的进程同时运行,这提高了系统的速度,因为它使计算机可以同时执行多个操作。基本上,操作系统将多个内核视为多个cpu,从而提高了性能。当多个核心被安装到同一个芯片上时,由于核心之间更快的通信,所以延迟就会更少。多核系统只有一个多核CPU插槽。

由于超线程,对于操作系统,单核作为两个逻辑单元出现。超线程允许在两个cpu之间共享物理资源。

数字信号处理器(DSP)

DSP是一种针对数字信号处理的操作进行优化的芯片。包括传感器、执行器、数据处理和数据分析的操作,它可用于图像解码。DSP的使用节省了其他处理任务的CPU周期,从而提高了性能。专用DSP更节能,这使得它们适合在SoC中使用。用于DSP核心的指令集是SIMD(单指令多数据)和VLIW(超长指令字)。这种体系结构的使用允许并行处理指令和超标量执行。DSP用于执行快速傅里叶变换、卷积、乘法累加等操作。

SoC上的内存

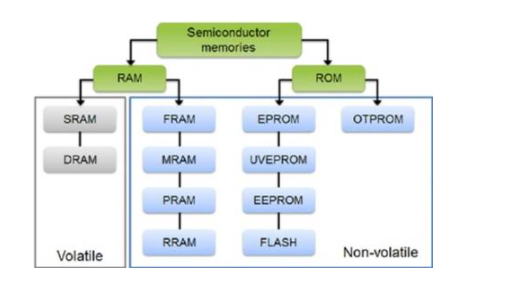

SoC有基于应用程序的内存。这些存储器是用于计算的半导体存储器块。半导体存储器通常是指在单个硅片上制造的金属氧化物半导体存储器单元。内存类型包括:

易失性存储器:断电后会丢失数据的存储器。换句话说,它们需要恒定的电源来保存信息。易失性存储器更快、更便宜,这也是被大众所接受的原因。

RAM是一种易失性存储器。最常用的RAM是SRAM和DRAM。SRAM由1、3或6个晶体管组成的存储单元组成。相反,DRAM只有一个MOSFET和一个根据FET状态进行充放电的电容。然而,DRAM容易受到电容泄漏电流的影响。DRAM的一个显著优点是它比SRAM便宜。如果一个SoC有一个缓存层次结构,SRAM被用于缓存,DRAM被用于主存储器。这是因为与主存相比,高速缓存需要更快的内存类型。

也有专为非易失性函数设计的RAM类型。例如FRAM,MRAM,它以磁性状态存储数据,PRAM(参数随机存取存储器),它在Macintosh计算机中用于存储系统设置,包括显示和时区设置。除此之外,还有RRAM(电阻随机存取存储器),它有一个叫做记忆电阻的组件。记忆电阻是一种电阻,其电压随所施加的电压而变化。

非易失性记忆:即使在没有电源的情况下也能保留信息的记忆。ROM(只读存储器)是一种非易失性存储器。ROM的类型包括EPROM(可擦可编程只读存储器),它是一组浮动栅晶体管。紫外线可擦可编程只读存储器(紫外线可擦可编程只读存储器),用紫外光擦除并重新编程数据,EEPROM(电可擦可编程只读存储器)和闪存。

选择的内存类型取决于设计规范和应用程序。

片上通信

传统上,总线体系结构用于SoC的执行单元之间的通信。然而,近年来,片上网络互联技术已经成为一种取代总线架构的趋势。

总线通信的一个流行的例子是ARM的AMBA(高级微控制器总线体系结构)总线协议。总线体系结构用于驱动组件之间的数据。片上总线体系结构可分为共享总线、层次总线和环形拓扑结构。不同的公司根据芯片的设计和应用设计了不同的架构。例如Altera AVALON, IBM CORECONNECT, silicon ore Corporation的WISHBONE。

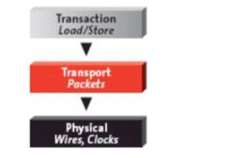

片上网络采用系统级网络技术进行片上流量管理。NOC是一种同构、可扩展的交换结构网络,用于传输多用途数据包。这个体系结构本质上是通过用户定义的技术分层。通信在三层通信方案上进行,即事务、传输和物理。

NOC互连结构的目标是减少芯片上的线路路由拥塞,提供更好的时间闭合,对SoC设计进行各种IPs的标准化改变。NOC体系结构已被证明更节能,并能满足吞吐量要求。

外部接口

SoC接口会按预定的程序进行延迟。外部接口通常基于WiFi、USB、以太网、I2C、SPI、HDMI等通信协议。如果需要,可以添加模拟接口与传感器和执行器接口。

其他组件

对于一个功能完整的SoC来说,其他必要的组件包括时钟、定时器、振荡器、锁相环系统、稳压器和电源管理单元等定时源。

SoC设计流程

SoC设计流程以架构协同设计为目标,即同时设计硬件和软件。设计流程必须考虑优化目标和各种约束条件。下图是一个从规范到制造的SoC设计流程示例,不同的团队执行制造SoC所涉及的每个步骤。

如今我们正在使用MOS技术制作SoC。最小的MOS技术是TSMC和三星共同开发的3nm技术。然而,今天的大多数器件都使用10nm技术。制作过程包括设计的网表生成,然后是物理设计流程。在整个过程中,需要特别注意静态时序分析(STA),即数字电路中的时序计算。STA还用于验证计时性能和检查任何计时违反。当数字电路中的触发器处于未知状态(既不是1也不是0)时,时序违反会导致亚稳态。

在制作步骤1中,分析设计规范,并生成执行规范所需的IP列表。这些IP通常外包给第三方IP供应商。这些IP可以是软核、硬核,这取决于更改参数的灵活性水平。IP也可以由同一家公司制作。

在步骤2中,集成IP,生成整个设计的RTL描述。RTL代表寄存器传输级别,它包括各种硬件描述语言的使用,如Verilog、System Verilog和VHDL。RTL是硬件寄存器之间的同步数字电路的型号。

在步骤3中,一个门级网表由SoC积分器生成。网关级的网表(netlist)包含有关标准单元的逻辑连接性的数据:组合单元格、顺序单元格和网络。网络是由两个或多个相互连接的组件组成的一组。用于测试的设计(DFT)工具用于提高可测试性。

在步骤4中,根据物理设计流程将网关级网表转换为布局。在这个阶段也可以导入IP核。物理设计包括将设计的电路表现形式转换成几何形状,从而在制造后使元件发挥作用。

在步骤5中,假设静态时序分析和功率分析已经完成,最终的布局将被开发并送往制造。

第6步,在组装过程中检查制作好的芯片。在此步骤之前,要彻底检查芯片的逻辑正确性。这种检查被称为功能验证,它占整个过程的很大一部分。为了执行验证,像SystemC、System Verilog这样的语言越来越受欢迎,他们应对复杂性有自己的妙招。

重要的是,在制造后对芯片进行任何更改都是非常困难和昂贵的。因此,设计的仿真(原型)是在制造之前进行的。这通常使用FPGA来完成,因为它是可重新编程的,并且允许调试。

SoC的优缺点

SoC的主要目标是最小化外部组件。因此,较之单板机有以下优点:

1.大小:SoC的大小相当于一枚硬币。由于MOS技术的不断演进,SoC可以做得非常小,同时能够执行复杂的任务。尺寸不影响芯片的特性。

2.低功耗:SoC针对手机等低功耗设备进行了优化。低功耗让手机的电池容量更高。

3.灵活性:SoC很容易重新编程,这使得它们很灵活。它们允许IP的重用。

4.可靠性:SoC提供了更高的电路安全性,降低了设计复杂性。

5.成本效益:主要由于较少的物理组件和设计重用

6.更快的电路操作

但它也有一些缺点:

1.耗时:从设计到制造的整个过程可能需要6个月到1年。因此,市场需求的时间是非常高的。

2.设计验证要求非常高,消耗了总时间的70%。由于SoC设计的日益复杂,设计验证越来越繁琐。此外,IP的可用性和兼容性起着非常重要的作用,可以增加上市时间。

3.制造成本呈指数增长。

4.对于小批量产品,SoC可能不是最佳选择。

应用程序

今天,SoC最常见的应用是移动应用,包括智能手机、智能手表和平板电脑。其他应用包括信号语音处理,PC接口,数据通信。由于集成了LTE和无线网络等通信模块,SoC也被应用到个人电脑上。

目前市场上最受欢迎的当属由高通生产的SoC,用于智能手机、智能手表和即将到来的5G网络兼容。其他制造商包括英特尔科技、三星、苹果、华为海思等。

编辑:hfy

-

soc

+关注

关注

38文章

3745浏览量

215678 -

无线网络

+关注

关注

6文章

1374浏览量

65242 -

数字信号处理器

+关注

关注

5文章

309浏览量

27195 -

硅芯片

+关注

关注

0文章

85浏览量

16829

发布评论请先 登录

相关推荐

SoC设计中什么构成了良好的互联?

SOC设计从Spec到流片:一窥全流程

SOC设计与验证流程是什么?

SoC是什么意思

SoC芯片的开发流程有哪几个阶段

SoC设计流程相关资料下载

使用Arm DesignStart处理器核搭建SoC流程

SOC的多核启动流程详解

SOC设计方法与实例

嵌入式SoC IC 的设计方法和流程

用于SoC验证的(UVM)开源参考流程使EDA360的SoC

如何搭建SoC项目的基本流程

SoC设计流程

什么构成了SoC SoC设计流程步骤详解

什么构成了SoC SoC设计流程步骤详解

评论