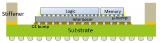

在 SoC 上集成更多功能的难度越来越大,这促使着整个芯片行业对新封装方法的探索,其中既有更复杂的集成 SoC,也有多芯片封装等形式的先进封装。

截至目前,这一领域的大部分工作都是高度定制化的。但随着先进封装日益主流,差距也在开始出现。

“IC 封装在过去 10 年中取得了非常显著的进展,但 IC 封装今天所能应对的复杂度还相当有限。”eda2asic Consulting 总裁 Herb Reiter 说,“正如我们所见,价值创造正越来越多地转向封装而且封装与硅方面的合作也越来越多,我们遇到了一个让人头疼的大问题,因为目前还没有什么 die-封装联合设计流程。从硅领域向封装领域输送信息是非常困难的,而硅领域要从封装领域获取反馈信息甚至还要更加困难,但这样才能联合优化这两个领域。”

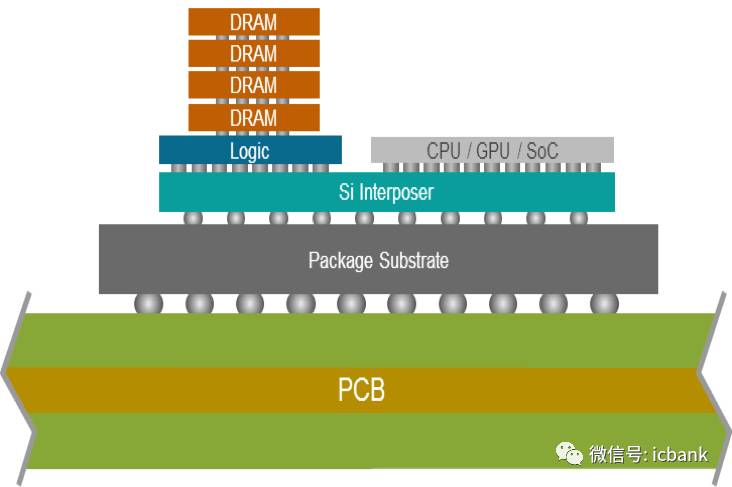

图 1:超越摩尔定律,来自 Cadence

要取得成功,封装必须接近由摩尔定律扩展所带来的 PRA 收益,而更快的上市时间还能带来额外的收益。

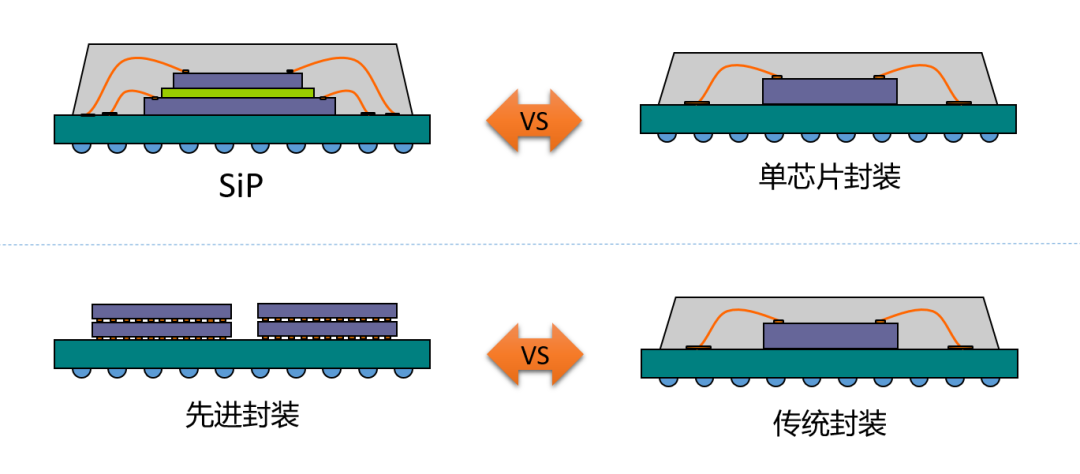

“但随着工程开发团队成功实现这些多 die 异构设计,在一个封装中放入更多内容的难度也会越来越大。”西门子一个业务部门 Mentor 的产品营销经理 Keith Felton 表示,“在纸面上这看起来很合情合理。你可以混合技术节点、工艺,你可以将具有不同功能的不同异构芯片放到一起,将它们与 interposer 一起组合到同一个封装中,然后基本上你就得到了一个非常好的可工作的子系统,而且几乎就像是在单个 SoC 中一样高效。理论上,这仅需远远更低的成本和风险就能接近 SoC 的性能表现。它的面积会多一点点,高度也会多一点点,但现在他们正在解决这些问题。”

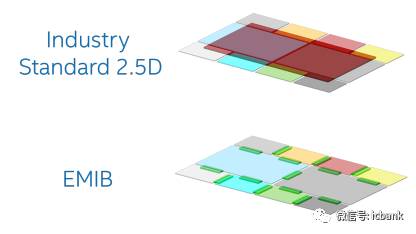

他们想在每个方面都能赶上。“甚至英特尔也脱离了更小更小更小的‘经典’摩尔定律算法,因为这个东西没效了。”Optimal+ 全球营销副总裁 David Park 表示,“他们做的是开始进军多芯片封装、多芯片模块,因为这比试图将所有东西都放在 28nm 等节点上要容易得多。‘我们会将数字逻辑放在 28nm,但让模拟部分留在 45nm,因为这样效果很好,然后我们会在基板上将它们连接起来。’这差不多就是人们绕过摩尔定律的方式——通过某种类型的 interposer 将多个芯片组合到一起。这样他们就能将具有收益的小特征尺寸和能提供更高鲁棒性和质量的更大特征尺寸组合到一起。”

图 2:英特尔的 EMIB 方法,来自英特尔

集成方面的问题

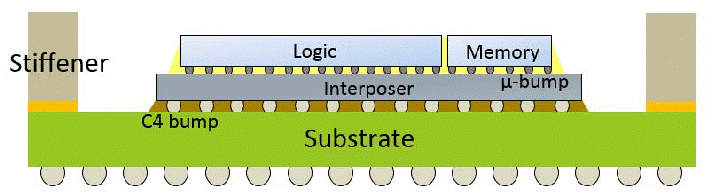

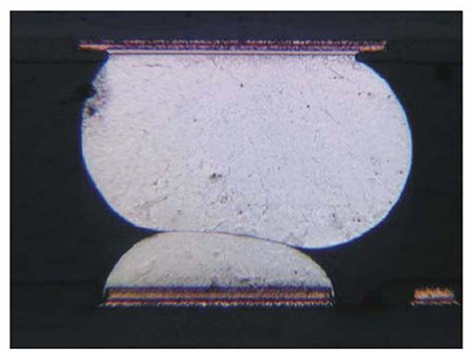

尽管这项工艺的细节设计和布局部分已经得到了很好的理解,但要将芯片与 interposer 放到一起并找到正确的连接方法却并不轻松。“过去这通常是在纸面上完成的,还有每个人都在谈的 bump ball spreadsheet,这是这个工艺的代名词。”Felton 说,“但这是静态文档,不是真正的设计工具。它们无助于你了解其中的权衡。它们不会给你的连接是否正确提供任何反馈。它们只是记录了你按顺序做的事情的文档,以便你能将其提供给别人,所以它们只是静态的文档,实际没什么用。尽管可能看起来很不错,但从信号集成的角度和热分析的角度看,这可能是无效的。”

一旦物理布局完成,就要验证设计,这又会增加潜在的雷区。如果一开始就在逻辑连接各个部分之间出了错,当你进入最后的设计阶段并在验证过程中发现问题时,就会需要大量返工。Felton 说:“如果你和你的代工厂和 OSAT 锁定了生产时间,这就会变得非常困难。你实际上就会错过他们的生产计划安排。”

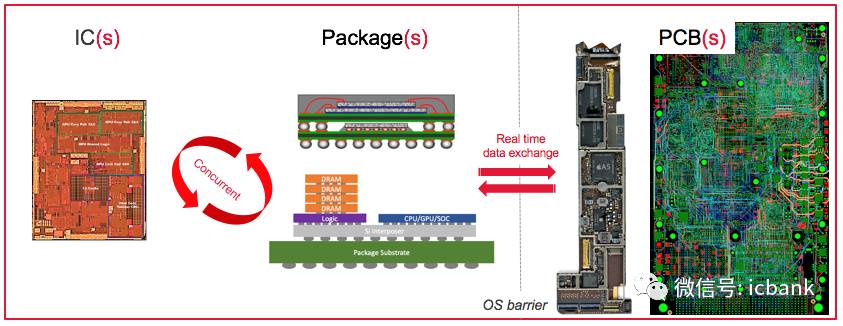

为了避免这些问题,一些设计团队已经开始关注在系统层面上创造前期设计原型——基本上就是创造整个设计的数字模型。这让他们可以从顶部 die 一直到 package ball 或甚至到印制电路板上一路跟踪导通性,而且也可以在该模型上修改设计,然后将其送入仿真工具。但从多个来源组合数据以构建整个封装结构的逻辑原型并不是简单的工作。

Felton 说:“即使你是一家无晶圆厂半导体公司,你也不需要设计放入设备的所有芯片。你可能会从一些公司那里得到内存堆栈或 memory cube,你可能会使用你自己设计的处理器或微控制器,但也会使用其它现成可用的器件。通常你需要 Verilog 网表(netlist)这样的东西,你也需要其它 die 的某种形式的 footprint 模型,实体 footprint 通常是以 GDS 形式提供的。你可能会得到一个 SPICE 网表或一个 Verilog 顶级网表,但你还是要将所有这些组合到一起并且保证你的组合方式是正确的。”

此外,针对这些组合到一起的单个器件的逻辑模型,必须为这种物理数字模型进行布局与原理图验证。

一旦创造出了验证过的模型并且得到了正确的逻辑验证,那就有可能开始要在 die 的封装方式上做一些权衡——用并排结构还是垂直结构、应该使用什么类型的封装和互连。

Felton 说:“一些人试图使用原理图捕获(schematic capture)。他们试图绘制符号来表示 die,他们试图导入 Verilog 网表作为 die 的主体。然后他们会在上面连接外部端口。你又带来了另一层不正确连接的风险。这有很大的风险。也可能有好处,你可以将其看作是一副生动的原理图,这可能对工程师而言非常有用。但将不同的数据部分放到一起,正确连接,然后以此为基础向前发展,这个过程中存在非常多的风险。通常他们会发现,在他们进入实体设计阶段时会有 LVS 错误,所以他们必须返回去调试这个错误出现的确切位置。是不是原来的 Verilog 网络不正确,还是在构建原理图时 Verilog 端口映射得不对?人们已经试过使用原理图了,但这没法提供任何实体方面的理解,因为这是平面的静态的,没法说明在 3D 情况的状况。”

人类因素

说服设计工程师使用新方法也并不容易。

Felton 说:“如果你看看我们今天的客户,我可以说有 30% 在尝试使用新方法,但这要在设计工艺和设计流程上做根本性的改变。首先,你需要让这些设计师用那种方式思考,这可能需要时间。他们已经知道该怎么做一些事了。他们知道这并不完美,但是有效。而且他们知道在任何不得不改变的时候,都只会带来更大的风险,所以他们会后撤,直到他们解决这个问题或遭遇灾难性的失败。”

另外设计和封装团队往往工作在不同的管理层面上。这些团队往往会被人为地拉入一个组,这么做并不总是很有用的,因为这个组中的人往往分散在世界的不同地理位置。这里的关键是要能安全地来回传递设计的改变和模型。

通过为他们定义一种更好更智能的数据交换流程,很多公司才能采用这种方法,而不是迫使他们的团队聚到一起或处在同样的管理结构层次中。而这又会真正落入到所有数据的产品生命周期管理中。

“在 SoC 设计领域的 IC 方面,我们喜欢说这是一个幸福大家庭。”Mentor 技术营销工程师 John Ferguson 说,“但实际并不是。其中有很多沟通问题。我们有一些设计团队在研究不同的 IP 模块,与此同时还有其他一些人在研究如何将这些 IP 在 SoC 中连接到一起。而且即使有最好的意图,也不会百分之百正确,很大程度上是因为他们是各自为战的团队。一般他们会在开始时聚在一起研究出规格,似乎每个人都想主导并且认为他们做的事别人都同意。但是之后你会发现中间会有些沟通不畅。我认为这种情况并不会真正改变。关于谁在做什么、谁负责什么以及怎么沟通上都一直不会连贯一致。”

图 3:先进封装的现有流程,来自 Cadence

而且随着先进封装的发展,难度还会越来越大。

“项目规模越大,让人们合作的难度也就越大。”Flex Logix CEO Geoff Tate 说,“单个芯片设计团队可能会有数百人,而封装团队可能在另一个楼层或另一栋楼里——或者另一个城市。所以当所有东西都变得非常大非常专业化时,紧密合作的能力就会下降。在一起紧密工作的团队总是有益的。在团队规模非常大的时候,这事儿就会非常难。当你的楼里面有 500 人时,你就没法让他们一起紧密工作。其中一些会在一起紧密工作,另一些则分散在不同的多个楼层。当你的团队很大的时候,就会遇到组织上难题。”

不过,也可能会出现变化。Cadence 的 IC 封装和跨平台解决方案产品管理总监 John Park 说芯片设计团队、封装设计团队甚至电路板设计团队都已经开始更紧密的合作了。他说过去 7 或 8 年来大型的半导体公司都是这样。

直到最近,他们的合作还基本上没有在信息协同设计流程中共享 EDA 工具、微软 Visio 制图、PowerPoint 幻灯片、Excel 电子表格、电子邮件和白板制图。

“但至少他们已经认识到他们不能只设计一块芯片然后就扔过墙壁给设计团队,然后让他们处理各种问题,然后再扔过墙给电路板设计团队。”Park 说,“所有的大公司都意识到这种方法已经不再可行。事实上,英特尔在 7 或 8 年前就在一场会议上做了一篇论文说他们正在使用那种方法,这使得他们的封装成本高于他们的芯片成本。很显然这杀死了这个项目。英特尔是这一趋势的最早采用者之一,这个行业中很多人都说这是‘探路’,其中许多做芯片的人和做封装的人甚至做电路板的人都开始在芯片流程早期进行合作,同时规划应该以什么封装技术为目标进行设计”

展望未来,对 3D 堆叠的兴趣和采用肯定会在半导体系统上带来更大的价值,并为 3D 堆叠上智能分区能力等 EDA 创新带来机会。Park 说:“这不只是为了在单个技术上规划单个芯片。它也可以在一个堆叠上做三个芯片的智能布局规划,以便根据产生热量和电气性能等要求,确定哪个模块应该位于堆叠中的哪块芯片上。这是一个有价值的领域。这几乎就像是引入芯片的 RTL 描述,但可以用于每个垂直堆叠中的 2 个或 3 个芯片。”

-

半导体

+关注

关注

328文章

24504浏览量

202083 -

数据

+关注

关注

8文章

6511浏览量

87592 -

逻辑

+关注

关注

2文章

818浏览量

29293

发布评论请先 登录

相关推荐

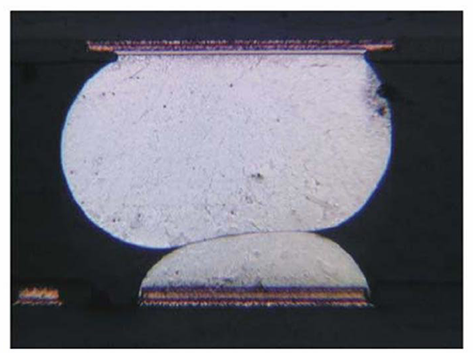

浅谈BGA、CSP封装中的球窝缺陷

传统封装和先进封装的区别

锂电池中的三元电池有什么优点和缺陷吗?

什么是先进封装?先进封装技术包括哪些技术

什么是先进封装?先进封装和传统封装区别 先进封装工艺流程

一文解析Chiplet中的先进封装技术

盘点先进封装基本术语

算力时代,进击的先进封装

探究BGA封装焊接:常见缺陷与异常解析

SiP与先进封装有什么区别

简要解析先进封装的优点和缺陷

简要解析先进封装的优点和缺陷

评论