摘 要 :DDR3 SDRAM 是第二代双倍数据传输速率同步动态随机存储器, 以其大容量、 高速率和良好的兼容性得到了广泛应用。 文中介绍了 DDR3 的特点和操作原理, 以及利用 MIG 软件工具在 Virtex - 6 系列 FPGA 中实现 DDR3 SDRAM控制器的设计方法, 并进行硬件测试。 验证了 DDS3 控制器的可行性, 其工作稳定、 占用资源少、 可植性强等。

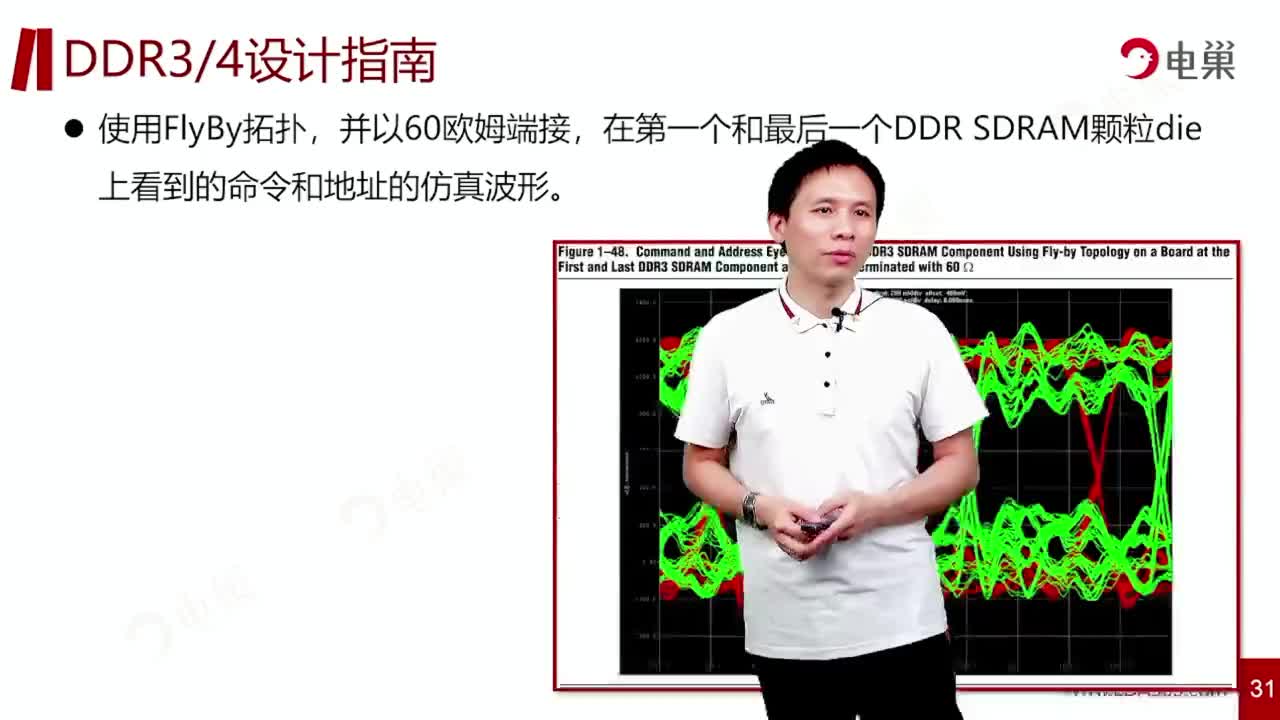

DDR3 SDRAM 是从 DDR、 DDR2 发展而来的一种高 速同步动态随机访问存储器。 由于 DDR3 SDRAM 可以 在脉冲的上升和下降沿都传输数据, 因此传输数据的等 效频率是工作频率的两倍。 与 DDR2 相比, DDR3 主要 有以下优势: ( 1) DDR3 采用 8- bit 预取技术, 解决了 外部数据传输率与核心频率之间的矛盾, 保证了数据 传输率的持续增长, 同时增加了带宽。 ( 2) DDR3 的核 心电压为 1.5 V, 增加异步重置与 ZQ 校准功能, 功耗 比 DDR2 降低了 25% 。 ( 3) DDR3 存储器模块的地址、 命令、 控制信号和时钟采用了“ fly - by” 的拓扑结构, 大幅减轻了地址 / 命令 / 控制与数据总线的负载, 提高 了信号的完整性[ 2] 。本文介绍了 DDR3 的特点和操作原理, 利用 MIG 软 件工具在 Virtex - 6 系列 FPGA 中实现 DDR3 SDRAM 控 制器的设计, 并给出了硬件测试的结果。

1 DDR3 的操作原理

DDR3 SDRAM 加电后必须按照规定的步骤完成 初始化。 在初始化的过程中应注意对模式寄存器和扩 展模式寄存器的配置。 通过初始化可以完成对 CAS 延迟, 突发长度, 突发类型, 输出驱动能力, 片上端接电 阻( ODT) 的值, 伴随 CAS 的附加延迟, 片外驱动器校 准等配置[ 3 - 4] 。 初始化完成后, DR3 SDRAM 进入正常 工作状态, 此时可以对其进行寻址和读写操作。

1. 1 预充命令

预充命令用于释放已经打开的 Bank 和已经打开 的行或者打开新的 Bank 和新的行。 发送预充命令后, 要经过 tRP( Row Precharge command Period, 行预充电 有效周期) 个时钟发送行有效命令。 如果超过了这个 延迟, 那么 Bank 就会进入空闲状态。 地址线的 A10 用于决定是对一个还是所有的 Bank 进行预 充。 一 个Bank 被预充之后, 进入空闲状态, 等待接收激活命令。

1. 2 激活命令

在任何读写命令被发送到 DDR3 SDRAM 存储器 的行上之前, Bank 中的行必须使用激活命令进行激 活。 与激活命令一起被触发的地址用来选择将要存取 的 Bank 和行, 与读或写命令一起触发的地址位用来选 择突发存取的起始列单元。

1. 3 读命令

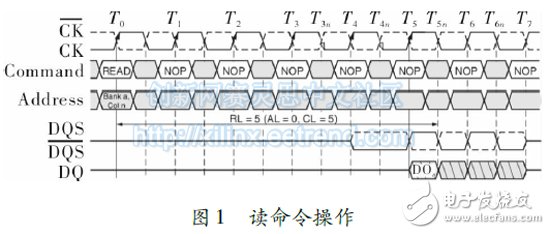

读命令用来启动一个突发的存储器读操作, 以访 问一个激活的行。 BA0 ~ BA2 用来选择存储体 Bank 地址, A0 ~ Ai 提供的输入地址用来选择开始列位置。 在读操作完成之后, 这个行在随后的访问中仍是活跃, 直到该行被预充命令关闭。 随着数据一起传送的还包 括一个双向的数据选通信号 DQS, 在读周期中, DQS 由 DDR 存储器产生, 它与数据时边沿对齐, 其读时 序[ 2] 如图 1 所示。

1.4 写命令

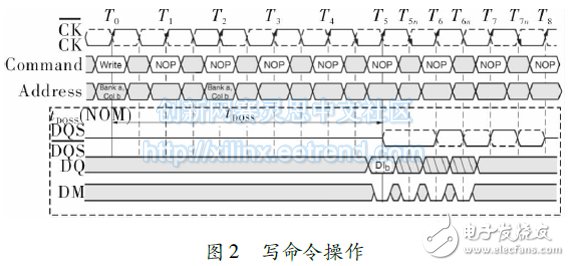

写命令用来启动一个突发的 存 储 器 写 操 作, 由 FPGA 向 DDR3 SDRAM 写 入 数 据, 只 需 按 照 DDR3 SDRAM 的工作要求发出相应的指令即可。 BA0 ~ BA2 用来选择存储体 Bank 地址, A0 ~ Ai 提供的输入地址用 来选择开始列位置。 在写周期中, DQS 由 DDR3 控制 器产生, 它 与 数 据 时 中 心 对 齐, 其 写 时 序[ 2] 如 图 2 所示。

1. 5 刷新命令

DDR3 是动态存储器, 必须要定期进行刷新才能 维持其存储的内容。 刷新间隔和 DDR3 存储器芯片的 温度有关。 刷新方式分为两种: 自动刷新和自刷新。 自动刷新用于正常操作模式, 在自动刷新时, 其他命令 无法操 作。 自 刷 新 主 要 用 于 低 功 耗 状 态 下 的 数 据 保存。

2 DDR3 SDRAM 控制器的总体设计

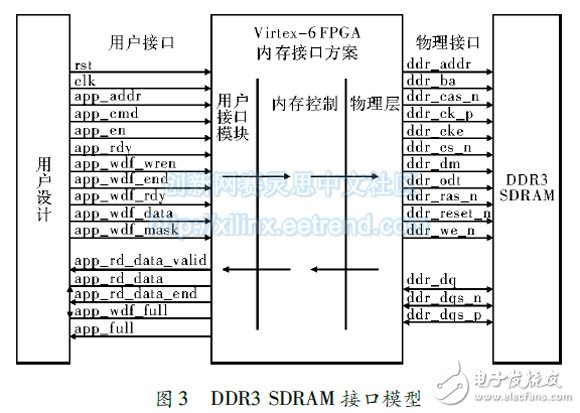

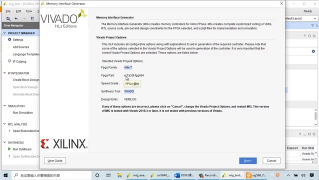

DDR3 SDRAM 控制器可以采用 Xilinx virtex - 6 系 列 FPGA 提供的免费 IP 核 MIG3. 9 来设计, 这样可以 缩短开发周期, 减少设计人员的工作量, 简化了系统设 计。 用户只需在 MIG 的 GUI 图形界面选择对应的芯片型号, 总线宽度和速度级别, 并设置 CAS 延迟、 突发 长度、 引脚分配等参数, 即可生成 DDR3 SDRAM 控制 器, 包括 HDL 代码和 UCF 约束文件。 Xilinx virtex - 6 系列的 FPGA 内存接口解决方案如图 3 所示, 该解决 方案屏蔽了内存底层操作的一些细节。 用户设计模块 可以通过用户接口模块直接操纵内存控制器。

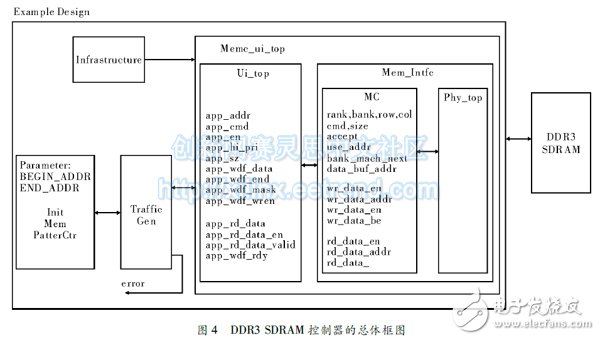

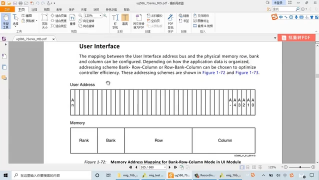

DDR3 SDRAM 控制器的主要功能是完成对 DDR3 SDRAM 的初始化, 将 DDR3 SDRAM 复杂的读写时序 转化为用户简单的读写时序, 以及将 DDR3 SDRAM 接 口的双时钟数据转换为用户的单时钟沿数据, 使用户 像操作普通 RAM 一样控制 DDR3 SDRAM; 同时, 控制 器还要产生周期性的刷新命令来维持 DDR3 SDRAM 内的数据不需要用户的干预[ 5] 。 DDR3 SDRAM 控制 器的总体框图[ 1] 如图 4 所示, 物理层模块的右侧信号 端口连接 DDR3 SDRAM 的物理引脚。 其主要包括 4 部分: 基础模块 ( Infrastructure) 、 用户界面模块 ( User Interface) 、 物理层模块( Physical Layer) 和存储器控制 模块( Memory Controller) 。

基础模块主要用来接收通过 FPGA 全局时钟网络 的外部 200 MHz 的差分时钟, 然后通过数字时钟管理 器( DCM) 产生用户接口时钟、 控制模块使用的时钟和 DDR3 存储器的时钟, 同时产生一个复位信号对整个 IP 核进行全局复位。 该模块还包括一个延时控制单 元, 用来同步校准设计中的延时单元以减少功耗。

用户接口模块主要控制命令和数据连续的输入和 输出, 用来接收和存储用户的数据, 命令和地址等信 息, 起到缓冲和同步数据的作用。

物理层模块直接与 DDR3 SDRAM 通信, 其主要功 能是 捕 获 DDR3 SDRAM 发 出 的 数 据, 产 生 DDR3 SDRAM 所需要的控制指令信号, 并通过输入输出缓存 发送所有 DDR3 SDRAM 的控制信号、 地址信号以及数 据信号, 同时保证指令与地址, 数据的同步和信号的维持[ 6] 。

控制模块主要实现对 DDR3 的初始化和命令的操 作, 故其由初始化和命令控制两部分组成。 DDR3 上 电后经过 200 μs 的稳定期, 再等待 500 μs 把时钟使能 信号 CKE 拉高, 保持至少 10 ns 后开始 ODT 过程, 然 后对扩展模式寄存器和模式寄存器进行配置, 使能 DLL 并对 DLL 复位, 校准结束, 信号 phy_ initial_ done 拉高则表示初始化完成。 初始化完成后, 控制模块自 动产生命令和控制信号并按照 DDR3 的读写时序要求 送给 DDR3, 命令发送完毕后提供给用户一个命令应答信号, 设计者根据这一信号判断是否可以发送下一 个命令。 整个过程用户完全不用干涉存储器的自动刷 新、 激活和预充电过程, 这些控制命令和过程都会有控 制器自动发出和完成。

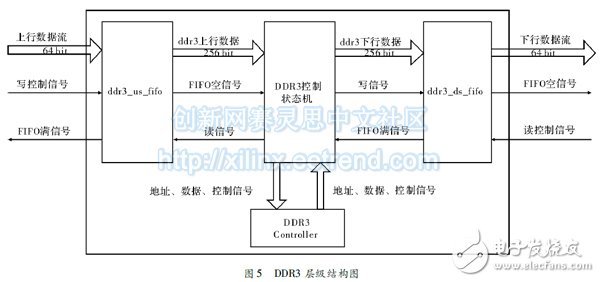

通常情况下, DDR3 SDRAM 存储器仅用作数据的存, 可以将 2 GB 的 DDR3 SDRAM 成一个 虚拟的 FIFO, 如图 5 所示, 并将这个虚拟的 FIFO 划分 为上行 FIFO 和下行 FIFO 两部分。

3 实验结果

为验证 DDR3 控制器 IP 核的正确性, 将生成的代 码添加到 ISE 工程前对采用 MIG 自动生成的测试模 块在 Xilinx ISE14.2 编程环境下进行功能仿真验证。

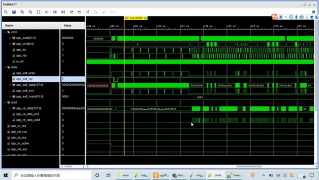

该模块可以向存储器发出一系列读写命令, 并对写人 的数据和读回的数据进行比较, 从而验证控制器的正确性, 仿真结果如图 6 所示。 从图 6 可以看到 phy_init_done 信号置 1 表明初始化完成, 否则为 0。 只有当app_en = 1 和 app_rdy = 1, app_cmd 和 app_addr 才能写人成功。 当 app_cmd = 000 时, 当前为写操作; 当 app_ cmd = 001 时, 当前为读操作。 突发长度 BL 的值设置 为 8, 地址位每增加 64, 数据端口同时写人两个 256 位 的数据, 可以通过 error 这个比较信号验证 DDR3 控制 器正确与否, 在检测出读写数据项的同时该信号输出 低电平。 从仿真结果可以看出比较信号 error 输出始 终为低电平, 说明写人和读取的数据相同, 所以该测试 模块仿真通过。

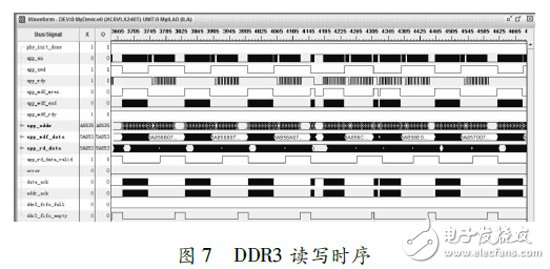

为确保设计的可行性和可靠性, 对设计的控制器 进行约束和综合实现, 将产生的 bit 文件下载到 FPGA 进行硬 件 测 试。 硬 件 测 试 过 程 采 用 Xilinx 公 司 的 XC6SLX240T FPGA 以及 Micron 的容量为 1 GB、 数据位 宽 64 bit、 含 10 位列地址线、 14 位行地址线和 3 位 Bank 地址线的 MT4JSF12864HZ 芯片。 Xilinx 提供了一个集 成于 ISE 软件中的 FPGA 片上调试工具 Chipscope, 它 可以捕获和显示实时信号, 观察在系统设计中的硬件 和软件之间的相互作用。 其原理是设定采样点数, 实 时采用数据并存储到 FPGA 片内的 RAM 中, 然后通过 JTAG 接口传送到 ISE 来显示。 由于 RAM 容量有限, 一次采样到的数据也有限, 因此在硬件测试时, 以循环 读写的方式进行读写数据指令的执行, 以便在逻辑分 析仪中捕获到数据。 对写人数据和读回数据进行比较 时, 用户可以通过 error 这个比较信号验证 DDR3 控制 器的正确与否, 在检测出读写数据项同时该信号输出 低电平。 用调试工具 Chipscope 捕获到的数据以及指 示和相关控制信号如图 7 所示, 读写比较信号 error 输出始终为低电平, 说明写人和读取的数据相同, 硬件验证通过。

4 结束语

通过对 DDR3 操作原理的分析, 给出了 DDR3 控 制器的设计及实现。 将 DDR3 控制器在 Xilinx 公司的 Virtex - 6 系列 FPGA 芯片上实现, 在板卡上能够控制 Micron 公司的 DDR3 芯片稳定地读写数据。 经测试验 证该 DDR3 控制器的可行性, 其工作稳定可靠, 占用逻 辑资源较少, 且具有较高的可移植性以及简单的用户 接口, 在此基础上进行系统开发, 将缩短系统开发周 期, 同时也降低了系统成本。

电子发烧友App

电子发烧友App

评论