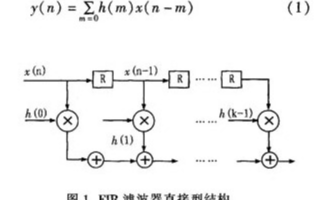

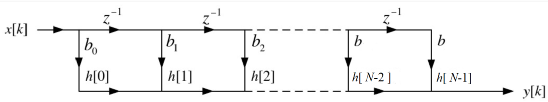

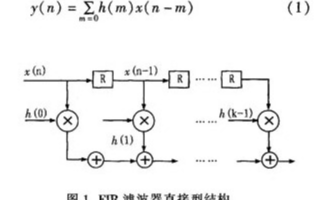

FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。##全并行FIR滤波器结构

2014-06-27 10:02:56 8178

8178 流水线是为了提高效率,能并发同时进行多个任务。

2023-09-05 15:39:56 1112

1112

1、FIR 滤波器是在数字信号处理(DSP)中经常使用的两种基本的滤波器之一,另一个为IIR滤波器。 2、FIR代表有限冲激响应(Finite Impulse Response)的简称。 3

2011-09-24 16:05:53

,所以经济而效率高。但是这个高效率是以相位的非线性为代价的。选择性越好,则相位非线性越严重。相反,FIR滤波器却可以得到严格的线性相位,然而由于FIR滤波器传输函数的极点固定在原点(输出只与有限项输入

2018-03-12 13:21:07

,所以经济而效率高。但是这个高效率是以相位的非线性为代价的。选择性越好,则相位非线性越严重。相反,FIR滤波器却可以得到严格的线性相位,然而由于FIR滤波器传输函数的极点固定在原点(输出只与有限项输入

2016-08-08 08:49:32

考虑来加以选择。从使用要求上来看,在对相位要求不敏感的场合,如语言通信等,选用IIR较为合适,这样可以充分发挥其经济高效的特点;对于图像信号处理,数据传输等以波形携带信息的系统,则对线性相位要求较高,采用FIR滤波器较好。当然,在实际应用中可能还要考虑更多方面的因素。

2019-06-27 04:20:31

数字滤波器的类型有FIR(有限长冲击与IIR(无限长。离散数字系统中,滤波器的表述为差分方程。FIRFIR基本特性:FIR 滤波器永远是稳定的(系统只有零点);FIR 滤波器的冲激响应是有限长序列

2021-08-17 06:19:17

第一个问题的基础上,我是设置unsigned还是signed?3、滤波器的设计,我要给他什么样子的输入,仿真看得出什么样子的结果?部分代码如下

2017-05-09 14:18:17

本文将简单介绍FIR滤波器的原理,详细介绍使用Verilog HDL设计并行FIR滤波器的流程和方法。接下来几篇会介绍串行结构FIR的Verilog设计、使用Quartus和Vivado的IP核

2020-09-25 17:44:38

流水线技术基本原理是什么?设计DSP流水线应注意哪些问题?

2021-04-28 06:10:03

图中的DFG(Data Flow Graph)节点已经标出了传输延迟,求该电路中流水线寄存器的最佳放置位置?求问大神解答这个题

2021-11-20 11:02:57

本帖最后由 eehome 于 2013-1-5 09:44 编辑

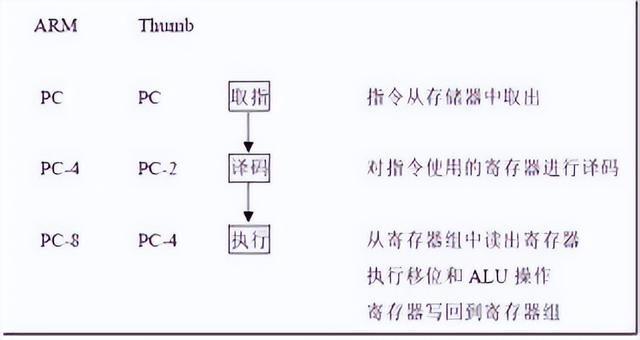

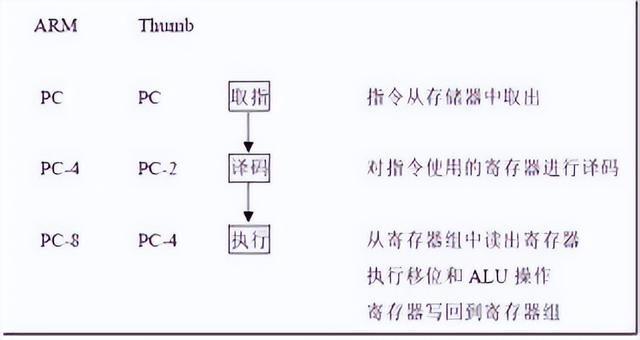

流水线指令及RISC

2012-08-17 15:49:58

看到汇编中很多关于程序返回与中断返回时处理地址都很特别,仔细想想原来是流水线作用的效果。所以,决定总结学习下ARM流水线。ARM7处理器采用3级流水线来增加处理器指令流的速度,能提供0.9MIPS

2021-07-16 06:53:06

ARM 系列的流水线设计都不同。流水线是一种设计技术或过程,它在提高计算机和微控制器处理器中的数据处理效率方面发挥着重要作用。通过将处理器保持在一个连续的获取、解码和执行过程中,称为

2022-04-11 17:23:19

C66 的DSP核有几级流水线的概念吗? 如果有该怎么理解,是几级流水线?

2018-06-21 01:28:01

令预取、 译码、 执行、 写回结果, openrisc采用的是 5 级整数流水线。当然它们的核心思想都是利用并行执行提高效率。总结一下,流水线就是插入寄存器,以面积换取速度。`

2020-10-26 14:38:12

一种新颖的环路内去块效应滤波器设计,设计中采用5阶流水线的去块效应模块,利用混合滤波顺序与打乱的存储更新机制的方法提高了流水线畅顺性,滤波一个16×16大小的宏块仅需要198个时钟周期。

2021-04-12 06:35:37

FIR滤波器如何定义?为什么要使用FIR滤波器?

2021-04-06 07:48:45

如何理解fpga流水线

2015-08-15 11:43:23

前段时间发了个关于fpga的PID实现的帖子,有个人说“整个算法过程说直白点就是公式的硬件实现,用到了altera提供的IP核,整个的设计要注意的时钟的选取,流水线的应用”,本人水平有限,想请教一下其中时钟的选取和流水线的设计应该怎么去做,需要注意些什么,请大家指导一下。

2015-01-11 10:56:59

本文首先介绍了FIR滤波器和脉动阵列的原理,然后设计了脉动阵列结构的FIR滤波器,画出电路的结构框图,并进行了时序分析,最后在FPGA上进行验证。结果表明,脉动阵列的模块化和高度流水线的结构使FIR

2021-04-20 07:23:59

流水线模数转换器(ADC)有哪些优点?流水线ADC中常用的运算放大器有哪些?流水线ADC的放大器结构及工作原理是什么?

2021-04-22 06:18:28

设计实现低通FIR滤波器一步设计和实现过滤器获得滤波器系数可调谐低通FIR滤波器高级设计选项:最佳非等效低通滤波器Equiripple设计增加阻带衰减最小相位低通滤波器设计使用多级技术的最小

2018-08-23 10:00:16

实现FPGA数字下变频的多类滤波器分组级联技术分析1 引 言 本文针对以下高效算法做了总结,进行合理的分组级联并引入流水线技术以便于在FPGA上实现。数字下变频(DDC)就是通过混频、抽取和滤波等

2009-10-23 10:26:53

一篇文章带你分析图像传感器与软件图像处理流水线。

2021-04-27 06:28:00

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-23 06:39:46

相对无限冲击响应(IIR)滤波器,有限冲击响应(FIR)能够在满足滤波器幅频响应的同时获得严格的线性相位特性,而数据通信、语音信号处理等领域往往要求信号在传输过程中不能有明显的相位失真,所以FIR

2019-08-27 07:16:54

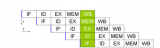

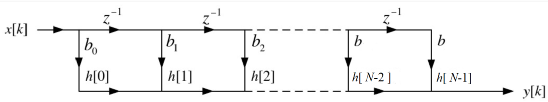

: 2.1 FIR数字滤波器与流水线结构 现代微处理器、数字信号处理器、高速数字系统设计中都广泛应用了流水线(Pipelining)技术,其核心设计思想是把一个周期内执行的逻辑操作分成几步较小的操作,在

2011-02-24 14:20:18

作Stretch计算机)。后来的CDC 6600同时采用了流水线和多功能部件。到了20世纪80年代,流水线技术成为RISC处理器设计方法中最基本的技术之一。RISC设计方法的大部分技术都直接或者间接以提高流水线

2023-03-01 17:52:21

现在的CPU处理器一般都是超流水线工作,动不动就是10级以上流水线,超高主频,这两者之间有什么关系呢?今天就跟大家科普下CPU流水线的工作原理,以及他们之间的关系。说到流水线,很多人会想到富士康

2021-12-15 06:17:45

[table=98%][tr][td]看到很多资料里说“利用流水线的设计方法,可大大提高系统的工作速度。”这是一个教材里很常用的例程:(1)非流水线实现方式module adder_8bits

2017-09-26 23:29:48

在ARM中,关于 LDR流水线,分支流水线,中断流水线,其和 PC 之间的关系一直没整明白,求大神详解!!!

2019-04-30 07:45:25

针对并行爬虫系统在多任务并发执行时所遇到的模块间负载平衡问题,提出流水线负载平衡模型(PLB),将不同的任务抽象为独立模块而达到各模块的处理速度相等,采用多线程的方式

2009-03-31 10:19:30 19

19 流水线结构的高效SAR快视成像处理器

2009-05-08 17:16:47 23

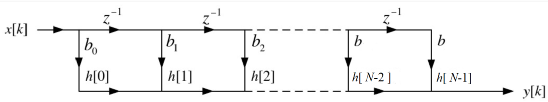

23 并行FIR滤波器具有速度快、容易设计的特点,但是要占用大量的资源。在多阶数的亚高频系统设计中,使用并

2009-07-21 16:55:06 0

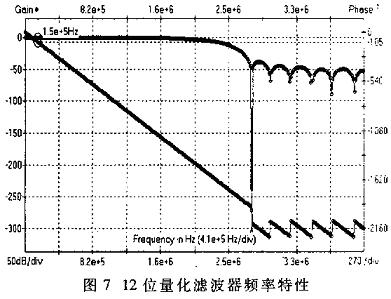

0 本文综合介绍了基于FPGA 软件Quartus II 和MATLAB 的FIR 滤波器的设计仿真,将两大软件综合运用后大大缩减了设计研发的时间,在算法结构上利用了流水线等优化方式。

2009-11-30 14:21:09 117

117 使用软件仿真硬件流水线是很耗时又复杂的工作,仿真过程中由于流水线的冲突而导致运行速度缓慢。本文通过对嵌入式处理器的流水线, 指令集, 设备控制器等内部结构的分析和

2009-12-31 11:30:21 9

9 流水线技术在高速数字电路设计中的应用

2010-07-17 16:37:21 6

6 什么是fir数字滤波器

Part 1: Basics1.1 什么是FIR滤波器?FIR 滤波器是在数字信号处理(DSP)中经常使用的两种

2008-01-16 09:42:22 16243

16243 FIR并行滤波器设计

数字滤波器可以滤除多余的噪声,扩展信号频带,完成信号预调,改变信号的特定频谱分量,从而得到预期的结果。数字滤波器在DVB、

2008-01-16 09:47:09 1270

1270

高效FIR滤波器的设计与仿真-基于FPGA

摘要:该文在介绍有限冲激响应(FIR)数字滤波器理论及常见实现方法的基础上,提出了一种基于FPGA的高效实现方案。

2008-01-16 09:56:02 1456

1456

摘要: 提出了一种采用现场可编码门阵列器件(FPGA)并利用窗函数法实现线性FIR数字滤波器的设计方案,并以一个十六阶低通FIR数字滤波器电路的实现

2009-06-20 14:05:46 1057

1057

什么是流水线技术

流水线技术

2010-02-04 10:21:39 3702

3702 流水线中的相关培训教程[1]

学习目标

理解流水线中相关的分类及定义;

2010-04-13 15:56:08 869

869 流水线中的相关培训教程[3]

(1) 写后读相关(RAW:Read After Write) (命名规则) :j 的执行要用到 i 的计算结果,当它们在流水线中重叠执行时,j 可

2010-04-13 16:02:57 773

773 流水线中的相关培训教程[4]

下面讨论如何利用编译器技术来减少这种必须的暂停,然后论述如何在流水线中实现数据相关检测和定向。

2010-04-13 16:09:15 4272

4272 基于流水线技术,利用FPGA进行并行可重复配置高精度的 FIR滤波器 设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用这种FIR滤波器的设计方法可以充分发挥FPGA的优势。

2011-07-18 17:09:28 63

63 cpu流水线技术是一种将指令分解为多步,并让不同指令的各步操作重叠,从而实现几条指令并行处理,以加速程序运行过程的技术。

2011-12-14 15:29:24 4476

4476 电镀流水线的PLC控制电镀流水线的PLC控制电镀流水线的PLC控制

2016-02-17 17:13:04 35

35 基于MATLAB的FIR滤波器设计与滤波。

2016-12-14 22:08:25 63

63 装配流水线控制系统设计

2016-12-17 15:26:59 13

13 基于位并行DA结构的高速FIR滤波器_周云

2017-01-07 21:39:44 4

4 流水线状态机20进制,101序列检测,8位加法器流水线的程序

2017-05-24 14:40:47 0

0 线性相位FIR滤波器的对称性减小了硬件规模;利用分割查找表的方法减小了存储空间;采用并行分布式算法结构和流水线技术提高了滤波器的速度,在FPGA上实现了该滤波器。

2017-11-24 15:17:27 2942

2942 本文将讨论处理器的一个重要的基础知识:流水线。熟悉计算机体系结构的读者一定知道,言及处理器微架构,几乎必谈其流水线。处理器的流水线结构是处理器微架构最基本的一个要素,犹如汽车底盘对于汽车一般具有基石性的作用,它承载并决定了处理器其他微架构的细节。

2018-04-08 08:16:00 21823

21823

颜色表示了不同阶段的可配置性或可编程性:绿色表示该流水线阶段是完全可编程控制的,黄色表示该流水线阶段可以配置但不是可编程的,蓝色表示该流水线阶段是由GPU固定实现的,开发者没有任何控制权。实线表示该shader必须由开发者编程实现,虚线表示该Shader是可选的.

2018-05-04 09:16:00 3613

3613

据通路和单周期没有什么太大区别,而且也是每个时钟周期都有一条指令执行结束。但是他又和多周期CPU一样一条指令需要多个时钟周期完成。而同时使这两条条件同时满足的就是流水线技术了。先上一张图由于在多周期CPU中,比如

2018-07-16 09:20:07 5448

5448 1914年福特在高地公园引入流水线的时候,一种全新的技术方式出现了。尽管此前流水线也屡屡冒头,但福特却是将其真正转化为一门工厂的必备技能。随后一百多年,任工业技术如何发展,流水线岿然不动,以其强大的生命力,证明了它才是“铁打营盘百年流水线”。

2018-08-27 09:20:00 1620

1620 ,并暂存中间数据的方法。 目的是将一个大操作分解成若干的小操作,每一步小操作的时间较小,所以能提高频率,各小操作能并行 执行,所以能提高数据吞吐率(提高处理速度)。 二. 什么时候用流水线设计 使用流水线一般是时序比较紧张

2018-09-25 17:12:02 4370

4370 自动化流水线是一个统称,包括组装流水线、皮带流水线、链板线、插件线等等,主要通过自动化系统来操作运行,不需要人工操作。

2019-05-22 06:06:00 6328

6328 流水线的工作方式就象工业生产上的装配流水线。在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条X86指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。

2019-11-29 07:06:00 2251

2251 流水线的平面设计应当保证零件的运输路线最短,生产工人操作方便,辅助服务部门工作便利,最有效地利用生产面积,并考虑流水线安装之间的相互衔接。为满足这些要求,在流水线平面布置时应考虑流水线的形式、流水线安装工作地的排列方法等问题。

2019-11-28 07:07:00 2039

2039 流水线在工业生产中扮演着重要的角色,优化流水线直接关系着产品的质量和生产的效率,因此成为企业不得不关注的话题。

2019-11-28 07:05:00 2088

2088 流水线又称为装配线,一种工业上的生产方式,指每一个生产单位只专注处理某一个片段的工作。以提高工作效率及产量;按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2019-11-28 07:04:00 3232

3232 流水线主要是一种硬件设计的算法,如第一条中表述的流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器,并暂存中间数据的方法。

2019-11-18 07:05:00 1853

1853 ,有必要在性能和实现复杂性之间做出选择,也就是选择不同的滤波器实现结构。这里运用并行流水线结构来实现速度和硬件面积之间的互换和折衷。

2020-03-04 09:22:01 3004

3004

一、背景 自20世纪初美国人亨利路福特首次采用流水线的生产方法至今,流水线的发展已经历了百年。 由于流水线作业的高效,稳定等优势,不断被应用于各类生产型企业。这个过程中不断衍生优化,逐渐形成了单一产品流水线

2020-11-02 13:55:21 1294

1294 L倍,其中L为并行的路数,并且运算延迟小。首先从理论上分析了基于多相滤波器的并行滤波原理,并以八路并行为例,对FIR滤波运算做了浮点仿真验证。然后用经典符号数表示以及优化定点滤波器系数,并针对滤波器系数设计了流水线结构。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 15

15 L倍,其中L为并行的路数,并且运算延迟小。首先从理论上分析了基于多相滤波器的并行滤波原理,并以八路并行为例,对FIR滤波运算做了浮点仿真验证。然后用经典符号数表示以及优化定点滤波器系数,并针对滤波器系数设计了流水线结构。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 EE-383:基于MDMA的双SHARC+并行流水线音频直通

2021-04-29 17:30:34 0

0 所谓流水线处理,如同生产装配线一样,将操作执行工作量分成若干个时间上均衡的操作段,从流水线的起点连续地输入,流水线的各操作段以重叠方式执行。这使得操作执行速度只与流水线输入的速度有关,而与处理所需

2021-05-27 16:57:52 2251

2251 按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2021-07-05 11:12:18 6087

6087

在工程建造中,滚筒流水线演着重要的角色。在一些工程建造过程中,经常看到滚筒流水线的身影。在工业不断发展下的今天,滚筒流水线日益增长,走向多元化。滚筒流水线能够长距离的输送,而且支持重量大的货物。

2021-07-08 09:32:56 1423

1423 LED生产流水线输送形式分为平面直线传输流水线、各种角度平面转弯传输流水线、斜面上传流水线、斜面下传流水线这四种输送方式,企业也是可以根据LED灯具生产状况选择合适自己的LED生产流水线输送方式。选择LED生产流水线时应了解流水线各部分组成及功用。

2021-08-06 11:53:51 786

786 昀通科技流水线式UVLED固化炉在工作中可以与生产线对接,配合流水线生产达到快速固化的效果。需要固化的器材在经过UV隧道式固化炉时,使其受到流水线内UV固化光源的照射,让器材上的胶水或油墨所含的光引发剂产生反应,在几秒的时间内完成固化。

2021-09-13 14:16:29 1254

1254 流水线一、定义流水线是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。各种部件同时处理是针对不同指令而言的,他们可同时为多条指令的不同部分进行工作。• 把一个重复的过程分解为若干个子过程

2021-10-20 20:51:14 6

6 1989 年推出的 i486 处理器引入了五级流水线。这时,在 CPU 中不再仅运行一条指令,每一级流水线在同一时刻都运行着不同的指令。这个设计使得 i486 比同频率的 386 处理器性能提升了不止一倍。

2022-09-22 10:04:23 1258

1258 stage:和声明式的含义一致,定义流水线的阶段。Stage 块在脚本化流水线语法中是可选的,然而在脚本化流水线中实现 stage 块,可以清楚地在 Jenkins UI 界面中显示每个 stage 的任务子集。

2023-01-13 15:34:18 747

747 流水线型ADC是采样速率从几Msps到100Msps+的首选架构。设计复杂性仅随位数线性(非指数)增加,因此同时为转换器提供高速、高分辨率和低功耗。流水线ADC在广泛的应用中非常有用,尤其是在数

2023-02-25 09:28:18 3426

3426

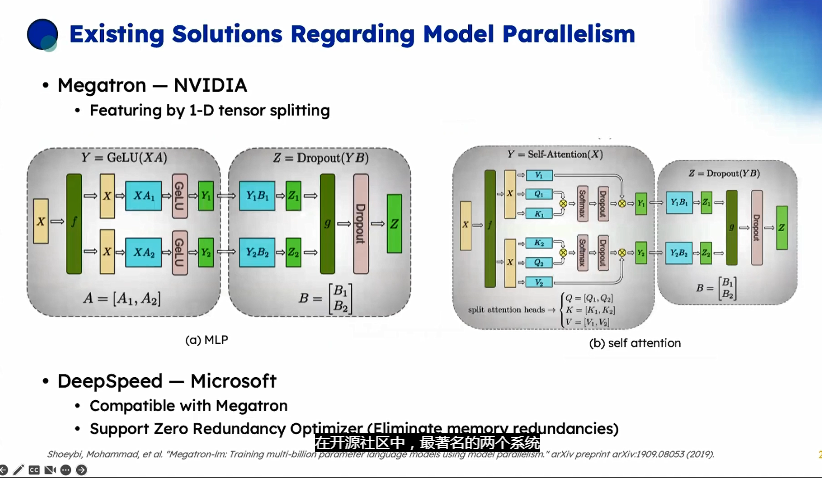

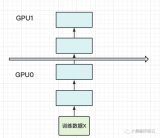

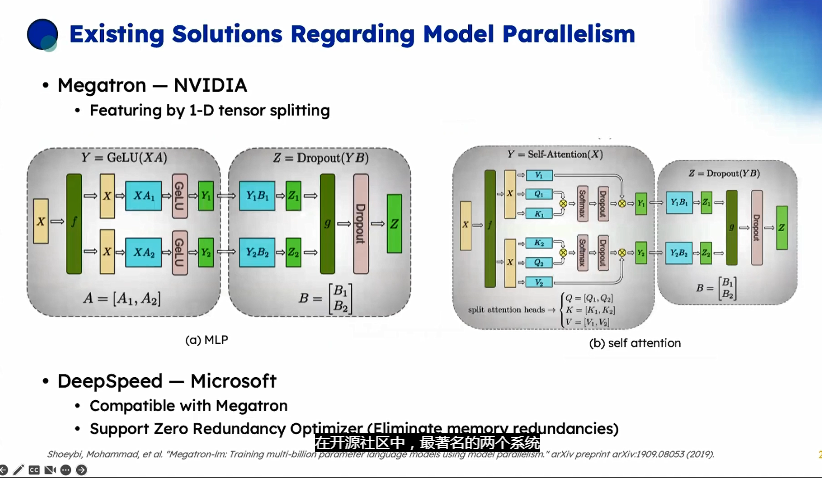

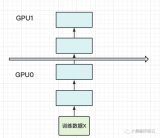

张星并行和流水线并行技术通常被描述为模型并行,在开源社区中,最著名的两个系统是NVIDIA的Megatron- M和Microsoft的DeepSpeed。

2023-03-23 17:21:29 1395

1395

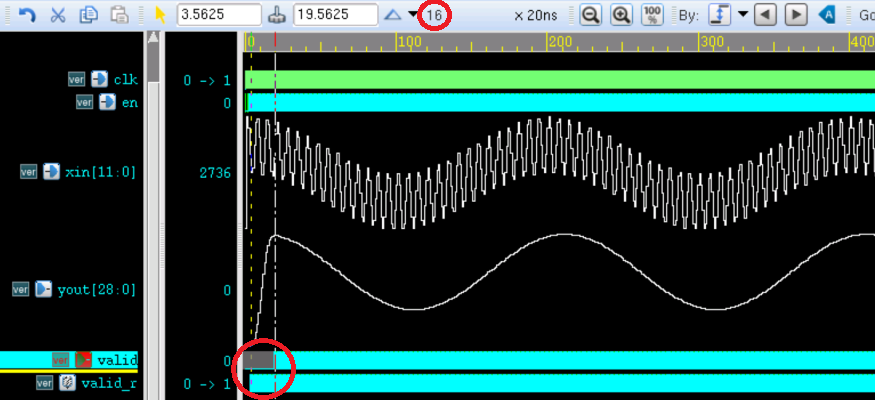

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。FIR 滤波器具有严格的线性相频特性,同时其单位响应是有限长的,因而是稳定的系统,在数字通信、图像处理等领域都有着广泛的应用。

2023-03-27 11:33:53 618

618

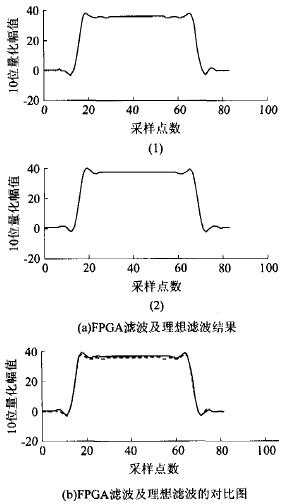

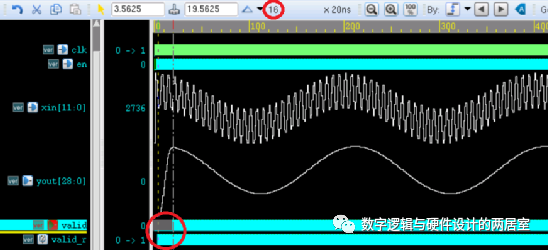

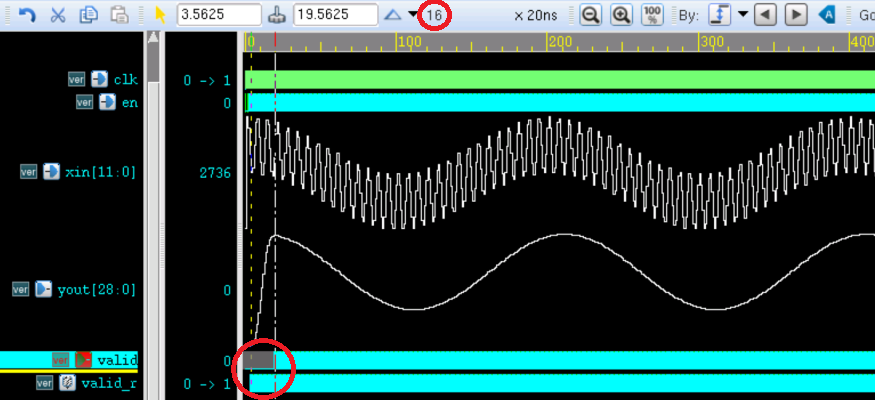

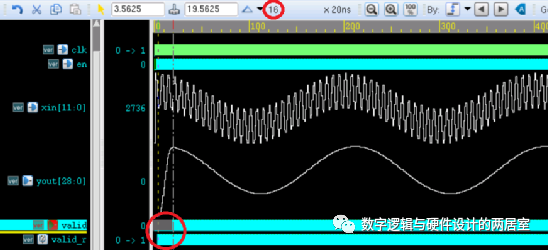

设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR 滤波器后,高频信号 7.5MHz 被滤除,只保留 250KMHz 的信号。

2023-03-27 11:36:46 548

548

jenkins 有 2 种流水线分为声明式流水线与脚本化流水线,脚本化流水线是 jenkins 旧版本使用的流水线脚本,新版本 Jenkins 推荐使用声明式流水线。文档只介绍声明流水线。

2023-05-17 16:57:31 613

613 本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 653

653

和充沛优质的硬件资源 算法的迭代创新 在大模型训练这个系列里,我们将一起探索学习几种经典的分布式并行范式,包括 流水线并行(Pipeline Parallelism),数据并行(Data

2023-05-25 11:41:21 625

625

点击上方 蓝字 关注我们 本文将回顾对称 F IR 滤波器 的高效 FPGA 实现的注意事项。 本文将推导对称 FIR 滤波器的模块化流水线结构。我们将看到派生结构可以使用 Xilinx

2023-05-26 01:20:02 441

441

但在实际应用中,流水线并行并不特别流行,主要原因是模型能否均匀切割,影响了整体计算效率,这就需要算法工程师做手调。因此,今天我们来介绍一种应用最广泛,最易于理解的并行范式:数据并行。

2023-05-26 14:40:20 532

532

设计参数不变,与并行 FIR 滤波器参数一致。即,输入频率为 7.5 MHz 和 250 KHz 的正弦波混合信号,经过 FIR 滤波器后,高频信号 7.5MHz 被滤除,只保留 250KMHz 的信号。

2023-06-01 11:08:38 532

532

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。

2023-06-01 11:11:34 822

822

数字滤波器是数字信号处理中最常用的一种技术,可以对数字信号进行滤波、降噪、增强等处理,其中最常见的两种数字滤波器是IIR滤波器和FIR滤波器。本文将从IIR滤波器和FIR滤波器的原理、特点和应用等方面进行详细介绍,以便更好地理解两种滤波器的区别。

2023-06-03 10:21:43 12909

12909 stage:和声明式的含义一致,定义流水线的阶段。Stage 块在脚本化流水线语法中是可选的,然而在脚本化流水线中实现 stage 块,可以清楚地在 Jenkins UI 界面中显示每个 stage 的任务子集。

2023-07-20 16:43:16 446

446

电子发烧友App

电子发烧友App

评论