在近几年里,随着微电子行业的不断发展,MCU的内核也在突飞猛进的革新,也是由于工程师们对MCU的选型也提出了更高的功能和性能方面的需求。嵌入式MCU选型主要是以性能和外围功能为主。下面我们来主要对Cortex-A7处理器性能和外围功能进行分析。

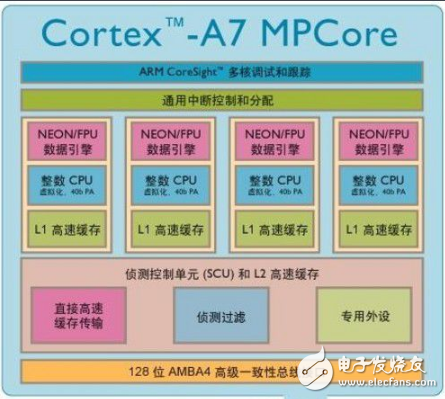

关于Cortex-A7处理器,曾经被评为是ARM 迄今为止开发的最有效的应用处理器它显著扩展了 ARM 在入门级智能手机、平板电脑以及其他高级移动设备方面的低功耗领先地位。Cortex-A7 处理器是一种由ARM公司推出的基于ARMv7-A架构的高能效处理器,采用28nm/40nm制造工艺,可实现单核多核MCU。该处理器与其他Cortex-A系列处理器开发的程序完全兼容,Cortex-A7 处理器的体系结构和功能集与 Cortex-A15 处理器完全相同,采用了包括虚拟化、大物理地址扩展 (LPAE) NEON 高级 SIMD 和 AMBA 4 ACE 一致性等全新技术。Cortex-A7 处理器着重考虑了性能与功耗间的平衡。

不同这处在于,Cortex-A7 处理器的微体系结构侧重于提供最佳能效,因此这两种处理器可在big.LITTLE(大小核大小核心伴侣结构)配置中协同工作,从而提供高性能与超低功耗的终极组合。单个Cortex-A7处理器的能源效率是ARM Cortex-A8处理器的5倍,性能提升50%,而尺寸仅为后者的五分之一。

下载发烧友APP

关注电子发烧友微信

关注发烧友课堂

相关推荐

甲骨文与AMD合作将AMD EPYC霄龙处理器应...

近日,在甲骨文(Oracle )OpenWorld 2018大会中,甲骨文宣布将与AMD合作,将AM...

英特尔10nm工艺处理器和AMD7nm处理器哪个...

AMD上周发布的财报虽然实现了连续5个季度的营收增长,同比净利润大涨67%,不过营收同比只增长了4%...

AMD第二代锐龙两款新品正式上市

10月29日晚间,AMD第二代锐龙ThreadRipper(俗称线程撕裂者)家族的两款新品正式上市,...

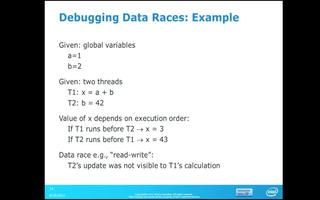

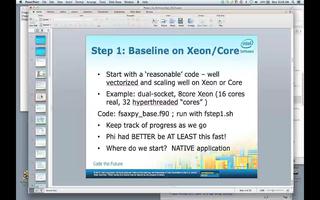

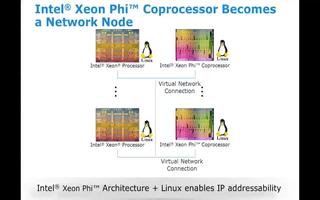

使用GNU调试器在英特尔至强融核协处理器上进行调...

第1部分,共2部分 - 在英特尔®至强融核™协处理器上进行调试:使用GNU项目调试器(GBD)

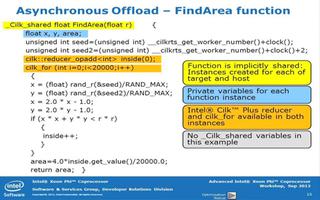

高级英特尔至强融核协处理器研讨会:基础知识

显式和隐式记忆模型; 每种内存模型的高级用法,包括异步卸载和缓冲; BKM可以在KNC上实现内...

Intel的Q3财报出炉,192亿美元的营收创造...

展望未来,Intel调高了2018年营收预期,比1月份估计的数字高出60多亿美元。但谨慎的Swan表...

传骁龙855处理器已完成流片 使用台积电7nm工...

随着麒麟980以及苹果A12处理器的上市,全球智能手机处理器已经进入7nm时代,剩下的两款7nm芯片...

国外拆解团队iFixit已经对iPhone XR...

iPhone XR也支持A12仿生处理器、无边框显示屏以及用于面容ID和动话表情的原深感摄像头,但屏...

魅族Note 8已发布利民手机魅族Note 8的...

10月25日魅族在线上举行了魅族 Note 8新品发布会,会上正式发布了千元国民拍照手机魅族 Not...

Silexica最新版SLX解决方案可优化软硬件...

业界首款解决方案,用来分析用于 RISC/FPGA 设计空间探索的 C/C ++ 代码,从而优化硬件...

酷睿i9-9980XE跑分曝光 一万六买个新的1...

Intel日前发布了第二代X系列发烧处理器,或者叫第九代酷睿X。虽然工艺、架构、最多核心数都没变,但...

微软晒Windows数据中心级机器 一共拥有多达...

微软近日发表了一篇介绍Windows系统内核的博文,期间为了展示Windows的强大扩展性,放出了一...

海得逻捷科技发布了仅重152克的SAM-60超紧...

海得逻捷科技面向TDOA系统提供了系统框架软件TDOAStudio,支持不同节点数的TDOA系统部署...

为什么酷睿i9-9900K比AMD的16核线程撕...

英特尔的九代酷睿处理器上周已经解禁了,三款处理器中最引人注目的当然是酷睿i9-9900K,它不仅是8...

联发科宣布推出曦力P70系统单晶片 将在11月上...

联发科技 24 日宣布推出曦力 P70(Helio P70)系统单晶片,其结合 CPU 与GPU的升...

高通正式推出全新的高通骁龙675移动平台,采用了...

除了在游戏、拍摄和AI体验方面的提升之外,骁龙675还支持:基于DSP的安全方案,在通过人脸识别解锁...

iPhone XR首销卖的如何?iPhone在存...

昨天,苹果官方宣布的消息显示,iPhone XR这款手机首批货源用了4天时间全部卖完,而从产业链的爆...

高通发布骁龙675处理器 AI应用的整体性能可提...

高通在香港正式发布了骁龙675处理器,其定位接近骁龙670和骁龙710。骁龙675基于三星11nm ...

三星首款搭载骁龙710处理器的机型或于明年1月面...

据消息,作为华为在智慧城市领域的合作方之一,云天励飞也参与了这次的华为全联接大会,并加入了华为推出的...

英特尔官方辟谣10纳米处理器终止开发谣言 并称执...

针对媒体报导10纳米处理器Cannon Lake已经终止开发,英特尔周一推文澄清报导不实,并称目前执...

国外玩家使用各种方式将i9-9900K处理器温度...

相比去年的八代酷睿,英特尔的九代酷睿处理器继续增加核心数,弥补了多核性能与AMD锐龙的差距,同时单核...

Arm DesignStart加速基于Linux...

Arm DesignStart使开发者得以不须承担评估的授权费用,就可透过此计划授权进行先期开发,甚...

iPhone XR正式开订,iPhone XR的...

其实对于iPhone XR的性能我们是不应该怀疑的,首先本身硬件标准就跟iPhone XS系列一样,...

麒麟990处理器或采用台积电EUV技术 7纳米+...

日前,才在英国伦敦发布会上展出4款Mate 20系列手机,以及新款麒麟980处理器的华为,根据外电报...

英特尔酷睿处理器发展史 14mm++工艺是如何爆...

从2009年发布酷睿i7-870开始到前不久的全球秋季发布会,英特尔的酷睿智能处理器家族一共出了九代...

iPhoneXR未能如预期热销,iPhoneXR...

iPhoneXS和iPhoneXS MAX在过高定价无疑影响了它的销售,它们上市之后并没能延续去年的...

九代酷睿处理器PCB厚度增加 对产品有哪些影响

相信大家都还记得,英特尔在Skylake架构的第六代酷睿处理器上换用了比前代产品更薄的PCB,还因此...

AMD回应酷睿i9-9900K评测事件 并表示这...

英特尔在前不久的秋季发布会上推出了九代酷睿,其中酷睿i9-9900K被英特尔称为地球上最好的游戏处理...

Intel危机重重,ARM阵营的野心

从微软与高通宣布合作以来,已有联想、华硕等传统的PC企业宣布将推出骁龙本,不过它们似乎更多是试探,依...

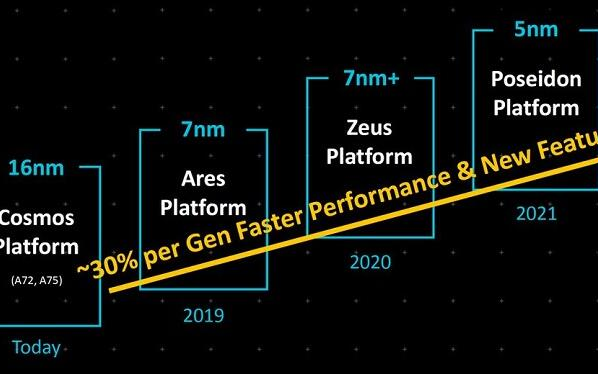

Arm首次公布Neoverse处理器IP路线图

“Arm基础设施事业部高级副总裁兼总经理Drew Henry表示:“今天Arm发布为实现万亿互联设备...

四款中端处理器游戏性能测试 哪款能更好的体验《怪...

卡普空的招牌大作《怪物猎人:世界》在PC平台已经上架已经将近2个月时间,但是其苛刻的硬件需求让不少玩...

ARM推出了一个名叫Neoverse的处理器家族...

ARM 基础设施事业部总经理 Drew Henry 表示:该公司将处理器技术授权给许多企业,通常会用...

赛普拉斯推出搭载Arm处理器的存储平台

赛普拉斯日前宣布推出拥有嵌入式计算能力的新一代存储平台,以满足高级驾驶辅助系统(ADAS)和智能工厂...

AMDZen2架构新处理器将采用7纳米制程 或将...

根据外电报导,在陆续推出14纳米Zen架构处理器、12纳米Zen+架构处理器之后,处理器大厂AMD预...

AMD发布入门级处理器速龙200GE系列 性价比...

日前,AMD发布新一代入门级处理器速龙200GE系列,融合最新的Zen CPU架构、Vega GPU...

英特尔发布9代酷睿处理器,树立游戏标杆

英特尔针对游戏和内容创作推出台式机全线产品,包括全新第九代英特尔®酷睿™和英特尔®酷睿™X系列处理器...

OMAP-L137 C6000 DSP+ARM ...

OMAP-L137器件是一款基于ARM926EJ-S和TMS320C674x DSP内核的低功耗应用处理器。它的功耗显着低于DSP的TMS320C6000平台的其他成员。 OMAP-L137器件使原始设备制造商(OEM)和原始设计制造商(ODM)能够快速推向市场通过完全集成的混合处理器解决方案的最大灵活性,提供强大的操作系统支持,丰富的用户界面和高处理性能。 OMAP-L137器件的双核架构提供了DSP和DSP的优势。精简指令集计算机(RISC)技术,集成了高性能TMS320C674x DSP内核和ARM926EJ-S内核。 ARM926EJ-S是一个32位RISC处理器内核,可执行32位或16位位指令和处理32位,16位或8位数据。核心使用流水线操作,以便处理器和内存系统的所有部分可以连续运行。 ARM内核具有协处理器15(CP15),保护模块以及数据和程序内存管理单元(MMU)表后备缓冲区。 ARM内核具有单独的16 KB指令和16 KB的数据高速缓存。两个内存块都与虚拟索引虚拟标记(VIVT)进行四向关联。 ARM内核还具有8KB的RAM(向量表)和64KB的ROM。 OMAP-L137 DS...

TMS320VC5506 TMS320VC550...

TMS320VC5506定点数字信号处理器(DSP)基于TMS320C55x DSP生成CPU处理器内核。 C55x™DSP架构通过增加并行性和全面关注降低功耗来实现高性能和低功耗。 CPU支持内部总线结构,该结构由一个程序总线,三个数据读总线,两个数据写总线以及专用于外设和DMA活动的附加总线组成。这些总线能够在一个周期内执行最多三次数据读取和两次数据写入。并行地,DMA控制器每个周期最多可以执行两次数据传输,与CPU活动无关。 C55x CPU提供两个乘法累加(MAC)单元,每个单元能够支持17位x 17-单个循环中的位乘法。额外的16位ALU支持中央40位算术/逻辑单元(ALU)。 ALU的使用受指令集控制,提供优化并行活动和功耗的能力。这些资源在C55x CPU的地址单元(AU)和数据单元(DU)中进行管理。 C55x DSP代支持可变字节宽度指令集,以提高代码密度。指令单元(IU)从内部或外部存储器执行32位程序提取,并为程序单元(PU)排队指令。程序单元解码指令,将任务指向AU和DU资源,并管理完全受保护的管道。预测分支功能可避免执行条件指令时的管道冲洗。 5506上的128...

TMS320C6747 定点/浮点数字信号处理器

TMS320C6745 /6747器件是一款基于TMS320C674x DSP内核的低功耗数字信号处理器。它的功耗显着低于TMS320C6000 DSP平台的其他成员。 TMS320C6745 /6747器件使原始设备制造商(OEM)和原始设计制造商(ODM)能够快速推出市场上的设备。高处理性能。 TMS320C6745 /6747 DSP内核采用基于缓存的两级架构。 1级程序高速缓存(L1P)是32 KB直接映射高速缓存,1级数据高速缓存(L1D)是32 KB双向组关联高速缓存。 2级程序高速缓存(L2P)由256 KB内存空间组成,在程序和数据空间之间共享。 L2内存可以配置为映射内存,缓存或两者的组合。虽然系统中的其他主机可以访问DSP L2,但是其他主机可以使用额外的128KB RAM共享内存(仅限TMS320C6747),而不会影响DSP性能。 外设集包括:带管理数据输入/输出(MDIO)模块的10/100 Mbps以太网MAC(EMAC);两个I 2 C总线接口; 3个多通道音频串行端口(McASP),带有16/9串行器和FIFO缓冲器;两个64位通用定时器,每个都可配置(一个可配置为看门狗);可配置的16位主机端口接口(HPI)[仅限TMS3...

Intel处理器价格持续走高 AMD二代锐龙或迎...

Intel近日发布了第九代酷睿的首批三款K系列处理器,8核心16线程、加速5GHz、钎焊散热等都颇为...

曝i9-9900K超频到全核5GHz时最高温度达...

被批评多年之后,Intel终于在九代主流酷睿K系列、九代发烧酷睿X系列上应用了高级钎焊散热材质,淘汰...

Intel将推出一款8核心16线程的移动处理器

AMD锐龙强势诞生以后,Intel就开始在各条产品线上围追堵截,堆积越来越多的核心成为最大法宝,从工...

新创公司推出名为Palm的轻便机,只有信用卡大

Palm的存在并非为了取代手机,而是如智能手表一般的穿戴装置,提供给想要轻便出门的民众「第二台」手机...

魅族将于10月25日在北京召开魅族Note 8新...

日前,工信部有一款信号为 M822Q 的新机通过了入网许可,这款机型很有可能就是魅族 Note 8 ...

向Intel发起重型计算挑战 ARM发布Neov...

ARM 基础设施事业部总经理 Drew Henry 表示:该公司将处理器技术授权给许多企业,通常会用...

英特尔发布第九代 Core 新品:含两款核心芯片...

10 月 8 日,英特尔宣布在秋季新品发布会上重磅发布下一代 PC 游戏处理器 Core i9-99...

全面评测对iPhoneXS系列的实力进行解读

实测结果显示,iPhone XS系列的安兔兔跑分高达332569分,GeekBench单核跑分为48...

iPhone XR在10月19日下午3:01开启...

iPhone XR依旧采用了LCD屏幕,导致四周边框比OLED屏幕的iPhone XS宽一点,其次i...

TMS320C6472 定点数字信号处理器

与其它产品相比 其他 C6000 DSP DSP var link = "zh_CN_folder_p_quick_link_description_features_parametrics"; com.TI.Product.handleQuickLinks('parametric','参数变化','#parametrics',link); TMS320C6472 6 C64x+ 无样片 方框图 (1)...

SM320DM355-EP 数字媒体片上系统 (...

DM355是一款高度集成的可编程平台,适用于数码相机,数码相框,IP安全摄像机,4路数字视频录像机,视频门铃应用程序和其他低成本便携式数字视频应用程序。 DM355旨在为便携式视频设计人员和制造商提供高质量的低成本便携式数字视频解决方案,将高性能MPEG4 HD(720p)编解码器和JPEG编解码器组合在一起,每秒高达50M像素,高品质,低功耗价格非常低。 DM355还可实现与完整数码相机实施所需的大多数其他外部设备的无缝接口。该接口足够灵活,可支持各种类型的CCD和CMOS传感器,信号调理电路,电源管理,DDR /mDDR存储器,SRAM,NAND,快门,光圈和自动对焦电机控制等。 DM355处理器内核是ARM926EJ-S RISC处理器。 ARM926EJ-S是一个32位处理器内核,可执行32位和16位指令,并处理32位,16位和8位数据。核心使用流水线操作,以便处理器和内存系统的所有部分都可以连续运行。 ARM内核包含: 协处理器15(CP15)和保护模块 带有表后备缓冲区的数据和程序存储器管理单元(MMU)。 单独的16K字节指令和8K字节数据缓存。两者都是与虚拟索...

TMS320DM648 TMS320DM648 ...

The TMS320C64x+™ DSPs (including the TMS320DM647/TMS320DM648 devices) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM647, DM648 devices are based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices. Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively. With performance of up to 8800 million instructions per second (MIPS) at a clock rate of 1.1 GH...

TMS320C6746 TMS320C6746 ...

TMS320C6746定点和浮点DSP是一款低功耗应用处理器,该处理器基于C674x DSP内核。该DSP与其他TMS320C6000™平台DSP相比,功耗要小很多。 凭借这款器件,原始设备制造商(OEM)和原始设计制造商(ODM)能够充分利用全集成混合处理器解决方案的灵活性,迅速将兼用稳健操作系统,丰富用户接口和高处理器性能的器件推向市场。 该器件的DSP内核采用基于2级缓存的架构。第1级程序缓存(L1P)是一个 32KB的直接映射缓存,第1级数据缓存(L1D)是一个32KB的2路组相连缓存。第2级程序缓存(L2P)包含256KB的存储空间,由程序空间和数据空间共享.L2存储器可配置为映射存储器,缓存或二者的组合。系统内的其他主机可以访问DSP L2。 外设集包括:1个具有管理数据输入/输出模块(MDIO)的10Mbps /100Mbps以太网介质访问控制器(EMAC); 1个USB2.0 OTG接口; 2个I 2 C总线接口; 1个具有16个串行器和FIFO缓冲器的多通道音频串行端口(McASP) ); 2个具有FIFO缓冲器的多通道缓冲串行端口(McBSP); 2个可配置的64位通用定时器(其中一个可配置...

OMAP-L138 OMAP-L138 Data...

OMAP-L138 C6000 DSP+ARM 处理器 是一款低功耗 应用 处理器,该处理器基于 ARM926EJ-S 和 C674x DSP 内核。该处理器 与其他 TMS320C6000™ 平台 DSP 相比,功耗要小很多。 凭借这款器件,原始设备制造商 (OEM) 和原始设计制造商 (ODM) 能够充分利用全集成混合处理器解决方案的灵活性,迅速将兼具稳健操作系统、丰富用户接口和高处理器性能的器件推向市场。 此器件采用双内核架构(包括一个高性能的 TMS320C674x DSP 内核和一个 ARM926EJ-S 内核),实现了 DSP 与精简指令集计算机 (RISC) 技术二者优势的完美融合。 ARM926EJ-S 是一款 32 位 RISC 处理器内核,可执行 32 位或 16 位指令和处理 32 位、16 位或 8 位数据。该内核采用流水线结构,因此处理器和存储器系统的所有部件能够连续运行。 ARM9 内核配有协处理器 15 (CP15)、保护模块以及具有页表缓冲区的数据和程序存储器管理单元 (MMU)。ARM9 内核配有独立的 16KB 指令缓存和 16KB 数据缓存。这两个缓存均与虚拟索引虚拟标签 (VIVT) 4 路相连。ARM9 内核还配...

SM320DM6446-HIREL HiRel ...

The TMS320DM6446 devices (also referenced as DM6446 and including the SM320DM6446) leverages TIs DaVinci technology to meet the networked media encode and decode application processing needs of next-generation embedded devices. The DM6446 enables OEMs and ODMs to quickly bring to market devices featuring robust operating systems support, rich user interfaces, high processing performance, and long battery life through the maximum flexibility of a fully integrated mixed processor solution. The dual-core architecture of the DM6446 provides benefits of both DSP and Reduced Instruction Set Computer (RISC) technologies, incorporating a high-performance TMS320C64x+ DSP core and an ARM926EJ-S core. The ARM926EJ-S is a 32-bit RISC processor core that performs 32-bit or 16-bit instructions and processes 32-bit, 16-bit, or 8-bit data. The core uses pipelining so that all parts of...

TMS320C5505 定点数字信号处理器

该器件是TI TMS320C5000™定点数字信号处理器(DSP)产品系列的成员,专为低功耗应用而设计。 定点DSP基于TMS320C55x™DSP生成CPU处理器内核。 C55x™DSP架构通过增加并行性和全面关注节能来实现高性能和低功耗。 CPU支持内部总线结构,该结构由一个程序总线,一个32位数据读总线和两个16位数据读总线,两个16位数据写总线以及专用于外设和DMA活动的附加总线组成。这些总线能够在一个周期内执行多达四个16位数据读取和两个16位数据写入。该器件还包括四个DMA控制器,每个控制器有4个通道,为16个独立的通道上下文提供数据移动,无需CPU干预。每个DMA控制器可以在每个周期内并行执行一次32位数据传输,与CPU活动无关。 C55x CPU提供两个乘法累加(MAC)单元,每个单元能够支持17位x单个周期内的17位乘法和32位加法。额外的16位ALU支持中央40位算术/逻辑单元(ALU)。 ALU的使用受指令集控制,提供优化并行活动和功耗的能力。这些资源在C55x CPU的地址单元(AU)和数据单元(DU)中进行管理。 C55x CPU支持可变字节宽度指令集,以提...

SM320DM642-HIREL 视频/成像定点...

The C64x™ DSPs (including the SM320DM642-EP device) are the highest-performance fixed-point DSP generation in the C6000 DSP platform. The DM642 device is based on the second-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture (VelociTI.2™) developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x is a code-compatible member of the C6000 DSP platform. With performance of up to 5760 million instructions per second (MIPS) at a clock rate of 720 MHz, the DM642 device offers cost-effective solutions to high-performance DSP programming challenges. The DM642 DSP possesses the operational flexibility of high-speed controllers and the numerical capability of array processors. The C64x™ DSP core processor has 64 general-purpose registers of 32-bit word length and eight highly in...

TMS320DM6467T 数字媒体片上系统

The TMS320DM6467T (also referenced as DM6467T) leverages TI's DaVinci™ technology to meet the networked media encode and decode application processing needs of next-generation embedded devices. The DM6467T enables OEMs and ODMs to quickly bring to market devices featuring robust operating systems support, rich user interfaces, high processing performance, and long battery life through the maximum flexibility of a fully integrated mixed processor solution. The dual-core architecture of the DM6467T provides benefits of both DSP and Reduced Instruction Set Computer (RISC) technologies, incorporating a high-performance TMS320C64x+ DSP core and an ARM926EJ-S core. The ARM926EJ-S is a 32-bit RISC processor core that performs 32-bit or 16-bit instructions and processes 32-bit, 16-bit, or 8-bit data. The core uses pipelining so that all parts of the processor and memory sy...

TMS320C5504 定点数字信号处理器

该器件是TI TMS320C5000™定点数字信号处理器(DSP)产品系列的成员,专为低功耗应用而设计。 定点DSP基于TMS320C55x™DSP生成CPU处理器内核。 C55x™DSP架构通过增加并行性和全面关注节能来实现高性能和低功耗。 CPU支持内部总线结构,该结构由一个程序总线,一个32位数据读总线和两个16位数据读总线,两个16位数据写总线以及专用于外设和DMA活动的附加总线组成。这些总线能够在一个周期内执行多达四个16位数据读取和两个16位数据写入。该器件还包括四个DMA控制器,每个控制器有4个通道,为16个独立的通道上下文提供数据移动,无需CPU干预。每个DMA控制器可以在每个周期内并行执行一次32位数据传输,与CPU活动无关。 C55x CPU提供两个乘法累加(MAC)单元,每个单元能够支持17位x单个周期内的17位乘法和32位加法。额外的16位ALU支持中央40位算术/逻辑单元(ALU)。 ALU的使用受指令集控制,提供优化并行活动和功耗的能力。这些资源在C55x CPU的地址单元(AU)和数据单元(DU)中进行管理。 C55x CPU支持可变字节宽度指令集,以提...

TMS320C6748 TMS320C6748 ...

TMS320C6748 定点和浮点 DSP 是一款低功耗 应用 处理器,该处理器基于 C674x DSP 内核。该DSP 与其他 TMS320C6000™ 平台 DSP 相比,功耗要小很多。 凭借这款器件,原始设备制造商 (OEM) 和原始设计制造商 (ODM) 能够充分利用全集成混合处理器解决方案的灵活性,迅速将兼具稳健操作系统、丰富用户接口和高处理器性能的器件推向市场。 该器件的 DSP 内核采用基于 2 级缓存的架构。第 1 级程序缓存 (L1P) 是一个 32KB 的直接映射缓存,第 1 级数据缓存 (L1D) 是一个 32KB 的 2 路组相连缓存。第 2 级程序缓存 (L2P) 包含 256KB 的存储空间,由程序空间和数据空间共享。L2 存储器可配置为映射存储器、缓存或二者的组合。尽管系统内的其他主机可访问 DSP L2,但还是额外提供了一个 128KB 的 RAM 共享存储器给其他主机使用,从而避免对 DSP 性能产生影响。 对于支持安全功能的器件,TI 的基本安全启动可为用户保护自主知识产权并防止外部实体修改用户开发的算法。该安全启动流程从一个基于硬件的“信任根”开始,确保代码从一个已知安全的位置开始...

TMS320C6720 TMS320C6727B...

The TMS320C672x is the next generation of Texas Instruments' C67x generation of high-performance 32-/64-bit floating-point digital signal processors. The TMS320C672x includes the TMS320C6727B, TMS320C6726B, TMS320C6722B, and TMS320C6720 devices.(1) Enhanced C67x+ CPU. The C67x+ CPU is an enhanced version of the C67x CPU used on the C671x DSPs. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and floating-point performance per clock cycle. At 350 MHz, the CPU is capable of a maximum performance of 2800 MIPS/2100 MFLOPS by executing up to eight instructions (six of which are floating-point instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision floating-point, and 64-bit double-precision floating-point arithmetic. Efficient Memory System. The memory controller maps the la...

TMS320C6743 定点/浮点数字信号处理器

C6743器件是一款基于C674x DSP内核的低功耗数字信号处理器。与TMS320C6000™DSP平台的其他成员相比,该器件的功耗显着降低。 C6743器件使原始设备制造商(OEM)和原始设计制造商(ODM)能够快速推向市场高处理性能。 C6743 DSP内核采用基于缓存的两级架构。 1级程序高速缓存(L1P)是32 KB直接映射高速缓存,1级数据高速缓存(L1D)是32 KB双向组关联高速缓存。 Level 2程序缓存(L2P)由128 KB的内存空间组成,在程序和数据空间之间共享。 L2内存可以配置为映射内存,缓存或两者的组合。 外设集包括:带管理数据输入/输出(MDIO)模块的10/100 Mbps以太网MAC(EMAC);两个I 2 C总线接口;两个带有14/9串行器和FIFO缓冲器的多通道音频串行端口(McASP);两个64位通用定时器,每个都可配置(一个可配置为看门狗);多达8个16引脚的通用输入/输出(GPIO),具有可编程中断/事件生成模式,与其他外设复用;两个UART接口(一个具有 RTS 和 CTS );三个增强型高分辨率脉冲宽度调制器(eHRPWM)外设;三个32位增强型捕获(eCAP)模块外设,...

TMS320C6745 定点/浮点数字信号处理器

TMS320C6745 /6747器件是一款基于TMS320C674x DSP内核的低功耗数字信号处理器。它的功耗显着低于TMS320C6000 DSP平台的其他成员。 TMS320C6745 /6747器件使原始设备制造商(OEM)和原始设计制造商(ODM)能够快速推出市场上的设备。高处理性能。 TMS320C6745 /6747 DSP内核采用基于缓存的两级架构。 1级程序高速缓存(L1P)是32 KB直接映射高速缓存,1级数据高速缓存(L1D)是32 KB双向组关联高速缓存。 2级程序高速缓存(L2P)由256 KB内存空间组成,在程序和数据空间之间共享。 L2内存可以配置为映射内存,缓存或两者的组合。虽然系统中的其他主机可以访问DSP L2,但是其他主机可以使用额外的128KB RAM共享内存(仅限TMS320C6747),而不会影响DSP性能。 外设集包括:带管理数据输入/输出(MDIO)模块的10/100 Mbps以太网MAC(EMAC);两个I 2 C总线接口; 3个多通道音频串行端口(McASP),带有16/9串行器和FIFO缓冲器;两个64位通用定时器,每个都可配置(一个可配置为看门狗);可配置的16位主机端口接口(HPI)[仅限TMS3...

TMS320C6727 浮点数字信号处理器

The TMS320C672x is the next generation of Texas Instruments C67x family of high-performance 32-/64-bit floating-point digital signal processors. The TMS320C672x includes the TMS320C6727, TMS320C6726, and TMS320C6722 devices.(1) Enhanced C67x+ CPU. The C67x+ CPU is an enhanced version of the C67x CPU used on the C671x DSPs. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and floating-point performance per clock cycle. At 300 MHz, the CPU is capable of a maximum performance of 2400 MIPS/1800 MFLOPS by executing up to eight instructions (six of which are floating-point instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision floating-point, and 64-bit double-precision floating-point arithmetic. Efficient Memory System. The memory controller maps the large on-chip 256K-byte RAM...

TMS320DM365 DaVinci 数字媒体...

开发人员现在可以在数字视频设计中以30fps的速度提供高达720p H.264的像素完美图像,而无需考虑视频格式支持,网络带宽受限新型TMS320DM365数字媒体处理器基于德州仪器(TI)的DaVinci技术,有限的系统存储容量或成本。凭借多格式高清视频,DM365还具有一套外设,可为开发人员节省系统成本。 这款基于ARM9的DM365设备提供高达300 MHz的速度,并支持符合生产要求的H.264,MPEG -4,MPEG-2,MJPEG和VC1 /WMV9编解码器,使客户能够灵活地为其应用选择正确的视频编解码器。这些编解码器由视频加速器驱动,从ARM内核卸载压缩需求,以便开发人员可以利用ARM的最高性能来实现其应用。视频监控设计人员可以实现更高的压缩效率,从而在不影响网络带宽的情媒体播放和相机驱动应用的开发人员,如视频门铃,数字标牌,数字视频录像机,便携式媒体播放器等,可以利用DM365支持的全套编解码器,确保互操作性和产品可扩展性。 /p> 与多格式高清视频一起,DM365可实现与视频应用所需的大多数其他外部设备的无缝接口。图像传感器接口足够灵活,可支持CCD,CMOS和各种其他接口,如BT.656,BT...

TMS320C6722B TMS320C6727...

The TMS320C672x is the next generation of Texas Instruments' C67x generation of high-performance 32-/64-bit floating-point digital signal processors. The TMS320C672x includes the TMS320C6727B, TMS320C6726B, TMS320C6722B, and TMS320C6720 devices.(1) Enhanced C67x+ CPU. The C67x+ CPU is an enhanced version of the C67x CPU used on the C671x DSPs. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and floating-point performance per clock cycle. At 350 MHz, the CPU is capable of a maximum performance of 2800 MIPS/2100 MFLOPS by executing up to eight instructions (six of which are floating-point instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision floating-point, and 64-bit double-precision floating-point arithmetic. Efficient Memory System. The memory controller maps the la...

TMS320DM647 TMS320DM647 ...

The TMS320C64x+™ DSPs (including the TMS320DM647/TMS320DM648 devices) are the highest-performance fixed-point DSP generation in the TMS320C6000™ DSP platform. The DM647, DM648 devices are based on the third-generation high-performance, advanced VelociTI™ very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI), making these DSPs an excellent choice for digital media applications. The C64x+™ devices are upward code-compatible from previous devices that are part of the C6000™ DSP platform. The C64x™ DSPs support added functionality and have an expanded instruction set from previous devices. Any reference to the C64x DSP or C64x CPU also applies, unless otherwise noted, to the C64x+ DSP and C64x+ CPU, respectively. With performance of up to 8800 million instructions per second (MIPS) at a clock rate of 1.1 GH...

TMS320VC5507 定点数字信号处理器

TMS320VC5507定点数字信号处理器(DSP)基于TMS320C55x DSP生成CPU处理器内核。 C55x ?? DSP架构通过增加并行性和全面关注降低功耗来实现高性能和低功耗。 CPU支持内部总线结构,该结构由一个程序总线,三个数据读总线,两个数据写总线以及专用于外设和DMA活动的附加总线组成。这些总线能够在一个周期内执行最多三次数据读取和两次数据写入。并行地,DMA控制器每个周期最多可以执行两次数据传输,与CPU活动无关。 C55x CPU提供两个乘法累加(MAC)单元,每个单元能够支持17位×17-单个循环中的位乘法。额外的16位ALU支持中央40位算术/逻辑单元(ALU)。 ALU的使用受指令集控制,提供优化并行活动和功耗的能力。这些资源在C55x CPU的地址单元(AU)和数据单元(DU)中进行管理。 C55x DSP代支持可变字节宽度指令集,以提高代码密度。指令单元(IU)从内部或外部存储器执行32位程序提取,并为程序单元(PU)排队指令。程序单元解码指令,将任务指向AU和DU资源,并管理完全受保护的管道。预测分支功能可避免执行条件指令时的管道冲洗。 5507上的1...

OMAP3525 应用处理器

OMAP3530和OMAP3525器件基于增强型OMAP 3架构。 OMAP 3架构旨在提供最佳的OMAP 3架构。类视频,图像和图形处理足以支持以下内容: 流媒体视频 视频会议 高分辨率静止图像 该设备支持高级操作系统(HLOS),例如: Linux® Windows®CE < li> Android™ 此OMAP设备包含高性能移动产品所需的最先进的电源管理技术。 以下子系统是其中的一部分设备: 基于ARM Cortex-A8微处理器的微处理器单元(MPU)子系统 带有C64x +数字信号处理器(DSP)内核的IVA2.2子系统< /li> 用于支持显示的3D图形加速的PowerVR SGX子系统(仅限OMAP3530设备) 支持相机图像信号处理器(ISP)端口多种格式和连接到各种图像传感器的接口选项 显示子系统具有多种并发图像处理功能,以及支持各种显示器的可编程接口。显示子系统还支持NTSC和PAL视频输出。 3级(L3)和4级(L4)互连...

TMS320C6727B TMS320C6727...

The TMS320C672x is the next generation of Texas Instruments' C67x generation of high-performance 32-/64-bit floating-point digital signal processors. The TMS320C672x includes the TMS320C6727B, TMS320C6726B, TMS320C6722B, and TMS320C6720 devices.(1) Enhanced C67x+ CPU. The C67x+ CPU is an enhanced version of the C67x CPU used on the C671x DSPs. It is compatible with the C67x CPU but offers significant improvements in speed, code density, and floating-point performance per clock cycle. At 350 MHz, the CPU is capable of a maximum performance of 2800 MIPS/2100 MFLOPS by executing up to eight instructions (six of which are floating-point instructions) in parallel each cycle. The CPU natively supports 32-bit fixed-point, 32-bit single-precision floating-point, and 64-bit double-precision floating-point arithmetic. Efficient Memory System. The memory controller maps the la...

SM320C6415-EP 增强型产品定点数字信...

TMS320C64x ?? DSP(包括SM320C6414-EP,SM320C6415-EP和SM320C6416-EP器件)是TMS320C6000中性能最高的定点DSP产品。 DSP平台。 SM320C64x ?? (C64x ??)设备是基于第二代高性能,先进的VelociTI ??德州仪器(TI)开发的超长指令字(VLIW)架构(VelociTI.2 ??),使这些DSP成为多通道和多功能应用的绝佳选择。 C64x ??是C6000的代码兼容成员?? DSP平台。 C64x器件在500 MHz时钟频率下具有高达4000万条指令/秒(MIPS)的性能,可为高性能DSP编程挑战提供经济高效的解决方案。 C64x DSP具有高速控制器的操作灵活性和阵列处理器的数字功能。 C64x DSP内核处理器有64个32位字长的通用寄存器和8个高度独立的功能单元?? 2个乘法器用于32位结果和6个算术逻辑单元(ALU)??使用VelociTI.2扩展。八个功能单元中的VelociTI.2扩展包括新指令,以加速关键应用程序的性能并扩展VelociTI架构的并行性。 C64x每周期可产生4个32位乘法累加(MAC),总计每秒2400万MAC(MMACS),或每周期8个8位MAC,总计4800 MMACS。 C64x DSP还具有特定于应...

TAS3108 数字音频处理器

TAS3108和TAS3108IA是完全可编程的高性能音频处理器。这些器件使用针对数字音频处理算法优化的高效,定制,多指令编程环境。 TAS3108 /TAS3108IA架构通过使用48位数据路径,28位滤波器系数和带有76位累加器的单周期28×48位乘法器提供高质量音频处理。嵌入式8051微处理器为TAS3108 /TAS3108IA提供算法和数据控制。 TAS3108是用于家庭音频和其他商业应用的商业版本。 TAS3108IA是汽车版,适用于汽车应用。 特性 8通道可编程音频数字信号处理器(DSP) 135-MHz最高速度,> 2800个处理周期采样频率为48 kHz 采样率为32 kHz至192 kHz 48位数据路径和28位系数 单周期,76位乘法累加 每个时钟周期五个同时操作 1022个48位数据存储器字 1022个28位系数存储器字 < li> 3位54位程序RAM字 5.88K 24位延迟存储器字(在48 kHz时为122.5 ms) 15立体声/TDM数据格式 独立输入/输出数据格式 16位,20位,24位和32位字大小 ...

华为Mate20 Pro的性能外观价格详细分析介...

本月可谓是妥妥的新机发布大月,目前已经确定将要发布的新机便高达20余款,而说起最令消费者关注的新机,...

英特尔第九代core处理器正式发布

近期,英特尔在纽约举办了秋季新品发布会,正式带来了第九代Intel Core处理器,正如此前网络所传...

TMS320VC5402A 定点数字信号处理器

TMS320VC5402A定点数字信号处理器(DSP)(以下简称5402A除非另有说明)基于先进的改进型哈佛架构,有一个程序存储器总线和三个数据存储器总线。该处理器提供具有高度并行性的算术逻辑单元(ALU),专用硬件逻辑,片上存储器和其他片上外设。该DSP的操作灵活性和速度的基础是高度专业化的指令集。 独立的程序和数据空间允许同时访问程序指令和数据,提供高度的并行性。可以在单个周期中执行两个读操作和一个写操作。具有并行存储和特定于应用程序的指令的指令可以充分利用该架构。此外,数据可以在数据和程序空间之间传输。这种并行性支持一组强大的算术,逻辑和位操作操作,这些操作都可以在一个机器周期中执行。 5402A还包括管理中断的控制机制, 特性 具有三个独立的16位数据存储器总线和一个程序存储器总线的高级多总线架构 40位算术逻辑单元(ALU)包括一个40位桶形移位器和两个独立的40位累加器 17-×17位并行乘法器耦合到一个40位专用加法器,用于非流水线单周期乘法/累积(MAC)操作 比较,选择和存储单元(CSSU)以进行维特比算子的添加/比较选择 指数编码器以计算40的指数值单周期位累加器值 具有8个辅助寄存器和2个辅...

SM320C6711D-EP 增强型产品浮点 D...

320C67x ?? DSP(包括SM320C6711-EP,SM320C6711B-EP,SM320C6711C-EP,SM320C6711D-EP器件)撰写TMS320C6000中的浮点DSP系列?? DSP平台。 C6711,C6711B,C6711C和C6711D器件基于德州仪器(TI)开发的高性能,先进的超长指令字(VLIW)架构,使这些DSP成为多通道和多功能应用的绝佳选择。 C6711 /C6711B器件的时钟频率为150 MHz,性能高达每秒9亿次浮点运算(MFLOPS),可为高性能DSP编程挑战提供经济高效的解决方案。 C6711 /C6711B DSP具有高速控制器的操作灵活性和阵列处理器的数字能力。该处理器具有32个32位字长的通用寄存器和8个高度独立的功能单元。八个功能单元提供四个浮点/定点ALU,两个定点ALU和两个浮点/定点乘法器。 C6711 /C6711B每个周期可以产生两个MAC,总计300 MMACS。 在200 MHz或1350 MFLOPS的时钟频率下,每秒浮点运算高达12亿次(MFLOPS) C6711C /C6711D器件的时钟频率为250 MHz(适用于6711D),还为高性能DSP编程挑战提供了经济高效的解决方案。 C6711C /C6711D DSP还具有高速...

TMS320C6712D 浮点数字信号处理器

TMS320C67x ?? DSP(包括TMS320C6712,TMS320C6712C,TMS320C6712D器件)是浮点DSP系列的成员TMS320C6000。 DSP平台。 C6712,C6712C和C6712D器件基于德州仪器(TI)开发的高性能,先进的超长指令字(VLIW)架构,使这些DSP成为多通道和多功能应用的绝佳选择。 p> C6712D器件在时钟频率为150 MHz时性能高达9亿次浮点运算(MFLOPS),是C6000中成本最低的DSP? DSP平台。 C6712D DSP具有高速控制器的操作灵活性和阵列处理器的数字能力。该处理器具有32个32位字长的通用寄存器和8个高度独立的功能单元。八个功能单元提供四个浮点/定点ALU,两个定点ALU和两个浮点/定点乘法器。 C6712D每个周期可以产生两个MAC,总共300 MMACS。 C6712D采用基于缓存的两级架构,具有强大而多样的外设集。 1级程序高速缓存(L1P)是32-Kbit直接映射高速缓存,1级数据高速缓存(L1D)是32-Kbit 2路组关联高速缓存。 2级内存/高速缓存(L2)由512-Kbit的内存空间组成,在程序和数据空间之间共享。 L2内存可以配置为映射内存,缓存或两者的组合。外设集包括两...

TMS320VC5441 数字信号处理器

TMS320VC5441定点数字信号处理器是一款运行速率为532-MIPS的四核解决方案。 5441由四个带有共享程序存储器的DSP子系统组成。每个子系统由一个TMS320C54x组成? DSP内核,32K字程序/数据DARAM,64K字数据DARAM,三个多通道缓冲串行端口,DMA逻辑,一个看门狗定时器,一个通用定时器和其他各种电路。 5441还包含一个主机端口接口(HPI),允许5441被视为主机处理器的内存映射外设。 每个子系统都有独立的程序和数据空间,允许同时访问程序说明和数据。可以在一个周期中执行两个读操作和一个写操作。具有并行存储和特定于应用程序的指令的指令可以充分利用该架构。此外,数据可以在程序和数据空间之间传输。这种并行性支持一组强大的算术,逻辑和位操作操作,这些操作都可以在一个机器周期中执行。 5441包括管理中断,重复操作和函数调用的控制机制。此外,5441共有256K字的共享程序存储器(子系统A和B共享128K字,另外128K字由子系统C和D共享)。 5441用作高性能,低成本,高密度DSP,用于远程数据访问或IP语音子系统。它旨在维护当前的调制解调器架构,同时最大限度地减少...

评论