完善资料让更多小伙伴认识你,还能领取20积分哦,立即完善>

电子发烧友网技术文库为您提供最新技术文章,最实用的电子技术文章,是您了解电子技术动态的最佳平台。

芯片开发成本的估算非常复杂,因为这些数字受到多种因素影响。早在2018年,IBS发布的数据将5纳米芯片的成本定为5.422亿美元,这样的估算可能不再准确,因为芯片设计和制造的方式已经发生了巨大变化。...

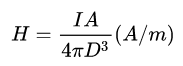

由于导线本身存在的电阻,相邻导线之间的互感,耦合电容在芯片内部会产生信号噪声,串扰和反射。这些效应会产生信号完整性问题,导致信号电压波动和变化,如果严重就会导致信号失真错误。...

在这五年中,通过与数以百计的芯片公司客户以及厂商的探讨交流、实践与协作,摩尔精英IT/CAD业务不断升级迭代,突破了之前一个封闭的芯片公司内部IT管理视角的局限性,而是能从行业发展的视角来看待IT/CAD这个支持性职能的发展路径。...

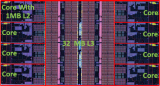

AMD 在代号 Milan-X 的 EPYC 7003X 系列处理器上应用了第一代 3D V-Cache 技术。这些处理器采用 Zen 3 架构核心,每片 Cache(L3 Cache Die,简称 L3D)为 64MB 容量,面积约 41mm²,采用 7nm 工艺制造...

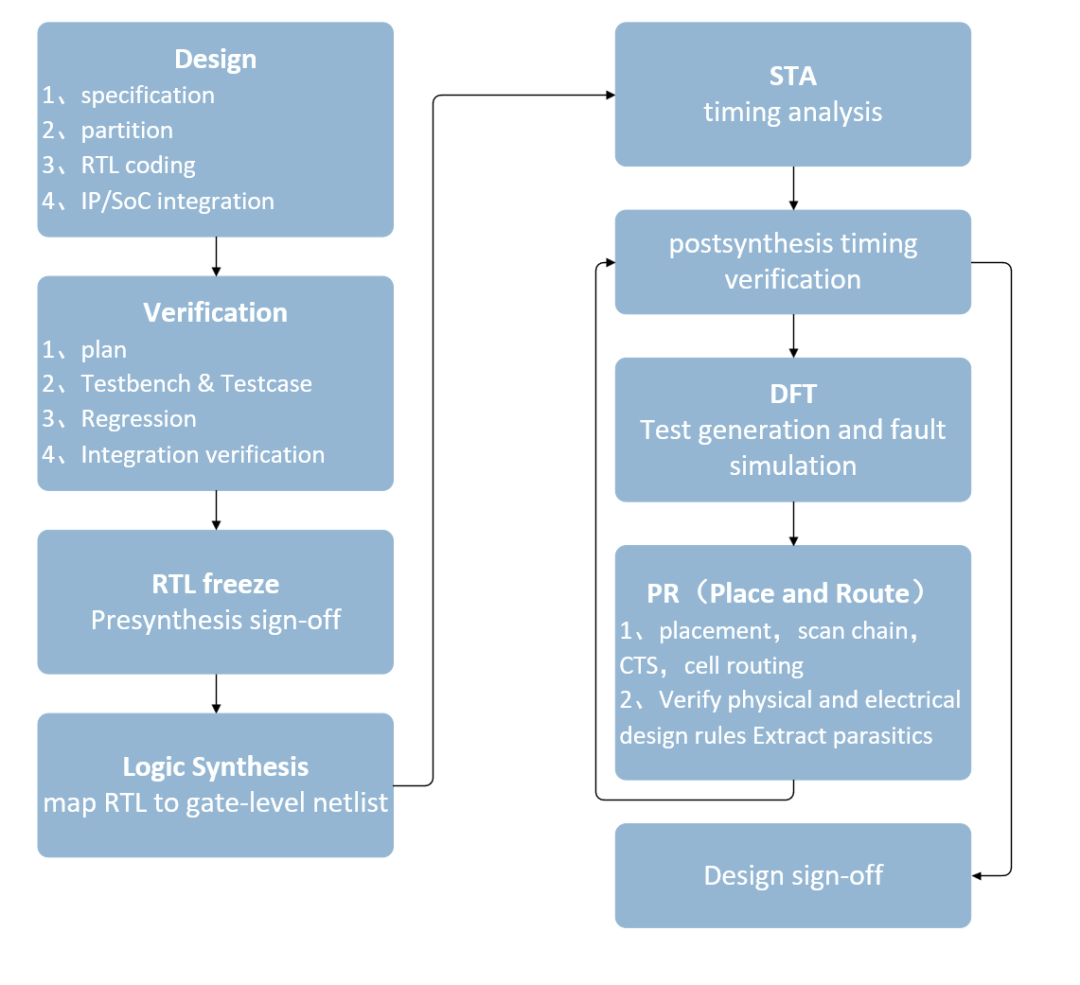

时序分析和验证时出现的错误可能需要反复重做前面几步才能解决,是一个多次迭代优化的过程。 下面我来仔细介绍一下这六个步骤。...

当CK为0时,ECK 恒定为0, q值为E:如果E为1,则q为1,如果E为0,则q为0。 当CK为1时,ECK 恒定为q(n),即对应的上一次CK为0时,锁存的E值。 因此最终的效果就是,只要E配置成了0,那么ECK会在CK的下降沿跳变成0,随后只要E保持为0,那么ECK一直为0。...

晶圆厂每年都会有固定的几次MPW机会,叫Shuttle (班车),到点即发车,是不是非常形象不同公司拼Wafer,得有个规则,MPW按SEAT来锁定面积,一个SEAT一般是3mm*4mm的一块区域,一般晶圆厂为了保障不同芯片公司均能参与MPW,对每家公司预定的SEAT数目会限制(其实SEAT多成本就...

华为麒麟9905G的芯片面积约113平方毫米,片12英寸硅片上大约可生产600颗芯片。每颗芯片上大约集成了103亿只晶体管。...

Scan stitching 是把上一步中得到的Scan DFF的Q和SI连接在一起形成scan chain。在芯片的顶层有全局的SE信号,以及scan chain的输入输出信号:SI 和 SO。通过scan chain的连续动作,就可以把问题从对复杂时序电路的测试转化成测试组合电路。...

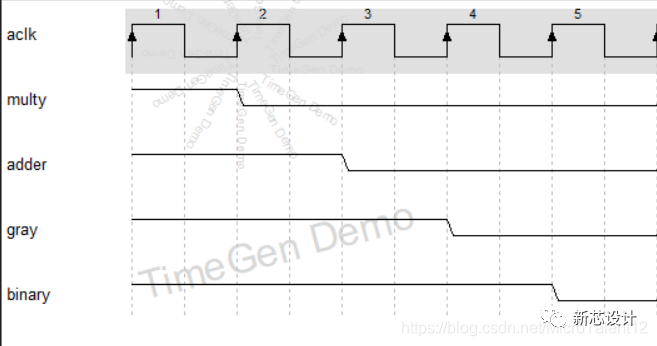

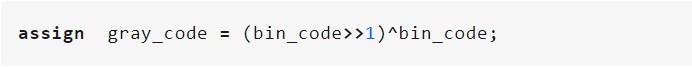

这是一个能够成功上板实现的灰度转二值的 Verilog 程序设计,详细的数据延时与信号延时如下所示...

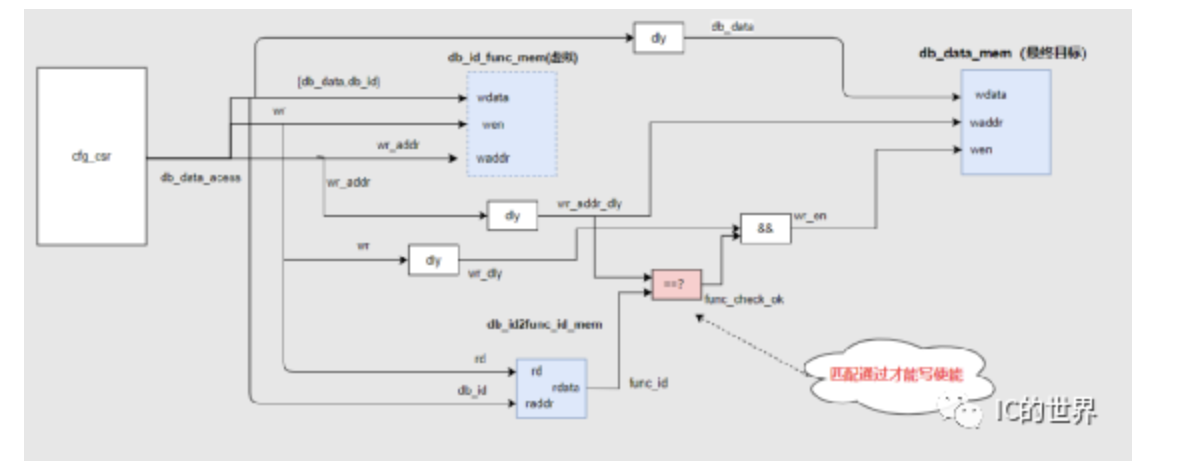

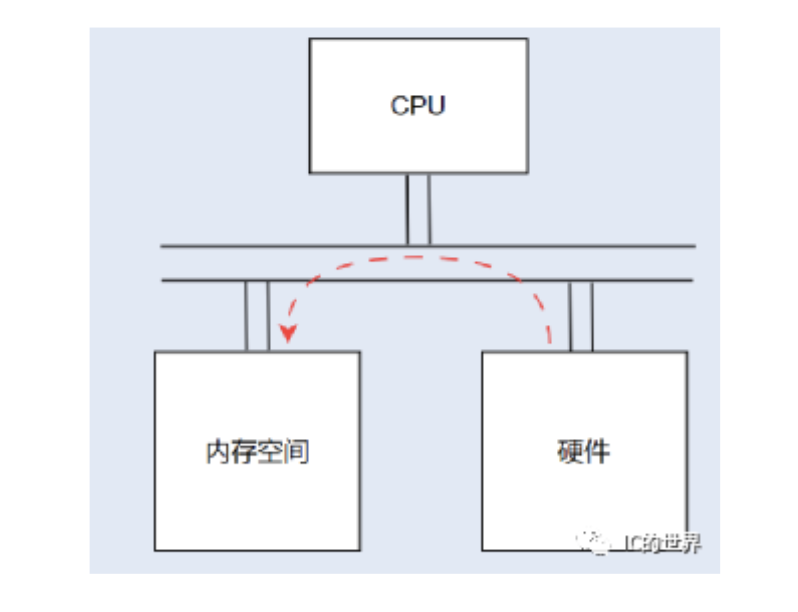

在软件硬件交互的过程中,通常需要软件(host)对特定地址的寄存器进行写操作,告之硬件进行特定的处理流程。...

EDA有着“芯片之母”称号,一个完整的集成电路设计和制造流程主要包括工艺平台开发、集成电路设计和集成电路制造三个阶段,三个设计与制造的主要阶段均需要对应的EDA工具作为支撑。...

渐进式改进与性能的巨大飞跃相结合,虽然这些改进将计算和分析能力提升到全新水平,但也需要全新的权衡考虑。这些变革的核心在于高度定制的芯片架构,芯片是在最先进的工艺节点开发的。...

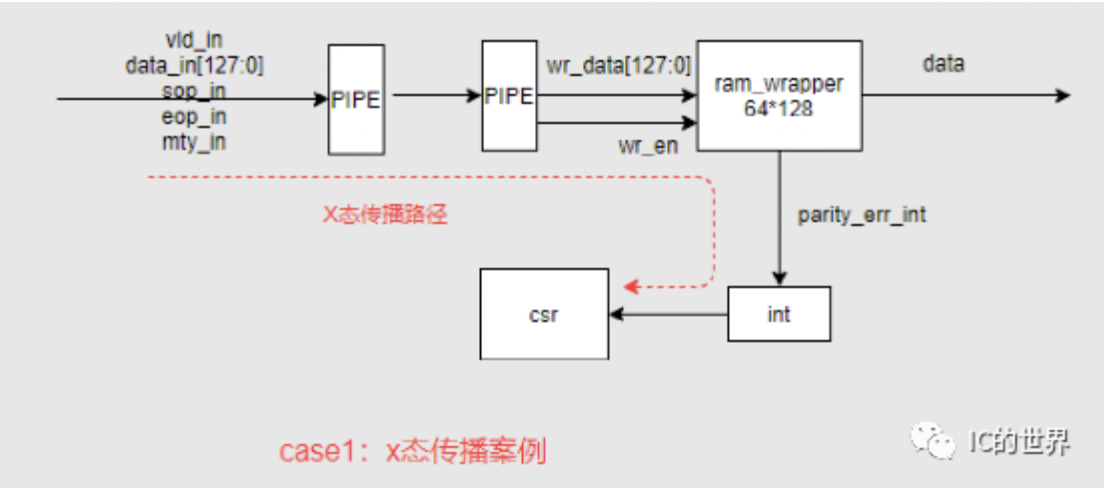

在芯片设计中,常常有这样的应用场景。硬件给软件传递消息,软件通过polling的方式获取。在我们的案例中,我们约定,硬件每次都上送128bit的数据。...

虽然真实芯片中,寄存器初始状态值只会为1或者为0。但是在RTL级仿真过程中X态的传播经常会给咱们造成很多麻烦,例如部分信号期望为0,但是仿真结果显示为X态。...

在大规模ASIC设计中,**多时钟系统**通常是不可避免的,这会导致不同时钟域中的数据传输问题。...

芯片设计分为前端设计和后端设计,前端设计也称为逻辑设计,后端设计也称为物理设计。随着DFT技术的发展,有的公司将DFT归到前端设计,有的公司归到后端设计,有些情况下也将DFT归到中端设计。前后端并没有统一严格的界限,笔者愚见,个人认为涉及到工艺相关的设计就是后端设计。...

在芯片设计中,复位操作被广泛应用,以确保芯片能够快速、准确地从故障状态恢复到正常工作状态。...