脉冲压缩技术是指对雷达发射的宽脉冲信号进行调制(如线性调频、非线性调频、相位编码),并在接收端对回波宽脉冲信号进行脉冲压缩处理后得到窄脉冲的实现过程。脉冲压缩有效地解

2011-09-30 15:09:56 1068

1068

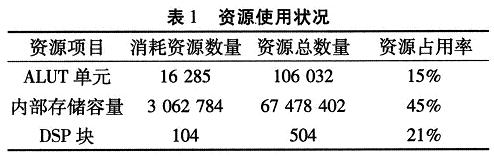

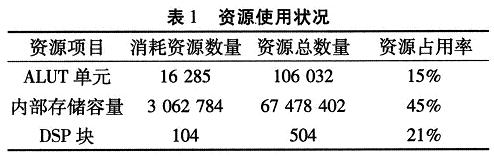

为了研究数字化γ能谱仪,本文提出一种基于FPGA的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。用QuartusⅡ软件在FPGA平台上完成了数字核脉冲的幅度提取并生成能谱。

2013-11-21 10:57:26 1948

1948

基于FPGA 的数字核脉冲分析器硬件设计方案,该方案采用现场可编程逻辑部件(FPGA),完成数字多道脉冲幅度分析仪的硬件设计。

2015-02-03 09:55:05 1870

1870

ADS5500 - 12-Bit, 105MSPS Analog-toDigital Converter - Burr-Brown Corporation

2022-11-04 17:22:44

14-Bit, 125MSPS Analog-to-Digital Converter datasheet (Rev. F)

2022-11-04 17:22:44

ADS5500-EP datasheet (Rev. C)

2022-11-04 17:22:44

EVALUATION MODULE FOR ADS5500

2023-03-30 11:47:22

ADS54T04IZAYR原厂现货TI 1000个ADS58H40IZCRR原厂现货TI 10000个ADS58H43IZCR原厂现货TI 8985个ADS5500MPAPREP原厂现货TI 1000个

2021-10-26 10:03:05

我们通过差分运放给ADC(ADS5500)输入了一个0~20mV的三角波信号,然后用逻辑分析仪输出的数据,发现在峰值部分有一个上抬,分析后发现是由于D7的错误输出导致,如果将输入信号加大,D8位也

2019-05-28 13:02:58

概述:采用64引脚TQFP PowerPAD封装,100MHz时ADS5500的信噪比(SNR)为70dB,无失真动态范围(SFDR)为82dB。它广泛应用于通讯基站基础设备、视频和影像系统、通讯

2021-05-18 07:40:52

【作者】:陈世海;裴东兴;张琦;【来源】:《电子设计工程》2010年02期【摘要】:针对数据采集系统高速长时间的采样和后端数据传输及存储能力有限的问题,提出基于FPGA的数据压缩解决方案。同时为平滑

2010-04-24 09:05:21

分析了抖动偏频激光陀螺信号的解调原理,提出了一种利用数字信号处理技术并采用FPGA实现的抖动解调方法;通过对激光陀螺脉冲计数值高速采样并采用数字滤波器滤波处理,可以有效消除抖动引起的信号噪声,得到

2018-08-30 09:21:12

DSP技术广泛应用于各个领域,但传统的数字信号处理器由于以顺序方式工作使得数据处理速度较低,且在功能重构及应用目标的修改方面缺乏灵活性。而使用具有并行处理特性的FPGA实现数字信号处理系统,具有很强的实时性和灵活性,因此利用FPGA实现数字信号处理成为数字信号处理领域的一种新的趋势。

2019-10-17 08:12:27

方波脉冲、高斯脉冲、Hermite脉冲和正交椭球波函数等。随着声表面波器件(SAW)的发展,可由低成本、低功耗、低复杂度的声表面波滤波器利用脉冲压缩技术产生和检测线性调频信号(Chirp)。由于

2019-06-14 07:24:09

和医疗成像•医疗器械•数字曝光系统说明DLP5500数字微镜器件(DMD)是一种数字控制的MOEMS(微光机电系统)空间光调制器(SLM)。当耦合到适当的光学系统时,DLP5500可用于调制入射(照明

2020-09-11 17:13:36

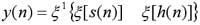

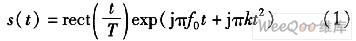

学习一下该开发板其他例程,提升一下自己,顺便也希望可以给他人提供些有用的参考例程。项目描述:1:完成线性调频信号LFM的数字下变频DDC(包括正交变换、FIR低通滤波及抽取);2:LFM信号的脉冲压缩

2015-09-10 11:18:53

小弟最近在做一个数字下变频和脉冲压缩的仿真,现在一点头绪都没有,有没有大神指教一下方向的。希望大神不吝赐教,或者是有源代码能分享一下,跪谢了。

2017-03-11 10:50:24

,数字锁相倍频模块每输出一个有效的采样触发信号CLK,ADC控制器就完成一次6通道的采样操作,然后停止等待下一个触发脉冲的到来。时钟管理模块的作用是利用最小系统板上的50MHz晶振输入,经过编程进行

2021-07-01 08:30:00

2 W5500的内部功能方框图2.3 系统程序设计本设计中FPGA选用Xilinx公司的Spartan6系列的XC6SLX150-2FG484C芯片。这款高性能核心板,具有高速,高带宽,高容量等特点

2018-08-07 10:10:25

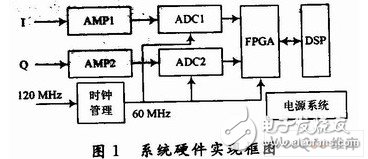

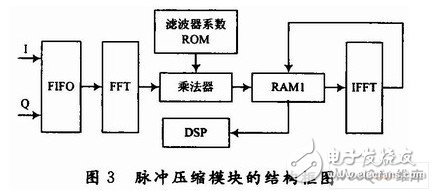

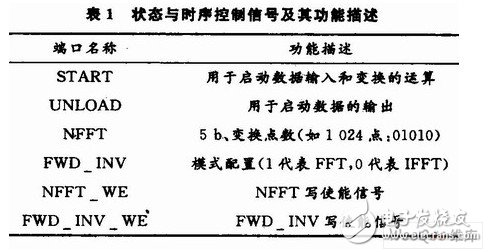

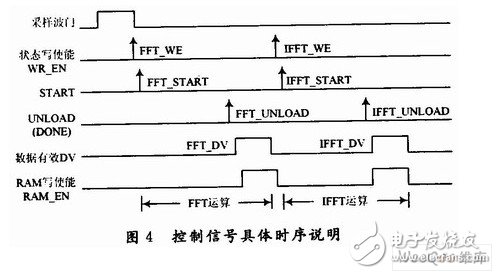

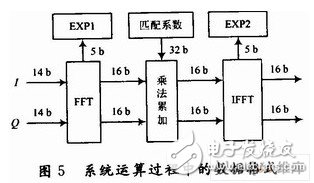

转换器选用TI公司的ADS5500,具有14 b的分辨率和125 MSPS的最高采样率,用来对输入LFM信号进行60 MHz的高速采样。 数字脉冲压缩模块在FPGA中实现,FPGA选用Xilinx

2018-11-09 15:53:22

基于FPGA的数字脉冲压缩技术1.数字脉冲压缩实现原理2.电路设计2.1APEX2OKE系列FPGA 简介2.2 基于FPGA 的算法研究及实现 2.3 脉冲压缩在FPGA 上的实现

2011-03-02 09:41:50

调相脉冲信号可以获得较大的压缩比,它作为一种常用的脉冲压缩信号,在现代雷达及通信系统中获得了广泛应用。随着近年来软件无线电技术和电子技术的发展,DDS(直接数字频率合成)用于实现信号产生的应用越来越广。

2019-09-30 07:22:22

基于FPGA的雷达脉冲压缩系统设计参见附件:

2011-03-02 09:39:11

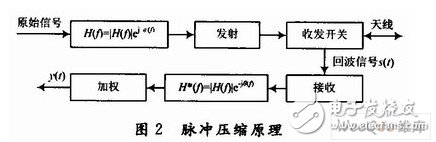

脉冲压缩技术是指对雷达发射的宽脉冲信号进行调制(如线性调频、非线性调频、相位编码),并在接收端对回波宽脉冲信号进行脉冲压缩处理后得到窄脉冲的实现过程。脉冲压缩有效地解决了雷达作用距离与距离分辨率之间的矛盾,可以在保证雷达在一定作用距离下提高距离分辨率。

2019-10-08 11:16:45

芯片具有高位、快速等特点,且操作简单。利用FPGA实现对数据的FFT转换,最终计算得出所测移动或静止物体与测量点间距离。 作为一个实时测距系统,单片机运算速度较慢,不能充分应用其优点,采用FPGA能满足

2021-12-27 17:08:50

王玲,邱军海,王世桥(烟台工程职业技术学院山东烟台264006)线性调频信号可以获得较大的压缩比,有着良好的距离分辨率和径向速度分辨率,所以线性调频信号作为雷达系统中一种常用的脉冲压缩信号,已经

2019-07-08 07:38:45

基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

2019-09-26 07:06:35

视频过大,打包成8个压缩包基于FPGA设计的数字时钟.part01.rar (20 MB )基于FPGA设计的数字时钟.part02.rar (20 MB )基于FPGA设计的数字时钟

2019-05-14 06:35:34

脉冲压缩是近年来光子晶体光纤中一个新的应用领域,在光通信系统中,利用具有高非线性系数和较大负色散值的光子晶体光纤进行脉冲压缩,将降低传输时间,提高传输速率。本文从非线性薛定谔方程组入手,深入探讨

2010-05-28 13:38:25

间提供简单、灵活的通信接口。 通常情况下,图像采集系统以CCD或CMOS等数字式相机为基础,还需要采集卡来完成数据采集,常见的采集卡有基于DSP实现的和基于FPGA实现的,MV-D1024E系列相机

2019-07-02 08:11:34

傅里叶变换、脉冲压缩、线性预测编码语音处理、高速定点矩阵乘法等,有较好的应用前景和发展空间。那有谁知道该如何利用FPGA实现级联信号处理器吗?

2019-07-30 07:22:48

针对航天测试系统的应用需求,利用FPGA的设计微型数字存储系统势在必行,那我们具体该怎么做呢?

2019-08-01 08:14:33

脉冲压缩体制在现代雷达中被广泛采用,通过发射宽脉冲来提高发射的平均功率,保证足够的作用距离;接收时则采用相应的脉冲压缩算法获得脉宽较窄的脉冲,以提高距离分辨力,从而能够很好地解决作用距离和距离分辨力之间的矛盾问题。

2019-11-08 08:08:55

本文提出一种采用FPGA和CMOS数字传感器实现前端数据采集、利用单片机进行图像鉴别和压缩、通过以太网控制器实现图像数据传输的图像监测系统。该系统不仅实现了图像信号数据采集,而且数据传输速度和稳定性高;不仅灵活性好、成本低,而且具有网络化、智能化等优点。

2021-05-26 06:58:29

怎么利用FPGA实现数字电压表的设计?

2021-05-06 10:19:03

脉冲压缩体制在现代雷达中被广泛采用,通过发射宽脉冲来提高发射的平均功率,保证足够的作用距离;接收时则采用相应的脉冲压缩算法获得脉宽较窄的脉冲,以提高距离分辨力,从而能够很好地解决作用距离和距离分辨力

2019-08-26 07:10:09

如何有效解决雷达作用距离与距离分辨率之间的矛盾?基于FPGA的雷达脉冲压缩系统设计

2021-04-08 06:02:27

脉冲压缩网络,给出了关键参数的设计计算,并且介绍了新颖的末级磁脉冲压缩放电结构。实验结果显示:各级磁脉冲压缩效果达到设计指标,电源输出电压峰达30 kV,输出电流峰值大于40 kA,电流脉冲宽度200

2010-04-22 11:41:29

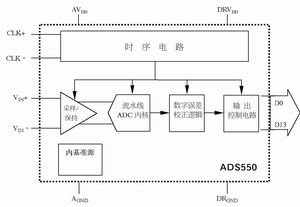

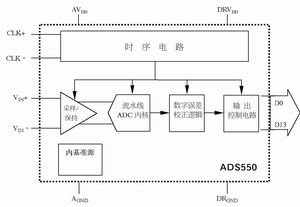

ADS5500的内部结构框图和工作信号时序ADS5500设计需要考虑什么因素?ADS5500的应用

2021-04-21 06:47:20

综合考虑到图像采集系统所要求的实时性,可靠性,以及FPGA在数字电路的设计中的优势,为此本文讨论如何利用FPGA设计基于LVDS的图像数据采集传输系统?

2021-04-08 06:48:28

脉冲压缩系统工业原理是什么?LFM信号实时脉冲压缩是如何实现的?TMS320C64x处理器的特点有哪些?

2021-04-19 11:50:02

【作者】:张鹏;和天慧;沈旭明;【来源】:《信息与电子工程》2010年01期【摘要】:为了实现高功率微波初级波源的小型化,获得更高功率的输出微波脉冲,研制了用于高功率微波脉冲压缩的能量倍增器。利用

2010-04-22 11:48:46

14位125Msps模数转换器ADS5500及其应用。摘要:ADS5500是美国德州仪器公司(TI)生产的一款高采样率、高精度、易使用的14位模数转换器。简易的并行数字输出数据接口可方便地与数字信号处理器(DSPs)连接。

2009-09-30 20:27:43 7

7 ADS5500是德克萨斯仪器公司(Texas Instruments)开发的一款14位分辨率、125MSPS采样速率的高性能模数转换器,芯片为64引脚TQFP PowerPAD封装。为实现更高的系统集成度,其内部还包括有宽

2009-09-30 20:28:45 66

66 传统的匹配滤波只能将距离旁瓣压缩到一定的程度,因此可能出现强目标的旁瓣掩盖弱目标的情况。针对上述问题,该文提出了基于迭代思想和最大输出信噪比准则的自适应脉冲压

2009-11-20 16:01:33 10

10 本文设计了一种以 FPGA 为数据压缩和数据缓存单元的高速数据采集系统,其主要特点是对高速采集的数据进行实时压缩,再将压缩后的数据进行缓冲存储。该设计利用数据比较模

2009-11-30 15:32:36 20

20 BOA单棱镜飞秒超短脉冲压缩器 当超短脉冲激光透过材料传输时(即使是简单的玻璃),由于群延迟色散(GDD)它们会在时间上展宽。红光的传播速度比蓝光的传播速度

2023-05-24 11:04:06

脉冲压缩透射光栅高功率光束组合光谱衍射光栅 脉冲压缩透射光栅高功率光束组合光谱衍射光栅采用独特的图案化方法、DUV投影光刻和离子蚀刻,为透射衍射光栅提供了许多

2023-05-24 13:50:09

Lightsmyth光通信1550nm脉冲压缩透射衍射光栅 Lightsmyth光通信1550nm脉冲压缩透射衍射光栅用于将入射光成角度地分散到光谱中。光通信透射衍射光栅

2023-05-24 13:55:56

发射信号的分离是MIMO 雷达的一个重要环节,该文基于最小均方误差准则,提出了一种有效的MIMO雷达自适应脉冲压缩方法,从每个接收阵元接收到的信号中分别自适应地估计每个距

2010-02-09 13:37:38 15

15 描述了Z箍缩放电等离子体极紫外光源系统中的主脉冲电源,给出了主电路拓扑结构,重点介绍了三级磁脉冲压缩网络,给出了关键参数的设计计算,并且介绍了新颖的末级磁脉冲

2010-03-05 14:13:38 27

27 针对受激布里渊散射(SBS)脉冲压缩系统中经常出现的波形调制现象,提出一种抑制调制、改善窄脉冲波形质量的新方法——双级SBS脉冲压缩结构。此方法以“两次压缩,子峰能量

2010-03-05 15:20:08 19

19 摘 要:基于电容微分结构设计脉冲产生电路。利用ADS软件对电路进行仿真和优化,脉冲宽度为1.5ns。对电路进行调试得到的结果与仿真结果基本一致。关键词:微分电路;脉

2010-04-13 22:26:38 42

42 The ADS5500 is a high-performance, 14-bit, 125 Msps analog-to-digital converter (ADC). To provide

2010-06-04 11:23:12 25

25 Processing™ solutions by coupling the CDC7005 low-jitter clock synchronizer chip with the industry leading 14-bit ADS5500 ADC dev

2010-06-04 11:38:04 17

17 本应用笔记介绍了当前视频监控系统所采用的不同压缩技术以及一些视频压缩标准的优势,讨论了利用传统CCTV和IP摄像机输入实现数字录像的基本原理,即采用H.264视频压缩标准能够

2010-07-30 11:27:59 20

20

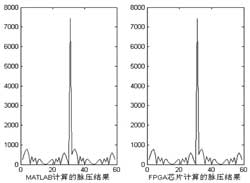

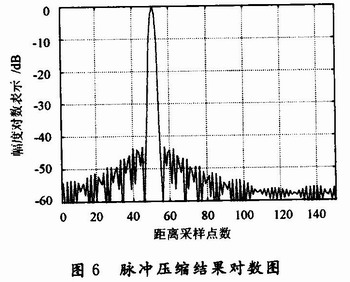

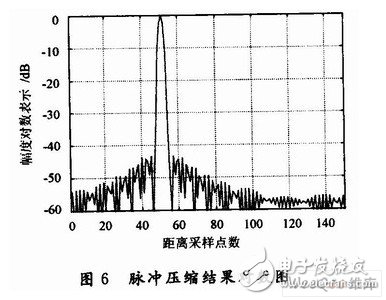

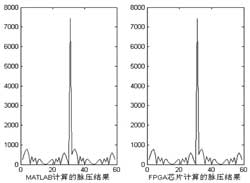

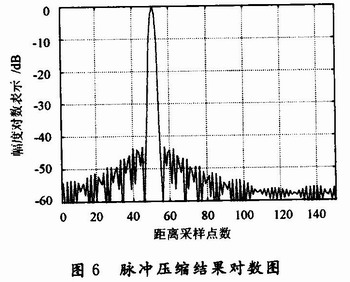

为解决雷达探测能力与距离分辨力之间的问题,在线性调频信号脉冲压缩的原理的基础上,利用MATLAB软件对数字脉冲压缩算法进行仿真,给出一种基于FPGA分布式算法的

2010-12-24 16:10:59 37

37 摘 要:本文介绍了ADS5500的性能特点和设计考虑,并对其在视频信号处理方面的应用作了简要说明。

2006-03-11 13:18:27 1034

1034

FPGA的多路可控脉冲延迟系统设计

采用数字方法和模拟方法设计了一种最大分辨率为0.15 ns级的多路脉冲延迟系统,可以实现对连续脉冲信号的高分辨

2009-03-29 15:09:48 2234

2234

基于FPGA雷达成像方位脉冲压缩系统的设计

合成孔径雷达成像算法中较为成熟和应用广泛的算法主要有距离-多普勒(R-D)算法和线性调频变标(CS)算法。R-D算法复杂度相

2009-12-02 11:44:10 1168

1168

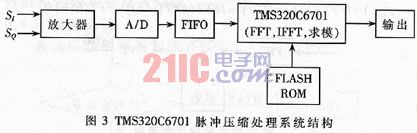

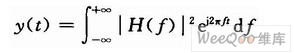

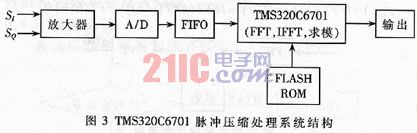

本文以TI公司的高性能的TMS320C6701浮点DSP芯片作为实现数字脉冲压缩的核心器件,实现了线性调频信号的频域数字脉冲压缩。

1 数字脉冲压缩原理

数

2010-07-02 09:47:37 2878

2878

脉冲压缩技术是指对雷达发射的宽脉冲信号进行调制(如线性调频、非线性调频、相位编码),并在接收端对回波宽脉冲信号进行脉冲压缩处理后得到窄脉冲的实现过程。脉冲压缩有效

2010-07-19 09:37:01 1064

1064

O 引言

脉冲压缩体制在现代雷达中被广泛采用,通过发射宽脉冲来提高发射的平均功率,保证足够的

2010-10-08 11:33:44 2184

2184

本文主要介绍了一种利用FPGA IP核设计线性调频信号脉冲压缩的方法,通过各种仿真与实际测试表明脉冲压缩结果正确。这种基于IP核的模块化设计方法非常灵活,参数的设置和修改方便

2011-06-29 10:40:20 7309

7309

本设计开发出了一套基于双FPGA+ARM架构的高速计算机屏幕图像压缩系统。系统通过对图像压缩系统任务的划分,利用FPGA的并行计算能力和灵活的编程方式,完成图像压缩算法。

2011-08-22 11:44:31 2039

2039

针对一种新型的宽脉冲信号二相码码内线性调频信号,分析了其数学表达式及其回波形成原理,并介绍了一种二相码码内线性调频信号地杂波模拟器的系统实现。

2011-09-07 18:58:11 46

46 基于FPGA的静止图像压缩系统的研究-JPEG编码器的设计电力电子与电力传动数字图像在人们生活中的应用越来越广泛,由于原始图像数据量比较大,因此数字图非常重要。

2011-11-01 18:17:55 65

65 本文基于快速傅里叶IP核可复用和重配置的特点,实现一种频域的FPGA数字脉压处理器,能够完成正交输入的可变点LFM信号脉冲压缩,具有设计灵活,调试方便,可扩展性强的特点。

2012-10-15 17:20:46 2738

2738

基于FPGA和MVD1024E相机的图像采集系统

2016-09-22 12:27:27 19

19 中频脉冲压缩信号数字化直接产生技术研究

2017-01-10 21:35:22 17

17 噪声干扰对线性调频脉冲压缩滤波器的干扰效果分析

2017-01-10 21:35:20 6

6 用高速DSP在频域上实现LFM信号的实时脉冲压缩

2017-01-10 21:35:20 6

6 一类新的脉冲压缩信号的旁瓣抑制,下来看看。

2017-01-10 21:35:20 11

11 压缩比1201的线性调频脉冲压缩系统,下来看看

2017-01-10 21:35:20 11

11 脉冲压缩在超宽带雷达中的应用,可以下来看看

2017-01-22 21:15:50 11

11 基于FPGA的1024点高性能FFT处理器的设计_钟冠文

2017-03-19 11:36:55 10

10 1024 2007脉冲功率表

2017-10-16 10:55:27 0

0 针对网内采用了旁瓣匿影和旁瓣对消技术的脉冲压缩雷达,采用卷积噪声对该种雷达进行干扰。结合公式推导及仿真实验,验证了该噪声的假目标特性。同时得出了该噪声在雷达接收机处所能获得的匹配增益计算公式,在信号

2017-11-07 09:46:41 0

0 TI公司引进了一套适合于高速、高中频采样ADC设备的设备,如ADS5500 ADC,能够在125MSPS下进行采样。为了实现这些高性能器件的全部潜力,必须提供一种极低的相位噪声时钟源。CDC7005

2018-05-18 11:07:29 4

4 脉冲压缩技术是指对雷达发射的宽脉冲信号进行调制(如线性调频、非线性调频、相位编码),并在接收端对回波宽脉冲信号进行脉冲压缩处理后得到窄脉冲的实现过程。脉冲压缩有效地解决了雷达作用距离与距离分辨率之间的矛盾,可以在保证雷达在一定作用距离下提高距离分辨率。

2018-11-28 09:18:00 3561

3561

、功耗与实时性要求都很高的实时SAR成像系统,其应用十分广泛。在整个有距离-多普勒(R-D)算法中方位脉冲压缩系统是设计的关键。随着FPGA芯片突飞猛进的发展,实时雷达成像方位脉冲压缩系统在FPGA上实现变成了可能。

2018-12-30 11:10:00 3331

3331

电子发烧友网为你提供TI(ti)ADS5500-EP相关产品参数、数据手册,更有ADS5500-EP的引脚图、接线图、封装手册、中文资料、英文资料,ADS5500-EP真值表,ADS5500-EP管脚等资料,希望可以帮助到广大的电子工程师们。

2018-11-02 19:09:06

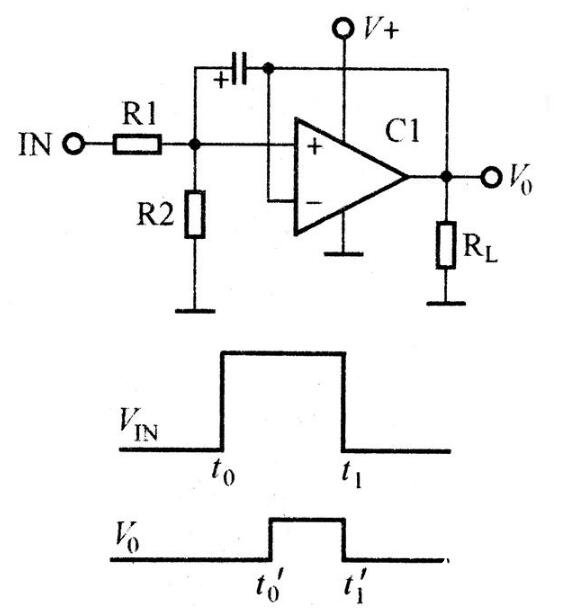

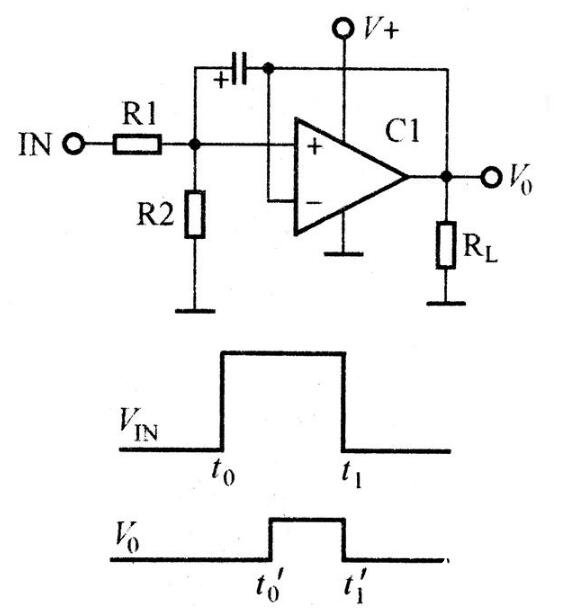

同时,由于C1与R1对信号的积分延时,所以,输出脉冲与输入脉冲相比,幅度和宽度都被压缩了。

2020-05-02 17:00:00 2067

2067

片多通道高速串行ADC用于X射线脉冲信号的采集,利用数字电位计及高压电源模块实现探测器偏置电压的精细调节,利用数据存储校正电路等完成采集数据的校正处理,并可通过图像传输电路完成图像数据的传输与显示以及系统功能的调试。与上位

2021-06-01 09:37:44 13

13 近日,中科院上海光机所成功制备出超大口径(1620mmx1070mm)的无拼缝脉冲压缩光栅,该口径面积是目前国际已知最大同类光栅元件2.9倍。

2023-11-20 10:08:57 311

311

相位编码信号的相位调制函数是离散的有限状态,属于“离散型“编码脉冲压缩信号。

在相位编码中,二相编码信号是常用的脉压信号形式之一。

将宽脉冲分为许多短的等宽度子脉冲,每个子脉冲以两种相位调制,其调制的顺序由指定的编码序列决定。

2024-02-20 10:57:30 353

353

电子发烧友App

电子发烧友App

评论