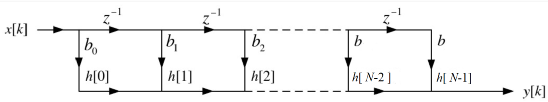

FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。##全并行FIR滤波器结构

2014-06-27 10:02:56 8178

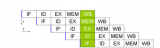

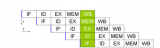

8178 流水线是为了提高效率,能并发同时进行多个任务。

2023-09-05 15:39:56 1112

1112

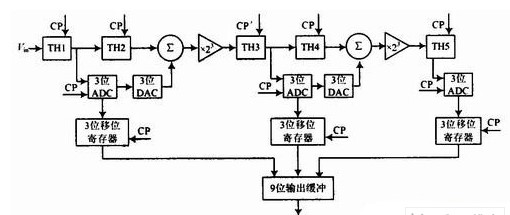

低采样速率ADC仍然采用逐次逼近(SAR)、积分型结构以及最近推出的过采样ΣΔADC,而高采样速率(几百MSPS以上)大多用闪速ADC及其各种变型电路。然而,最近几年各种各样的流水线ADC已经在速度

2023-09-26 10:24:32 434

434

本篇博文描述的是通过将 URAM 矩阵配置为使用流水线寄存器来实现最佳时序性能的方法

2019-07-26 16:01:44 5883

5883

时不同频率分量的叠加的相位情况和输入时有变化,得到的通带信号产生失真。iir滤波器有以下几个特点:1 iir数字滤波器的系统函数可以写成封闭函数的形式。2 iir数字滤波器采用递归型结构,即结构上带有反馈环路

2018-03-12 13:21:07

的线性相位滤波器IIR滤波器有以下几个特点:1、IIR数字滤波器的系统函数可以写成封闭函数的形式。2、IIR数字滤波器采用递归型结构,即结构上带有反馈环路。IIR滤波器运算结构通常由延时、乘以系数

2016-08-08 08:49:32

的性能要去较高。图1 FIR滤波原理图 IIR滤波器定义:IIR滤波器是无限脉冲响应滤波器,又称递归型滤波器,即结构上带有反馈环路。特点:IIR数字滤波器的系统函数可以写成封闭函数的形式,具有反馈回路

2019-06-27 04:20:31

;FIR 滤波器的系统函数为多项式;FIR 滤波器具有线性相位。实现同样参数的滤波器,FIR比IIR需要的阶数高,因此计算量大。目前,FIR 数字滤波器的设计方法主要是建立在对理想滤波器频率特性做某种近似的基础上。设计方法有窗函数法,等波纹设计法(Equiripple)和最小二乘法 (Least

2021-08-17 06:19:17

对于fir滤波器,已经在前面的文章中记录了仿制DIY&关于MATLAB中滤波器设计工具的使用心得记录),其设计和实现都非常简单。如果在嵌入式系统中可以满足且有必要实时iir运算,那么

2021-12-22 08:29:40

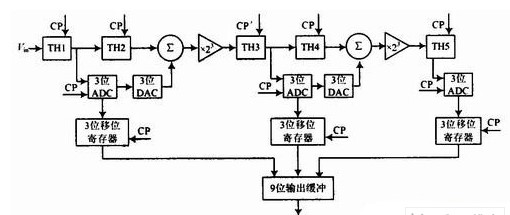

实现FPGA数字下变频的多类滤波器分组级联技术分析1 引 言 本文针对以下高效算法做了总结,进行合理的分组级联并引入流水线技术以便于在FPGA上实现。数字下变频(DDC)就是通过混频、抽取和滤波等

2009-10-23 10:26:53

型结构FIR,实现时可以采用并行结构、串行结构、分布式结构,也可以直接使用Quartus和Vivado提供的FIR IP核。本篇先介绍并行FIR滤波器的Verilog设计。设计参考自杜勇老师

2020-09-25 17:44:38

本文介绍了流水线ADC的内部结构和工作原理。

2021-04-22 06:56:00

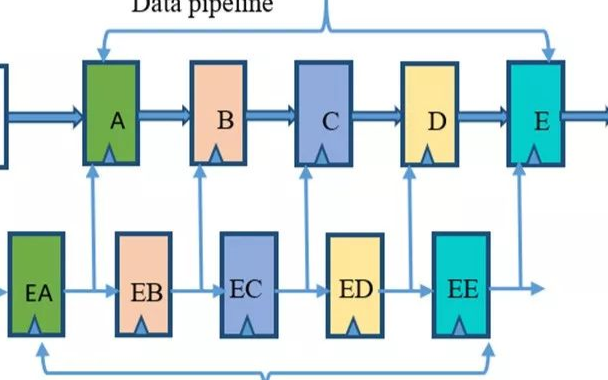

图中的DFG(Data Flow Graph)节点已经标出了传输延迟,求该电路中流水线寄存器的最佳放置位置?求问大神解答这个题

2021-11-20 11:02:57

流水线技术基本原理是什么?设计DSP流水线应注意哪些问题?

2021-04-28 06:10:03

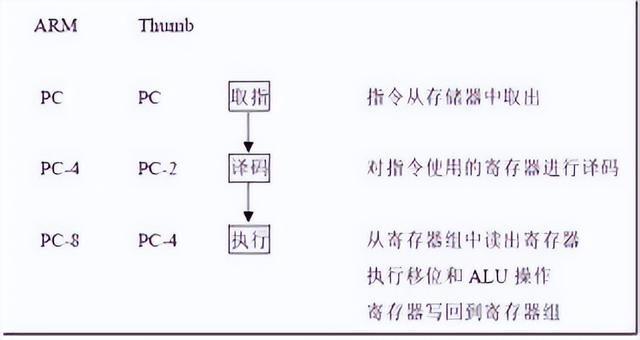

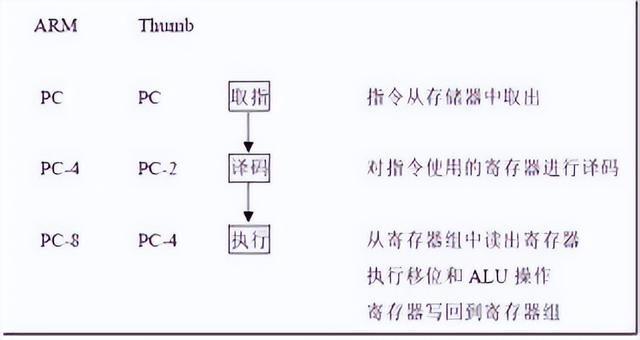

什么是ARM流水线流水线(Pipelining)是 RISC(精简指令集)处理器用来执行指令的机制,通过获取指令来加速执行,而其他指令同时被解码和执行。这反过来又允许内存系统和处理器连续工作。每个

2022-04-11 17:23:19

设计的算法,如第一条中表述的流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器,并暂存中间数据的方法。针对处理器中的流水线结构。比如,比如 5—6 个不同功能的电路单元组成一条指令处理

2020-10-26 14:38:12

形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。所谓串行结构,即串行实现滤波器的累加运算,将每级延时

2017-08-02 17:35:24

QY-JDYT25数控模组化生产流水线综合系统有什么作用?QY-JDYT25数控模组化生产流水线综合系统是由哪些部分组成的?QY-JDYT25数控模组化生产流水线综合系统有哪些特点?

2021-07-09 08:41:58

第37章FIR滤波器的实现 本章节讲解FIR滤波器的低通,高通,带通和带阻滤波器的实现。 37.1 FIR滤波器介绍 37.2 Matlab工具箱生成C头文件 37.3 FIR低通滤波器

2015-07-11 10:58:15

滤波器,即有限脉冲响应滤波器,顾名思义,是指单位脉冲响应的长度是有限的滤波器。而根据FIR滤波器的结构形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式

2017-04-14 15:20:31

如何理解fpga流水线

2015-08-15 11:43:23

前段时间发了个关于fpga的PID实现的帖子,有个人说“整个算法过程说直白点就是公式的硬件实现,用到了altera提供的IP核,整个的设计要注意的时钟的选取,流水线的应用”,本人水平有限,想请教一下其中时钟的选取和流水线的设计应该怎么去做,需要注意些什么,请大家指导一下。

2015-01-11 10:56:59

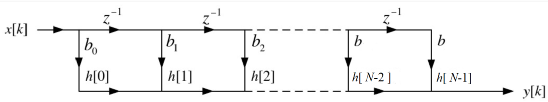

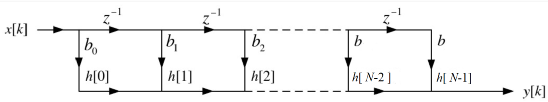

数,滤波器阶数为N-1。由上式可得到FIR滤波器在FPGA中的实现结构,如图1所示,主要由延迟单元Z-1、乘法器和累加器组成。此结构为直接型FIR滤波器结构,也称横向结构(transverse)。FIR结构

2021-12-15 06:30:00

本帖最后由 eehome 于 2013-1-5 09:50 编辑

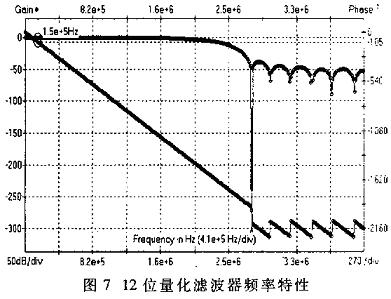

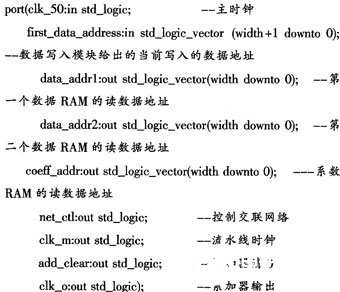

基于FPGA的FIR滤波器设计与实现 文章研究基于FPGA、采用分布式算法实现FIR滤波器的原理和方法,用

2012-08-11 15:32:34

系统兼具实时性和灵活性,而现有设计方案(如DSP)则难以同时达到这两方面要求。而使用具有并行处理特性的FPGA实现FIR滤波器,具有很强的实时性和灵活性,因此为数字信号处理提供一种很好的解决方案。

2019-11-04 08:08:24

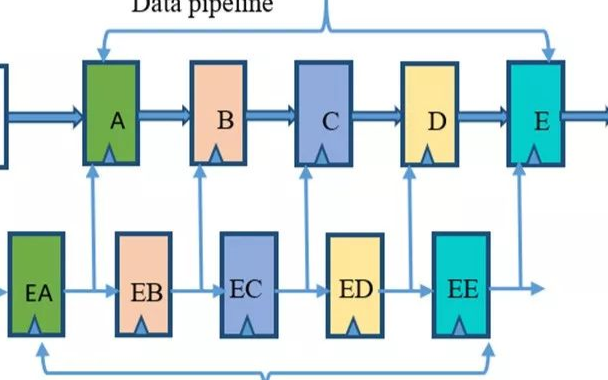

本文设计的FFT处理器,基于FPGA技术,由于采用移位寄存器流水线结构,实现了两路数据的同时输入,相比传统的级联结构,提高了蝶形运算单元的运算效率,减小了输出延时,降低了芯片资源的使用。

2021-04-28 06:32:30

本文首先介绍了FIR滤波器和脉动阵列的原理,然后设计了脉动阵列结构的FIR滤波器,画出电路的结构框图,并进行了时序分析,最后在FPGA上进行验证。结果表明,脉动阵列的模块化和高度流水线的结构使FIR

2021-04-20 07:23:59

流水线模数转换器(ADC)有哪些优点?流水线ADC中常用的运算放大器有哪些?流水线ADC的放大器结构及工作原理是什么?

2021-04-22 06:18:28

此示例显示如何设计低通FIR滤波器。这里介绍的许多概念可以扩展到其他响应,如高通,带通等。FIR滤波器被广泛使用,因为它们具有强大的设计算法,以非递归形式实现时的固有稳定性,可以轻松实现线性

2018-08-23 10:00:16

FIR滤波器的原理及结构是什么基于分布式算法的FIR滤波器的实现

2021-05-08 08:39:41

并行流水结构FIR的原理是什么基于并行流水线结构的可重配FIR滤波器的FPGA实现

2021-04-29 06:30:54

本文以实现抽取率为2的具有线性相位的3阶FIR抽取滤波器为例,介绍了一种用XC2V1000型FPGA实现FIR抽取滤波器的设计方法。

2021-05-07 06:02:47

滤波器获得了更广泛的应用。FIR滤波器有多种设计和实现方法,最为常用的是基于分布式算法的FIR滤波器设计。

2019-08-23 06:39:46

滤波器获得了更广泛的应用。FIR滤波器有多种设计和实现方法,最为常用的是基于分布式算法的FIR滤波器设计。

2019-08-27 07:16:54

本文将简单介绍另一种数字滤波器——IIR滤波器的原理,详细介绍使用Verilog HDL设计直接型IIR滤波器的方法。数字滤波器数字滤波器从实现结构上划分,有FIR和IIR两种。FIR的特点是:线性

2020-09-27 09:22:58

: 2.1 FIR数字滤波器与流水线结构 现代微处理器、数字信号处理器、高速数字系统设计中都广泛应用了流水线(Pipelining)技术,其核心设计思想是把一个周期内执行的逻辑操作分成几步较小的操作,在

2011-02-24 14:20:18

性能为目标。从此以后,流水线技术也被有效地应用到CISC处理器的设计中。Intel i486是IA32体系结构中的第一个流水线实现。Digital的VAX和Motorola的M68K的流水线版本在商业上也

2023-03-01 17:52:21

的作用;即DF(Digital Filter)是由差分方程描述的一类特殊的离散时间系统。它的功能是把输入序列通过一定的运算变换成输出序列。不同的运算处理方法决定了滤波器的实现结构的不同。35.1.2

2016-09-29 08:23:26

转dsp系列教程 本章节讲解FIR滤波器的低通,高通,带通和带阻滤波器的实现。 37.1 FIR滤波器介绍 37.2 Matlab工具箱生成C头文件 37.3 FIR低通滤波器设计 37.4 FIR

2016-09-29 08:32:34

。

FIR滤波器

一、定义:

FIR滤波器是有限长单位冲激响应滤波器,又称为非递归型滤波器,是数字信号处理系统中最基本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应

2023-05-29 16:47:16

与过去工厂管理模式相比,现代企业更注重品质与效率特别是服务制造业。目前在同行业里普遍推行的理念是智能工厂( Smartfactory),其解决方案主要以智能自动化流水线 电子看板系统 来实现。该系统

2019-10-05 20:03:08

在ARM中,关于 LDR流水线,分支流水线,中断流水线,其和 PC 之间的关系一直没整明白,求大神详解!!!

2019-04-30 07:45:25

FIR滤波器的原理及结构是什么基于分布式算法的FIR滤波器的实现

2021-04-30 06:03:00

根据FIR滤波器的结构形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。所谓串行结构,即串行实现

2017-05-23 10:11:26

这一节主要讲解一下转置型FIR滤波器实现。 FIR滤波器的单位冲激响应h(n)可以表示为如下式: 对应转置型结构的FIR滤波器,如图1所示,抽头系数与上一节中讲解直接型FIR滤波器的实例

2019-06-28 08:22:02

并网接口,容易产生谐振尖峰,影响整个系统的稳定性。鉴于此,本文提出了一种基于LCL型滤波器的光伏并网逆变器的设计方案,该方案对光伏并网逆变器的直接转矩控制策略进行了分析研究,通过仿真测试表明该逆变器

2018-09-29 16:39:11

提出了一种开关电容流水线结构A/D转换器(ADC)的速度分析方法。流水线结构ADC的速度取决于其级电路中开关电容反馈放大器的建立速度。根据流水线结构的特点,推导出输入等效阶

2008-12-03 13:02:29 30

30 针对并行爬虫系统在多任务并发执行时所遇到的模块间负载平衡问题,提出流水线负载平衡模型(PLB),将不同的任务抽象为独立模块而达到各模块的处理速度相等,采用多线程的方式

2009-03-31 10:19:30 19

19 流水线结构的高效SAR快视成像处理器

2009-05-08 17:16:47 23

23 并行FIR滤波器具有速度快、容易设计的特点,但是要占用大量的资源。在多阶数的亚高频系统设计中,使用并

2009-07-21 16:55:06 0

0 本文综合介绍了基于FPGA 软件Quartus II 和MATLAB 的FIR 滤波器的设计仿真,将两大软件综合运用后大大缩减了设计研发的时间,在算法结构上利用了流水线等优化方式。

2009-11-30 14:21:09 117

117 使用软件仿真硬件流水线是很耗时又复杂的工作,仿真过程中由于流水线的冲突而导致运行速度缓慢。本文通过对嵌入式处理器的流水线, 指令集, 设备控制器等内部结构的分析和

2009-12-31 11:30:21 9

9 FIR并行滤波器设计

数字滤波器可以滤除多余的噪声,扩展信号频带,完成信号预调,改变信号的特定频谱分量,从而得到预期的结果。数字滤波器在DVB、

2008-01-16 09:47:09 1270

1270

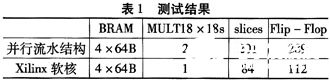

基于流水线技术的并行高效FIR滤波器设计

基于流水线技术,利用FPGA进行并行可重复配置高精度的FIR滤波器设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用

2009-03-28 15:12:27 737

737

摘要: 提出了一种采用现场可编码门阵列器件(FPGA)并利用窗函数法实现线性FIR数字滤波器的设计方案,并以一个十六阶低通FIR数字滤波器电路的实现

2009-06-20 14:05:46 1057

1057

什么是流水线技术

流水线技术

2010-02-04 10:21:39 3702

3702 采用DSPBuilder的FIR滤波器的方案实现

1.引言

在信息信号处理过程中,如对信号的过滤、检测、预测等,都要使用滤波器,数字滤波器是数字信号处

2010-03-04 17:09:38 738

738

流水线中的相关培训教程[1]

学习目标

理解流水线中相关的分类及定义;

2010-04-13 15:56:08 869

869 流水线中的相关培训教程[3]

(1) 写后读相关(RAW:Read After Write) (命名规则) :j 的执行要用到 i 的计算结果,当它们在流水线中重叠执行时,j 可

2010-04-13 16:02:57 773

773 流水线中的相关培训教程[4]

下面讨论如何利用编译器技术来减少这种必须的暂停,然后论述如何在流水线中实现数据相关检测和定向。

2010-04-13 16:09:15 4272

4272 本文通过改变通常FIR处理结构,有效地节省了资源,只使用了一套乘加器,一套FIR滤波器结构,就完成了两套FIR滤波器的功能,

2011-05-13 09:32:32 4233

4233

基于流水线技术,利用FPGA进行并行可重复配置高精度的 FIR滤波器 设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用这种FIR滤波器的设计方法可以充分发挥FPGA的优势。

2011-07-18 17:09:28 63

63 cpu流水线技术是一种将指令分解为多步,并让不同指令的各步操作重叠,从而实现几条指令并行处理,以加速程序运行过程的技术。

2011-12-14 15:29:24 4476

4476 描述了基于FPGA的FIR滤波器设计。根据FIR的原理及严格线性相位滤波器具有偶对称的性质给出了FIR滤波器的4种结构,即直接乘加结构、乘法器复用结构、乘累加结构、DA算法。在本文中给

2012-11-09 17:32:37 121

121 电镀流水线的PLC控制电镀流水线的PLC控制电镀流水线的PLC控制

2016-02-17 17:13:04 35

35 装配流水线控制系统设计

2016-12-17 15:26:59 13

13 一种改进运放共享结构的11位流水线ADC设计

2017-01-07 20:49:27 3

3 基于位并行DA结构的高速FIR滤波器_周云

2017-01-07 21:39:44 4

4 FIR滤波器,即有限脉冲响应滤波器,顾名思义,是指单位脉冲响应的长度是有限的滤波器。而根据FIR滤波器的结构形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。

2017-04-20 14:42:14 2186

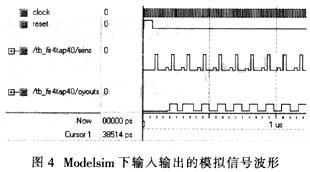

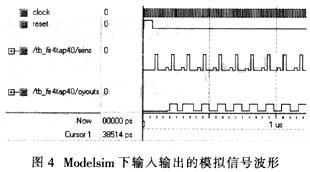

2186 摘要:有限冲击响应(FIR)滤波器是数字通信系统中常用的基本模块。文章设计了一种流水结构的FIR滤波器,通过FPGA对其进行硬什加速控制。仿真结果验证了所设计的FIR流水结构滤波器功能的正确性

2017-11-18 06:15:02 1259

1259

线性相位FIR滤波器的对称性减小了硬件规模;利用分割查找表的方法减小了存储空间;采用并行分布式算法结构和流水线技术提高了滤波器的速度,在FPGA上实现了该滤波器。

2017-11-24 15:17:27 2942

2942 分是采用分布式算法设计基于FPGA的实现结构,完全避免了乘法运算,资源优化性高;第三部分通过对FPGA的滤波器设计方案进行仿真验证,并与使用Matlab模拟滤波算法产生的波形进行比较,两者能够达到几乎一致,得出电路设计合理,滤波效果达标的结论。

2017-12-07 16:22:09 6

6 本文针对快速、准确选择参数符合项目要求的滤波器设计方法的目的,通过系统的介绍有限脉冲响应( Finite Impulse Response,FIR)滤波器的原理、结构形式以及几种FIR滤波器设计方法

2017-12-21 14:53:14 14

14 本文将讨论处理器的一个重要的基础知识:流水线。熟悉计算机体系结构的读者一定知道,言及处理器微架构,几乎必谈其流水线。处理器的流水线结构是处理器微架构最基本的一个要素,犹如汽车底盘对于汽车一般具有基石性的作用,它承载并决定了处理器其他微架构的细节。

2018-04-08 08:16:00 21822

21822

颜色表示了不同阶段的可配置性或可编程性:绿色表示该流水线阶段是完全可编程控制的,黄色表示该流水线阶段可以配置但不是可编程的,蓝色表示该流水线阶段是由GPU固定实现的,开发者没有任何控制权。实线表示该shader必须由开发者编程实现,虚线表示该Shader是可选的.

2018-05-04 09:16:00 3613

3613

本文详细讲述了通过Matlab工具设计FIR线性相位滤波器的方法, 并针对声波信号设计了优于传统结构的流水线CSD-DA结构, 该结构具有较明显的速度和面积优势。文中也通过仿真实验证实了设计的合理性

2018-08-12 09:33:37 3958

3958

在基本A/D转换结构中,有些具备高速性能,有些具备高精度性能,没有能够同时达到高速高精度的要求。流水线ADC的出现在一定程度上解决了这个难题。流水线结构可以在采样速度和转换精度之间取得较好的平衡。图1是三级流水线ADC的结构。

2019-06-08 09:39:00 2492

2492

第一部分什么是流水线 第二部分什么时候用流水线设计 第三部分使用流水线的优缺点 第四部分流水线加法器举例 一. 什么是流水线 流水线设计就是将组合逻辑系统地分割,并在各个部分(分级)之间插入寄存器

2018-09-25 17:12:02 4370

4370 自动化流水线是一个统称,包括组装流水线、皮带流水线、链板线、插件线等等,主要通过自动化系统来操作运行,不需要人工操作。

2019-05-22 06:06:00 6328

6328 流水线的平面设计应当保证零件的运输路线最短,生产工人操作方便,辅助服务部门工作便利,最有效地利用生产面积,并考虑流水线安装之间的相互衔接。为满足这些要求,在流水线平面布置时应考虑流水线的形式、流水线安装工作地的排列方法等问题。

2019-11-28 07:07:00 2039

2039 流水线在工业生产中扮演着重要的角色,优化流水线直接关系着产品的质量和生产的效率,因此成为企业不得不关注的话题。

2019-11-28 07:05:00 2088

2088 流水线又称为装配线,一种工业上的生产方式,指每一个生产单位只专注处理某一个片段的工作。以提高工作效率及产量;按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2019-11-28 07:04:00 3232

3232 流水线在工厂生产线上运用非常广泛。从产品原料到最终产品,工厂中的生产过程都是由各个生产工站实现。工站与工站之间的转运,就是通过流水线实现。

2020-06-04 10:22:14 8336

8336

L倍,其中L为并行的路数,并且运算延迟小。首先从理论上分析了基于多相滤波器的并行滤波原理,并以八路并行为例,对FIR滤波运算做了浮点仿真验证。然后用经典符号数表示以及优化定点滤波器系数,并针对滤波器系数设计了流水线结构。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 15

15 L倍,其中L为并行的路数,并且运算延迟小。首先从理论上分析了基于多相滤波器的并行滤波原理,并以八路并行为例,对FIR滤波运算做了浮点仿真验证。然后用经典符号数表示以及优化定点滤波器系数,并针对滤波器系数设计了流水线结构。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 本文介绍一种基于SoPC的FIR滤波器设计方案,设计流程如图l所示。该设计方法程序简单,调试方便,得到的FIR滤波器精确度高。

2021-03-24 09:18:27 2712

2712

按照流水线的输送方式大体可以分为:皮带流水装配线、板链线、倍速链、插件线、网带线、悬挂线及滚筒流水线这七类流水线。

2021-07-05 11:12:18 6087

6087

,每个子过程由专门的功能部件来实现。• 把多个处理过程在时间上错开,依次通过各功能段,这样,每个子过程就可以与其他的子过程并行进行。流水线中的每个子过程及其功能部件称为流水线的级或段,段与段相互连接形成流水线。流水线的段数称为流水线的深度。二、表示流水线的表示方法:时空图• 时空图从时间和空间两

2021-10-20 20:51:14 6

6 1989 年推出的 i486 处理器引入了五级流水线。这时,在 CPU 中不再仅运行一条指令,每一级流水线在同一时刻都运行着不同的指令。这个设计使得 i486 比同频率的 386 处理器性能提升了不止一倍。

2022-09-22 10:04:23 1258

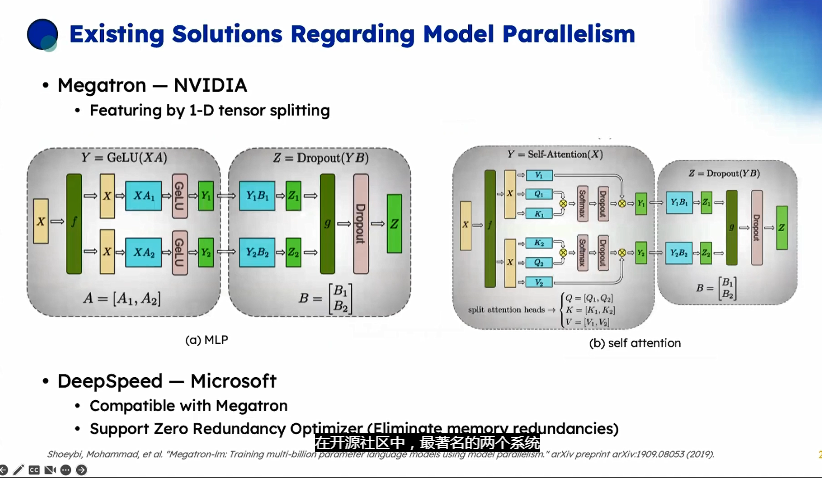

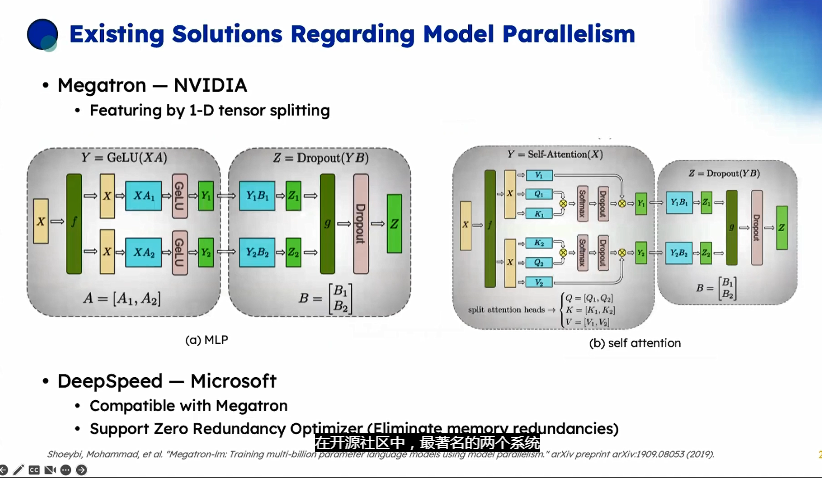

1258 张星并行和流水线并行技术通常被描述为模型并行,在开源社区中,最著名的两个系统是NVIDIA的Megatron- M和Microsoft的DeepSpeed。

2023-03-23 17:21:29 1395

1395

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。FIR 滤波器具有严格的线性相频特性,同时其单位响应是有限长的,因而是稳定的系统,在数字通信、图像处理等领域都有着广泛的应用。

2023-03-27 11:33:53 618

618

jenkins 有 2 种流水线分为声明式流水线与脚本化流水线,脚本化流水线是 jenkins 旧版本使用的流水线脚本,新版本 Jenkins 推荐使用声明式流水线。文档只介绍声明流水线。

2023-05-17 16:57:31 613

613 本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 653

653

点击上方 蓝字 关注我们 本文将回顾对称 F IR 滤波器 的高效 FPGA 实现的注意事项。 本文将推导对称 FIR 滤波器的模块化流水线结构。我们将看到派生结构可以使用 Xilinx

2023-05-26 01:20:02 441

441

FIR(Finite Impulse Response)滤波器是一种有限长单位冲激响应滤波器,又称为非递归型滤波器。

2023-06-01 11:11:34 821

821

![]()

电子发烧友App

电子发烧友App

评论