在红外抄表等电路中,要用到38kHz载波来实现串口通讯,其串口就是普通的UART。总结出6种调制电路供发烧友们参考。1、基于三态门的标准的调制方式:当UART_TX为低电平时,38kHz信号可以通过

2016-12-30 18:24:57

上才都有显示,这时测出的电压是5V上面的是用proteus仿真的情况,在实际中,我看jtag模块上都有一个74HC244这种芯片,我上网搜了一下,说244是三态8同相缓冲/驱动器,说是增加什么驱动

2014-07-20 11:49:56

FPGA 门数计算方法FPGA 门数计算方法 FPGA 等效门数的计算方法有两种: 1.把FPGA 基本单元(如LUT+FF ,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数

2012-08-11 10:29:07

iic_sda_out赋想要输出的值即可,当想要使用iic_sda作为输入时,只需要令iic_en为0,然后去读iic_sda的电平即可。但是需要注意三态门或者说时双向端口定义最好只定义在顶层文件中,顶层

2020-06-03 18:32:58

1. 把FPGA 基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA 基本单元的等效门数,然后乘以基本单元的数目就可以得到FPGA 门数

2012-03-01 10:08:53

FPGA中等效逻辑门概念数的计算方法有两种,一是把FPGA基本单元(如LUT+FF,ESB/BRAM)和实现相同功能的标准门阵列比较,门阵列中包含的门数即为该FPGA基本单元的等效门数,然后乘以

2012-08-10 14:05:35

我遇到的情景中,一般后仿真出现不定态的原因有三个:更多的后仿出现不定态的的情形可以参考以下文章。验证那些事最近陆续写了点工作方面的小文章,遂决定新开一个公众号,专门放工作相关的文章,就叫《超人验证

2022-01-18 06:35:33

FPGA布线开关的电路设计1 研究方法及其条件假定2 导通晶体管布线开关设计 2.1导通晶体管布线开关尺寸优化2.2 导通晶体管存在的问题及其改进3 三态缓冲布线开关的设计3.1三态缓冲器尺寸优化3.2 三态缓冲布线开关的缺点及其改进4 各种布线开关性能比较及其建议

2011-03-02 09:50:16

出来的是一个什么样的电路,计数器选择器 三态门等等,理解时序,逻辑是一拍一拍的东西,在设计初期想的不是很清楚的时候可以画画时序图,这样思路会更加的清晰,还有就是仿真很重要,不要写完程序就去往FPGA中去

2017-05-02 16:59:07

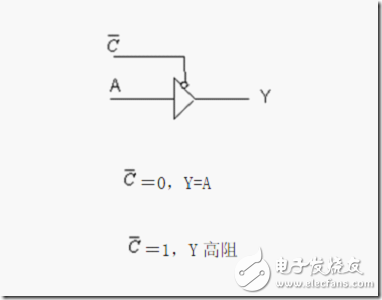

三态门的工作原理是什么?

2021-05-20 06:55:47

三态门输入信号和输出信号之间接电阻是什么用法?

2017-04-09 19:36:20

一、三态单片机IO的三态是指:高电平(1)、低电平(0)、高组态(Z)。二、高阻态高阻i是一种电路状态.既不是高电平,也不是低电平,以高阻态对下级电路输出,下级电路什么影响也没有.高阻态的IO电平

2021-11-25 06:42:28

如图是一个三态反相缓冲器,我想把它和一个自偏电阻连起来做一个放大器。

2019-01-28 16:40:28

如果我在其中一个存储器上使用32位三态输出,则合成器会添加一个切片。有人能告诉我内部三态缓冲器在FPGA架构中的位置(我得到了kintex 7)吗?我在CLB指南中找了它,但没找到

2019-03-04 13:17:18

。看起来微处理器正在写入FPGA而不是从FPGA读取。但情况应该不是这样,而应该恰恰相反!在推断三态缓冲区时,我是否设置了错误?当我在planAhead中打开设计时,我可以看到“io_data”被认为是

2019-03-08 14:01:02

三态输出门的电路图和图形符号

2019-10-25 07:17:31

1、AD5420的SDO是否是三态输出脚

2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正确

2023-12-20 08:08:51

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?

现在问题是FPGA引脚不够用了,能否将两片AD9280数据D0-D7接在一起,时钟是共用的,两片AD同步输出,在数据开始输出后用三态引脚控制取数?

2023-12-14 06:49:33

一片ADS1211时要求其余两片的ADS1211的SDOUT引脚此时具有三态状态,以实现让出SPI数据接口的目的,ADS1211的SDOUT具有三态状态,可是:The CS signal does

2019-05-23 08:07:10

CPLD/FPGA实现I2C的透传,使用三态门,那么SDA的方向应向该如何确定?assign SCL_OUT = SCL_IN;wire mid;assign mid = dir?1'bz

2019-01-11 09:49:55

我正在寻找在Spartan 3A中使用多路复用器与三态缓冲器之间的比较。从某个区域和时间角度来看哪个更好?谢谢,戴尔以上来自于谷歌翻译以下为原文I'm looking for a

2019-01-16 10:37:07

PSoC Creator组件数据手册/PSoC 4:三态缓冲器 (Bufoe) 组件是非反相缓冲器,其使能信号高电平有效。当输出使能信号为真时,次缓冲器用作标准缓冲器。当输出使能信号为假时,次缓冲器关闭。

2013-07-03 11:15:11

inout Key_inout;wire Key_input;//输入reg Key_output;//输出reg Key_Ctr;//三态控制assign Key_inout=Key_Ctr

2014-09-23 15:34:43

芯片外部引脚很多都使用inout类型的,为的是节省管腿。一般信号线用做总线等双向数据传输的时候就要用到INOUT类型了。就是一个端口同时做输入和输出。 inout在具体实现上一般用三态门来实现。三态

2012-01-17 10:08:04

这两个模块都是编写的一个4位4通道的三态总线驱动器,编译后RTL图是一样的第二个模块仿真是没有问题的,输出都是正常的但,第一个模块从仿真上看,当en 为“00”时输出是正常的,en其余状态时,输出

2019-01-30 11:18:46

一介绍。当三态输出信号es选通时,即es=“1”,PC可输出,否则输出为高阻态。数据或地址与总线相关的子模块都需采用三态门。由于采用了三态门,最好用QuartusⅡ软件来进行编译,Max+plusⅡ有时

2014-12-04 14:35:41

一介绍。当三态输出信号es选通时,即es=“1”,PC可输出,否则输出为高阻态。数据或地址与总线相关的子模块都需采用三态门。由于采用了三态门,最好用QuartusⅡ软件来进行编译,Max+plusⅡ有时

2014-12-04 14:36:22

如果:红色-0,绿色-1,蓝色-2

输入:数组

输出:布尔数组或簇

例如:输入数组为〔0 1 2 1 0〕

希望输出显示为红色,绿色,蓝色,绿色,红色的一组三态灯。

网上给的子vi是利用bool引用句柄实现一个灯的三态显示,如果数组元素少的话用枚举可以实现,但是如果数组元素很多,有什么简便的方法吗?

2015-12-09 14:32:54

求教大佬:proteus中用74LS164驱动共阳极数码管显示,显示的时候数字是对的,但是数字一直在闪烁是为什么呢?是因为没有在74LS164的输出端接三态门吗?

2020-11-02 06:42:30

等,要求信号为三态类型,也就是我们所说的输入输出(inout)类型。那么,本节梦翼师兄将和大家一起来探讨三态门的用法。项目需求设计一个三态门电路,可以实现数据的输出和总线“挂起”。系统架构 模块功能

2019-12-12 16:11:51

本帖最后由 gk320830 于 2015-3-4 23:25 编辑

【经典】集电极开路,漏极开路,推挽,上拉电阻,弱上拉,三态门,准双向口

2012-07-29 21:17:03

并不能直接并接使用,否则这些门的输出管之间由于低阻抗形成很大的短路电流(灌电流),而烧坏器件.在硬件 上,可用OC门或三态门(ST门)来实现. 用OC门实现线与,应同时在输出端口应加一个上拉电阻.3

2016-08-23 21:39:46

,VCCBRAM,VCCAUX和VCCO,以实现最小电流消耗,即I / O在上电时为3。我应该关心这件事吗?在上电过程中,I / O引脚是否应该处于三态?任何帮助将不胜感激。谢谢,菲利普

2020-07-30 09:51:29

AD9280三态引脚是否只是控制数据输出端的,和转换过程没有关系?现在问题是FPGA引脚不够用了,能否将两片AD9280数据D0-D7接在一起,时钟是共用的,两片AD同步输出,在数据开始输出后用三态引脚控制取数?

2019-01-09 09:30:29

三态门和OC门一、OC门实际使用中,有时需要两个或两个以上与非门的输出端连接在同一条导线上,将这些与非门上的数据(状态)用同一条导线输送出去。因此,需要一种新的与非门电路来实现线与逻辑,这种门电路

2008-05-26 13:01:37

的不足,同时也方便在现场可编程门阵列(FPGA)中增加一些其他相关的应用功能,因此在FPGA中实现CVSD语音编译码调制功能的前景将是非常广阔的。这里将详细介绍什么是CVSD?其算法分析如何在FPGA中实现?

2019-08-07 07:04:27

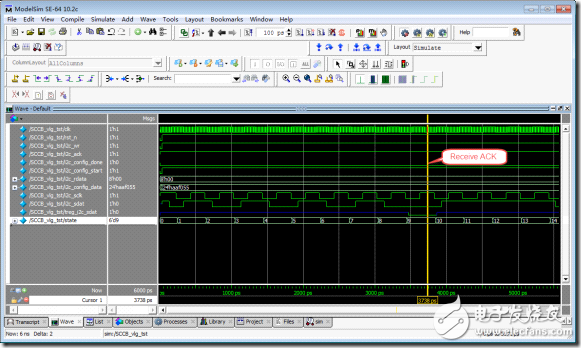

`刚刚本科毕业,假期导师要求做一个设计。实验室没有做过FPGA的学长只好问网上的各位了。写好的FPGA代码进行RTL仿真波形是符合要求的,如下图。但是做门级仿真的时候,时序就不对了,变成了这样

2016-08-06 12:12:03

三态LED 子vi

2017-01-13 10:39:39

在一起,并且在需要将门彼此分离的应用中,可以使用三态缓冲器或三态输出驱动器。“三态缓冲器”除了上面看到的标准数字缓冲器外,还有另一种类型的数字缓冲器电路,其输出可以在需要时从其输出电路“电子断开”。这种

2021-01-26 09:16:58

设计上,它会成为一个错误!对我来说,三态使能引脚没有连接到芯片上的引脚,不是它是一个输出,所以它没有转换约束,测试设计没有用户约束文件,只是选择IO向导为选择IO IP制作的文件, 所以我在xilinx

2020-08-05 12:07:55

/ axigpio_v2_0.tcl中有一个额外的']'是第246行的结尾在GPIO2接口上添加三态GPIO端口时会导致错误。以上来自于谷歌翻译以下为原文There is a small bug

2019-04-19 10:32:27

三态门高阻态时,同或门输出状态怎么判断?F的 逻辑表达式

2015-12-15 10:59:57

大家好!我想知道如何在FPGA中使用VHDL实现过零检测器。所以我想实现一个数字常数小数鉴别器。 firt部分提供了双极性信号,但我想知道如何在vhdl中实现过零检测器。感谢您的帮助!以上来自于谷歌

2019-01-29 08:16:40

亲爱的大家! 如何在IOB中为spartan-3生成FPGA使用TFF(TFF1和TFF2三态触发器)? 我想在spartan-3 FPGA(Spartan-3 GenerationFPGA用户指南

2019-06-28 09:53:28

必须是明确的。 OFDDRSE元素可用于IOB中的数据路径,但我找不到更“完整”的元素,其中还包含三态路径(OFDDRTRSE只有简单的三态路径)。我尝试使用OFDDRSE并使用它来控制三态上的启用

2019-05-13 08:41:11

在FPGA中,动态相位调整(DPA)主要是实现LVDS接口接收时对时钟和数据通道的相位补偿,以达到正确接收的目的。那么该如何在低端FPGA中实现DPA的功能呢?

2021-04-08 06:47:08

]set to input with tri-state,我给芯片配置完之后,只需要将DO(数据)引脚设置输入就行了吗?不太懂这里的输入三态啥意思?[size=18.6667px]而且,时钟线应该没啥

2017-03-29 10:29:23

如何才能制作一个三态指示灯?需要什么材料等等

2014-10-28 19:51:17

反相器的速度与哪些因素有关?什么是转换时间和传播延迟呢?怎样去设计一种CMOS三态缓冲器的电路呢?

2021-10-20 06:24:39

本帖最后由 yogaqingyun 于 2016-1-11 13:17 编辑

b=1时输出高阻态,cde都是高电平,当d变为低电平,ce也都为低;b=0时,输出为a是低电平。求个小程序,我自己的仿真总是不对啊。用Verilog描述完是这样的就行。

2016-01-11 13:03:18

要找一个7路输入/输出并带高阻的三态输出的逻辑IC,体积要小点的,有知道的请推荐一下,谢谢!!!积分只有13分,全给了。

2016-01-04 11:36:40

大家好,我是一名大学生,最近刚接触数字电子和单片机,产生了兴趣后,尝试着去学习它,但是碰到不少问题,其中TTL门中的OC门和三态门不是很清楚,所以找了几道题想知道详细的解答,我知道答案,但是为什么是这个结果,请各路大神多关照一下,带带初级生。

2014-03-13 23:56:56

如图一中,unused pin是配置为“三态输入输入”,还是“三态输入加弱上拉”。图二中,为什么要把这些dual_purpose_pin设置为“use as regular IO”.他们可是专用的引脚的啊

2018-07-11 23:35:47

我有一个使用MCLR作为输入的项目。用PICTIT2 MCLR放在编程后的三态,但是用皮卡4,似乎PIN保持高。这有什么设置吗? 以上来自于百度翻译 以下为原文 I have a project

2018-10-26 16:11:59

描述PCB_三态极性指示器使用 1K 电阻 (x2) 和任何硅二极管。顶部的绿色 LED 底部的红色。使用厚二极管腿作为探针和带有鳄鱼夹的接地线。

2022-08-30 07:31:27

新人在工作中经常碰到三态门与高阻态;请教技术大佬,这两个到底是什么东西 ?

2021-04-07 06:59:01

1、AD5420的SDO是否是三态输出脚2、MCU的SPI接口配置CPOL=0、CPAH=0,是否正确

2018-12-20 09:26:31

ISIM不能处理1Mb信号)。我也测试了它,用逻辑分析仪我可以看到信号,地址和写入数据是正确的,时间也很好,但读数不对。我的猜测是它与双向数据总线有关,我知道内部三态在spartan-3上不再可用,但我

2019-06-26 10:24:04

请问这个三态门为什么不能实现非功能?它的逻辑表达式不应该是A非吗?

2023-04-26 11:49:06

请问这个三态门为什么不能实现非功能?它的逻辑表达式不应该是A非吗?

2023-05-10 17:44:20

逻辑门及组合逻辑电路实验实验目的1. 掌握与非门、或非门、与或非门及异或门的逻辑功能。2. 了解三态门的逻辑功能以及禁止状态的判别方法。了解三态门的应用。3. 掌握组合逻辑电路的设计和实现方法。4.

2008-09-25 17:28:34

集电极开路 漏极开路 推挽 上拉电阻 弱上拉 三态门 准双向口

2016-06-02 16:22:21

高阻态和三态门高阻态 高阻态的实质:电路分析时高阻态可做开路理解。你可以把它看作输出(输入)电阻非常大。他的极限可以认为悬空。也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际

2019-01-08 11:03:07

数字电路常见术语:高阻态,三态门高阻态常用的表示方法

2021-03-01 11:09:49

悬空,顾名思义,就是不接任何器件啦高阻态:无上拉和无下拉,对外表现出电平不确定性不是所有的单片机都支持三态输出。三态输出一般由寄存器控制,需进行配置。高阻态既然无确定电平,怎么能做输出呢?把一个端口

2021-11-24 08:19:25

小波盲源分离算法的仿真及FPGA实现:提出了一种基于小波变换的盲源分离方法,在理论分析和仿真结果的基础上,给出了FPGA 的实现方案。针对传统盲分离算法对源信号统计特征敏

2009-06-21 22:44:09 21

21 本文就三态电路在FPGA中的应用作了详细的说明。文章首先描述了一个调用lpm中三态电路模块的VHDL程序,这个程序会出现编译不能通过的问题。然后从这个问题出发,通过尝试三态电

2010-08-06 16:56:22 27

27 介绍了用Multisim仿真软件分析三态门工作过程的方法,目的是探索三态门工作波形的仿真实验技术,即用Multisim仿真软件中的字组产生器产生三态门的控制信号及输入信号,用Multisim中示

2011-05-06 15:59:38 0

0 dac0832ad08098259a,825382508255等芯片的fpga实现及仿真

2016-01-20 15:12:47 13

13 的一个例子,HDL语言的INOUT端口仿真暨三态门仿真,VerilogHDL 的三态门实现与仿真,ARM 总线的三态门实现与仿真

2019-07-09 16:49:27 10

10 核的不同模块进行实体/块的仿真。前文回顾如何测试与验证复杂的FPGA设计(1)——面向实体或块的仿真在本篇文章中,我们将介绍如何在虹科IP核中执行面向全局的仿真,而这也是测

2022-06-15 17:31:20 389

389

电子发烧友App

电子发烧友App

评论