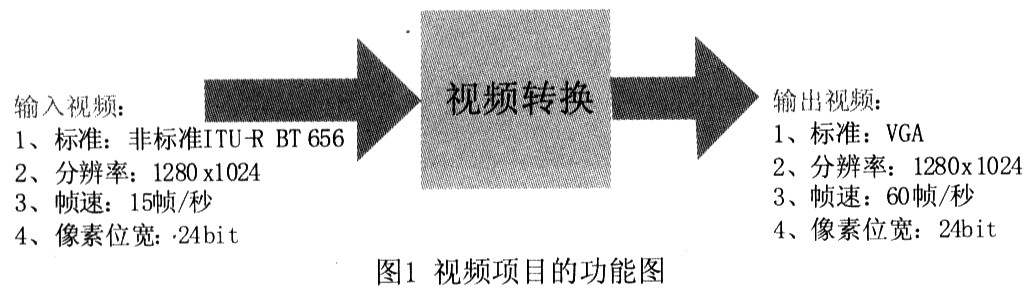

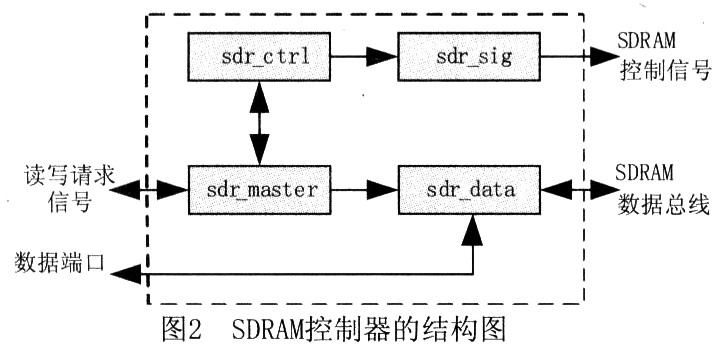

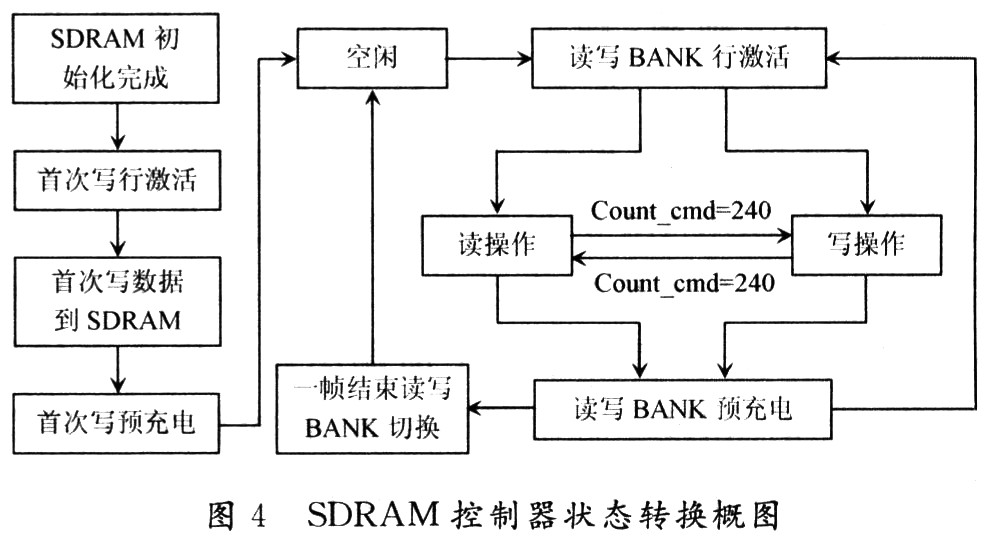

本文介绍了一种基于FPGA的用于高分辨率视频图像处理的SDRAM控制器的设计方法。通过设置SDRAM的工作状态,使其工作在猝发模式。在视频时序信号控制下,用多行连续的SDRAM存储空间,存取视频

2014-02-10 14:10:21 3023

3023

设计了一种基于FPGA的实时视频图像采集处理电路系统。采用FPGA作为整个系统的控制和图像数据处理中心。DDR2 SDRAM为高速储存模块核心器件,CMOS 7670为视频图像采集器件。

2018-02-10 02:43:55 19311

19311

FPGA之SDRAM控制器设计(二):刷新这次要来解决上次留下来的刷新问题,在100us后首先要经过两次刷新才进行模式寄存器设置。这颗SDRAM芯片需要每隔64ms对8192行(列地址10-位,行

2021-07-30 07:48:42

基于SDRAM控制器实现FPGA模块化和通用性的解决方案设计

2020-12-22 07:58:55

上找到了几个sdram控制器,但是我无法存储或读取任何内容。我问的是你有没有改变sdram的工作代码并使它像sram那样我可以测试我的硬件?你有什么想法我怎么测试芯片是否存活?最好的祝福。我喜欢

2019-05-16 13:10:57

描述此参考设计演示了如何实现 SDRAM 存储器并通过接口连接到高性能微控制器 TM4C129XNCZAD。为了实现此设计,其中采用了该微控制器的 EPI 接口来连接 256Mbit SDRAM

2018-08-30 09:31:51

SDRAM的控制结构复杂,常用的方法是设计SDRAM通用控制器,这使得很多人不得不放弃使用SDRAM而使用价格昂贵的SRAM。为此,笔者在研究有关文献的基础上,根据具体情况提出一种独特的方法,实现了

2009-11-13 11:37:08

SDRAM的基本工作原理是什么SDRAM的基本读写操作步骤是什么一种简单的通用SDRAM控制器的实现

2021-05-10 06:26:44

SDRAM(同步动态存储器)是一种应用广泛的存储器,具有容量大、数据读写速度快、价格低廉等优点,特别适合那些需要海量存储器的应用领域,例如视频方面。那么有谁知道,高速SDRAM控制器的视频有哪些吗?

2019-08-09 06:23:43

本次发布三例 SDRAM 控制器参考设计及 IP Core Generator 支持调用SDRAM 控制器 IP。 1. 32-bit SDRAM Controller for device

2022-10-08 07:59:17

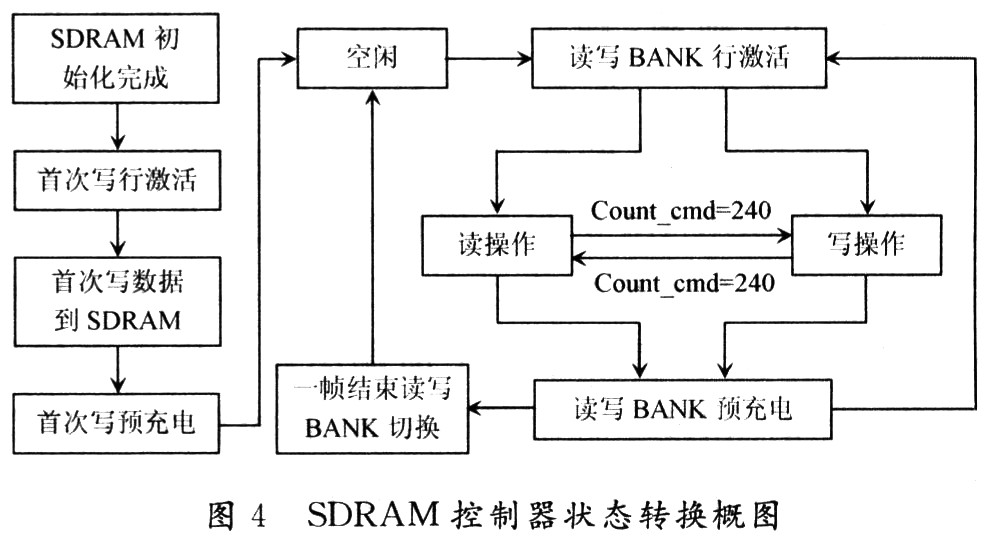

基于FPGA的SDRAM控制器设计(三)读写作者:小周 本文为明德扬原创及录用文章,转载请注明出处! SDRAM控制器设计的主要功能是能对SDRAM进行读写操作,本工程实现了SDRAM的初始化、自动

2020-04-23 11:31:47

在这一讲中,Kevin先带着大家了解一下我们这一套视频教程《SDRAM那些事儿第一季—轻松设计SDRAM控制器》中所要讲的这个项目。这个项目总的来讲,就是设计一个简单的SDRAM控制器,PC机通过

2017-05-08 22:14:21

,我们就来完成读模块,然后对这个SDRAM控制器稍加完善就可以应用到项目中了。对于读模块的设计:与写模块一致,只需要将写模块复制一份稍加修改就可以了。在此不做赘述!!!如有疑问,请观看配套视频教程进行

2017-05-08 22:28:13

项目的代码调试,过程相当繁琐,Kevin就不在电子版中进行讲解了(毕竟语文是数学老师教的。。。/捂脸)。对于完整项目的调试,强烈建议大家观看《轻松设计SDRAM控制器》的第九讲视频。四、最后的话Kevin

2017-05-08 22:38:37

对于很多刚接触SDRAM的朋友来说,还不能完整的设计出SDRAM控制器,很大一部分原因就是没了解到仲裁机制。仲裁机制应该是说SDRAM控制器中最关键的部分,理解并掌握仲裁机制对于设计SDRAM控制器

2017-05-08 22:22:44

第五讲介绍完仲裁机制之后,相信很多朋友都在想,仲裁模块写好了,那写模块、读模块等与SDRAM相关操作的模块应该怎么写代码呢?是的,在学习完仲裁机制之后只是相当于给SDRAM控制器建立了一个框架,这个

2017-05-08 22:25:30

的SDRAM控制器哦!!!!自己也是一时兴起,看到很多技术类的微信公众号,所以自己也开通了微信公众号【开源骚客】(微信号:OpenSoc)微信公众号,主要是用来分享一些不适合博文写出来的东西,博文可能大家

2017-05-08 22:20:54

,但由于接触FPGA时间不长,虽认真研读过各种关于SDRAM的资料,却仍然无法使用Verilog设计出一个工作正常的SDRAM控制器。在本文中,【开源骚客】将会先引入一个SDRAM控制器简单例子的演示

2016-10-16 23:04:43

第1节 SDRAM读写控制器--作者:小黑同学本文为明德扬原创及录用文章,转载请注明出处!1.1 总体设计1.1.1 概述同步动态随机存取内存(synchronousdynamic

2020-10-15 15:16:02

为什么选择高速HIL仿真器来实现电机控制器测试?为何需要基于FPGA的硬件在环仿真器?

2021-04-28 06:33:38

使用Verilog实现基于FPGA的SDRAM控制器

2012-08-20 19:35:27

本文介绍一种通用SDRAM控制器的FPGA模块化解决方案。

2021-05-07 06:42:49

求大佬介绍一种通用SDRAM控制器的FPGA模块化解决方案

2021-04-08 06:40:34

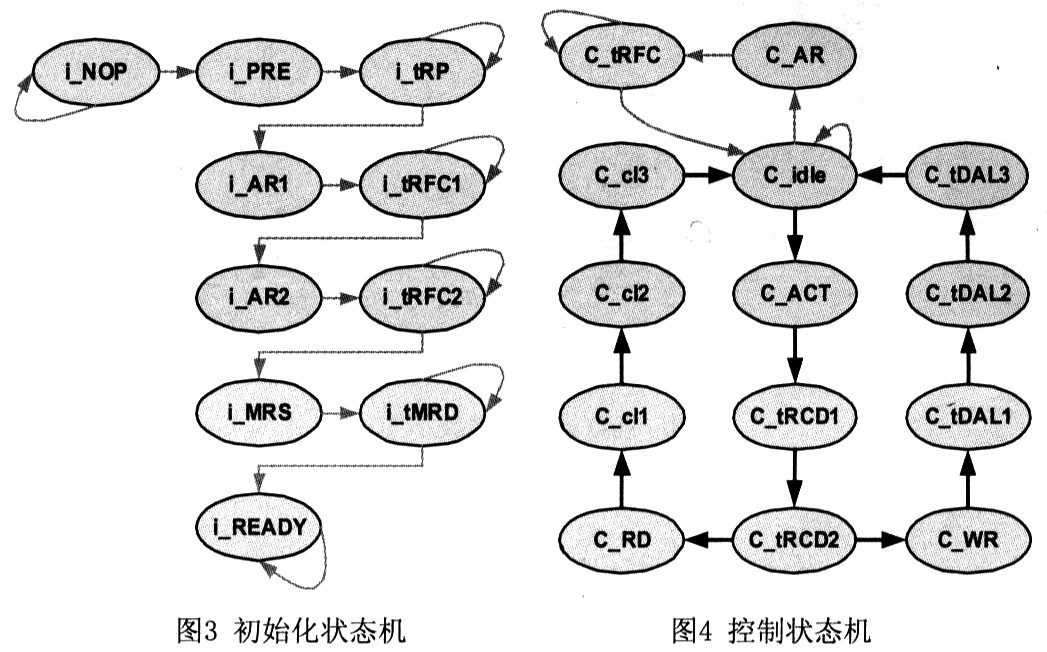

。DDR的时序与SDRAM是相似的,学好SDRAM后,理解DDR2和DDR3就非常容易了。2、至简设计代码实现(附录部分代码)下面是使用至简设计法实现的SDRAM控制器,该控制器使用了四段式状态机,其他信号

2017-08-02 17:43:35

基于FPGA的SDRAM控制器设计(原创分享)—自动刷新设计作者:小周本文为明德扬原创及录用文章,转载请注明出处!SDRAM控制器设计的主要功能是能对SDRAM进行读写操作,本工程实现了SDRAM

2020-04-15 14:43:50

基于FPGA的高速A_D转换控制器设计采 用 器 件 实 现 对 高 速 转 换 芯 片 的 实 时 采 样 控 制 解决 了 传 统 方 法 的 速 度 问 题 使 用 语 言 采 用 自 顶 向

2012-08-11 15:36:53

进行了DDR3 SDRAM控制器的编写,分析并提出了提高带宽利用率的方法。最终将其进行类FIFO接口的封装,屏蔽掉了DDR3 IP核复杂的用户接口,为DDR3数据流缓存的实现提供便利。系统测试表明,该

2018-08-02 09:34:58

基于FPGA的图形式AMLCD控制器该如何去设计?怎样去设计一种VGA视频接口电路?

2021-06-08 06:57:57

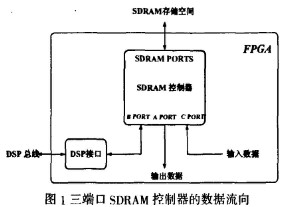

本文提出了一种基于FPGA的SDRAM控制器的设计方法,并用Verilog给于实现,仿真结果表明通过该方法设计实现的控制器可以在FPGA芯片内组成如图1所示的SDRAM接口,从而使得系统用户对SDRAM的操作非常方便。

2021-04-15 06:46:56

的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。利用DSP与FPGA设计运动控制器,其中DSP用于运动轨迹规划、速度控制及位置控制等功能;FPGA完成运动控制器的精插补功能,用于精确计算步进电机或伺服驱动元件的控制脉冲,同时接收并处理脉冲型位置反馈信号。那么,我们具体该怎么做呢?

2019-08-06 06:27:00

基于FPGA的SDRAM控制器包括哪些部分呢?如何去实现一种基于FPGA的SDRAM控制器设计呢?

2021-11-04 06:47:44

SDRAM控制器基本操作原理是什么?如何去设计并实现一种SDRAM控制器?

2021-06-07 06:01:39

的工作时钟频率。然而,设计至DDR3的接口也变得更具挑战性。在FPGA中实现高速、高效率的DDR3控制器是一项艰巨的任务。直到最近,只有少数高端(昂贵)的FPGA有支持与高速的DDR3存储器可靠接口的块

2019-08-09 07:42:01

如何解决SDRAM控制器设计刷新的问题?

2021-11-04 07:20:02

怎样去设计高速PID控制器?怎样对高速PID控制器进行仿真?

2021-04-28 06:43:09

的高速性和低单位成本使其引人注目。 因此我们需要的是一种访问SDRAM的方法,但是要易于使用静态内存。这就是创建内存控制器的原因。它们充当转换层:一方面,它们为用户提供了易于使用的内存接口,然后

2020-09-23 10:59:56

我移植网上的一个sdram vga的代码到ep4ce6e22c8n开发板上,它里面的sdram控制器是tequan写的,但是我移植后,却得不到代码要的效果,sdram读写出来的数据有错,调了好久也

2014-04-03 16:23:55

DDR SDRAM在嵌入式系统中有哪些应用?DDR SDRAM的工作方式有哪几种?怎样去设计DDR SDRAM控制器?

2021-04-30 07:04:04

SDRAM控制器的主要特点是什么?SDRAM控制器的状态流程是怎样的?SDRAM控制器有哪些功能?

2021-06-26 07:35:01

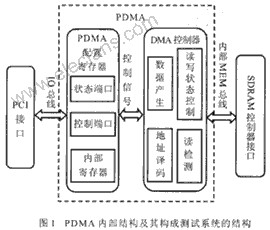

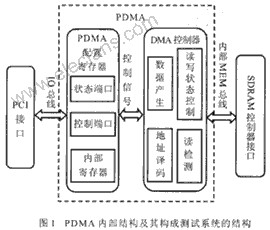

用什么方法去测试SDRAM控制器的性能?PDMA的结构及工作原理是什么?RTL仿真的顺序是什么?

2021-04-08 06:19:50

本帖最后由 upmcu 于 2012-7-28 15:07 编辑

截图:LED显示控制系统中SDRAM控制器的设计.pdf基于FPGA的DDR2+SDRAM数据存储研究.pdf基于FPGA

2012-07-28 14:40:53

转载▼网上有很多的SDR SDRAM控制器的代码,但都是基于burst1/2/4/8模式下的,这种模式下传输高速的相机数据还是有点拮据的,所以花了几天把这些模式改造成了页突发模式。我的这个控制器模型

2014-09-03 00:08:33

针对SDRAM 控制器读写数据块访问延时长、速度慢的问题,提出时间隐藏技术,将其应用于SDRAM 控制器的设计,采用FPGA实现。实验结果表明,时间隐藏技术有效缩短了数据块读写访问

2009-03-25 09:00:34 15

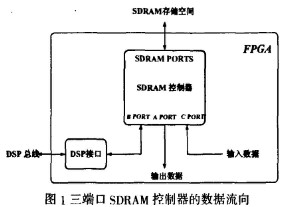

15 设计实现了一种基于FPGA 的,可用于多数据缓存的、能够高效利用带宽的多端口SDRAM 控制器。本文使用状态机的设计思想,采用Verilog 硬件描述语言设计了时序控制程序。得到的SDR

2009-08-27 09:43:33 22

22 简要介绍了SDRAM工作原理并认真研究了Altera提供的SDRAM控制器,根据实际系统使用需要加以修改简化,设计了对修改后控制器进行操作的状态机。采用全页突发读写模式,每次读/写

2009-12-26 17:02:56 70

70 本文采用Altera 公司的Stratix 系列FPGA 实现了一个三端口非透明型SDRAM 控制器,该控制器面向用户具有多个端口,通过轮换优先级的设计保证了多个端口平均分配SDRAM的带宽且不会降

2010-03-03 14:37:14 11

11 简要介绍了SDRAM工作原理并认真研究了Altera提供的SDRAM控制器,根据实际系统使用需要加以修改简化,设计了对修改后控制器进行操作的状态机。采用全页突发读写模式,每次读/写后自动

2010-07-21 17:31:37 38

38 本文介绍了DDR3 SDRAM 的基本特点和主要操作时序,给出了一种基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的设计方法。详述了控制器基本结构和设计思想,分析了各模块功能与设计注意事项,并

2010-07-30 17:13:55 30

30 摘要: 介绍了SDRAM的存储体结构、主要控制时序和基本操作命令,并且结合实际系统,给出了一种用FPGA实现的通用SDRAM控制器的方案。

关键词:

2009-06-20 12:51:58 834

834

摘 要:介绍了SDRAM的特点和工作原理,提出了一种基于FPGA的SDRAM控制器的设计方法,使用该方法实现的控制器可非常方便地对SDRAM进行控制。

关键

2009-06-20 13:04:51 2075

2075 实时视频采集系统的SDRAM控制器设计

0 引 言 在PAL→VGA的实时视频采集系统中,由于视频数据流的数据量大、实时性要求高。需要高速大容量的存

2009-11-24 09:33:19 811

811

我们设计了一个PDMA(Programmable Direct Mem o ry Access)用于测试SDRAM控制器的性能。在SoC中,SDRAM控制器往往跟多个IP模块(图形处理单元,音频处理单元等)交换数据,采用多个PDMA通道

2010-07-02 18:31:41 1655

1655

文中在介绍DDR2的工作原理的基础上,给出了一个用VHDL语言设计的DDR2 SDRAM控制器的方法,并且提出了一种在高速图像处理系统中DDR2 SDRAM的应用方案,同时在Virtex-5系列的FPGA上得到了实现

2011-07-23 10:03:16 5102

5102 SDRAM存储芯片拥有快速读写的性能,可以应用以回波模拟系统作为数据高速缓存器。SDRAM芯片是由SDRAM控制器控制的, SDRAM控制器有严格的控制时序和工作状态,可以使用有限状态机理论

2011-10-24 15:08:05 0

0 通过设计基于CPLD 的SDRAM 控制器接口,可以在STM系列、ARM系列、STC系列等单片机和DSP等微处理器的外部连接SDRAM,增加系统的存储空间。

2012-02-16 17:06:47 45

45 使用功能强大的FPGA来实现一种DDR2 SDRAM存储器的用户接口。该用户接口是基于XILINX公司出产的DDR2 SDRAM的存储控制器,由于该公司出产的这种存储控制器具有很高的效率,使用也很广泛,

2013-01-08 18:15:50 237

237 基于FPGA的高速A_D转换控制器设计。

2016-05-10 13:45:28 30

30 Xilinx FPGA工程例子源码:DDR SDRAM控制器参考设计VHDL代码

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源码:DDR SDRAM控制器verilog代码

2016-06-07 14:13:43 38

38 高速图像存储系统中SDRAM控制器的实现

2016-08-29 15:02:03 10

10 华清远见FPGA代码-SDRAM读写控制的实现与Modelsim仿真

2016-10-27 18:07:54 26

26 DDR2SDRAM控制器IP功能测试与FPGA验证_陈平

2017-01-07 21:45:57 3

3 基于VHDL的SDRAM控制器的实现

2017-01-22 13:43:27 12

12 DDR2SDRAM控制器在机载显控系统中的应用_孙少伟

2017-03-19 11:26:54 1

1 EPM1240的SDRAM控制器的设计

2017-10-31 08:24:31 21

21 为了满足高速图像数据采集系统中对高带宽和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的设计方法,提出了一种基于Verilog-HDL 语言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

控制器,在介绍控制器的逻辑结构的基础上,对FPGA与SDRAM间数据通信进行了时序分析,实现SDRAM 带有自动预充电突发读写和非自动预充电整页读写。

2017-11-18 12:42:03 2054

2054

逻辑复杂,接口方式与普通的存储器差异很大。为了解决这个矛盾,需要设计专用的SDRAM控制器,使用户像使用SRAM -样方便的使用SDRAM。考虑到控制器的通用性,本文中提出了一种通用的SDRAM控制器的FPGA设计,FPGA内部采用状态机的方式。该设计采用了AD公

2017-11-28 19:51:26 5

5 随着大规模集成电路和高速、低功耗、高密度存储技术的发展,SDRAM动态存储器因容量大、速度快、价格低廉等优点,现已成为PC内存的主流。然而SDRAM存储器内部控制逻辑十分复杂,时序要求也非常严格,因此需要设计专门的SDRAM控制器来实现系统对SDRAM的访问。

2018-04-30 10:58:00 5070

5070

SDRAM 具有存储容量大、速度快、成本低的特点,因此广泛应用于雷达信号处理等需 要海量高速存储的场合,但是SDRAM 的操作相对复杂,需要有专门的控制器配合处理器 工作完成数据的存取操作。随着FPGA 技术的快速发展及其应用的普及,用FPGA 实现 SDRAM 控制器是目前最流行的技术手段。

2019-04-26 08:06:00 2129

2129

实现数据的高速大容量存储是数据采集系统中的一项关键技术。本设计采用Altera 公司Cyclone系列的FPGA 完成了对DDR SDRAM 的控制,以状态机来描述对DDR SDRAM 的各种时序

2019-08-14 08:00:00 3401

3401

本文档的主要内容详细介绍的是FPGA读写SDRAM的实例和SDRAM的相关文章及一些SDRAM控制器设计论文主要包括了:FPGA读写SDRAM的实例,SDRAM控制器核心介绍,系列SDRAM数据手册

2018-12-25 08:00:00 56

56 关键词:SDRAM , 嵌入式 , 时序控制 , 视频系统 在高速数字视频系统应用中,使用大容量存储器实现数据缓存是一个必不可少的环节。SDRAM就是经常用到的一种存储器。 但是,在主芯片

2019-02-10 00:12:01 220

220 在学习FPGA的过程中,注意是在学习过程中,联系FPGA的使用技巧,强烈建议尝试设计一个SDRAM控制器,不要使用IP核。

2019-02-15 15:04:01 766

766 ,SDRAM是非常流行的存储器。它们不像静态存储器那样容易控制,因此经常使用SDRAM控制器。 FPGA器件属于专用集成电路中的一种半定制电路,是可编程的逻辑列阵,能够有效的解决原有的器件门电路数较少的问题。FPGA的基本结构包括可编程输入输出单元,可配

2020-05-19 17:35:14 1833

1833

针对SDRAM 操作繁琐的问题,在对SDRAM 存储器和全页突发式操作进行研究的基础上,提出一种简易SDRAM 控制器的设计方法。该设计方法充分利用全页式高效率存取的优点,对SDRAM 进行配置、全页突发式读写时,操作方便。在实现sDRAM 的快速批量存储方面,具有良好的应用价值。

2020-12-18 16:13:18 6

6 SDRAM作为大容量存储器在高速图像处理中具有很大的应用价值。但由于SDRAM的结构和SRAM不同,其控制比较复杂。文章详细介绍了 SDRAM存储器的结构、接口信号和操作方法,以及 SDRAM控制器

2021-01-26 15:30:52 13

13 1.SDRAM使用越来越广泛。

2.SDRAM具有存储容量大,速率快的特点。

3.SDRAM对时序要求严格,需要不断刷新保持数据。

.FPGA在电子设计中的广泛应用,使用十分灵活利用FPGA来设计自己的 SDRAM控制器。

2021-03-05 14:49:00 10

10 本文首先分析了DDR SDRAM的基本特征,并提出了相应的解决方案详细介绍了基于J EDEC DDR SDRAM规范的DDR SDRAM控制器设计方案。该控制器采用Verilog HDL硬件描述语言实现,并集成到高性能SoC中。

2021-03-28 10:57:24 18

18 在FPGA视频图像处理系统中,经常需要使用到SDRAM作为视频图像缓存。SDRAM控制器可以分为上电初始化,自动刷新,读操作和写操作这四个部分,他们之间的转换可以通过状态机来控制。下面分别实现这几个部分。

2021-04-19 09:46:24 3459

3459

,SDRAM的控制逻辑复杂,使用很不方便。 为了解决这个矛盾,需要设计专用的SDRAM控制器,使系统用户象使用SRAM一样方便的使用SDRAM是十分必要的。考虑到控制器的通用性,本文提出了一种通用的SDRAM控制器的 Verilog设计,并给出了实现结果。 1 SDRAM的工作原理

2021-06-30 09:16:47 2346

2346

基于FPGA的DDR3SDRAM控制器设计及实现简介(arm嵌入式开发平台PB)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现简介资料,讲解的还不错,感兴趣的可以下载看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的SDRAM控制器的设计与实现简介(嵌入式开发工程师和基层公务员)-该文档为基于FPGA的SDRAM控制器的设计与实现简介文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 09:34:59 11

11 基于FPGA的DDR3SDRAM控制器设计及实现(嵌入式开发式入门)-该文档为基于FPGA的DDR3SDRAM控制器设计及实现总结文档,是一份很不错的参考资料,具有较高参考价值,感兴趣的可以下载看看………………

2021-07-30 13:07:09 35

35 (网盘)关于SDRAM和录音机等FPGA视频(android嵌入式开发教程)-关于SDRAM和录音机等FPGA视频,一步一步的讲解,真的很详细,适合大家自学研究。

2021-08-04 12:21:50 15

15 电子发烧友网站提供《基于FPGA的一种SDRAM控制器简易化设计方法.pdf》资料免费下载

2023-10-26 09:08:37 0

0 实时视频SDRAM控制器的FPGA设计与实现

2022-12-30 09:21:26 3

3

电子发烧友App

电子发烧友App

评论