电子发烧友网站提供《如何使用HLS加速FPGA上的FIR滤波器.zip》资料免费下载

2023-06-14 15:28:49 0

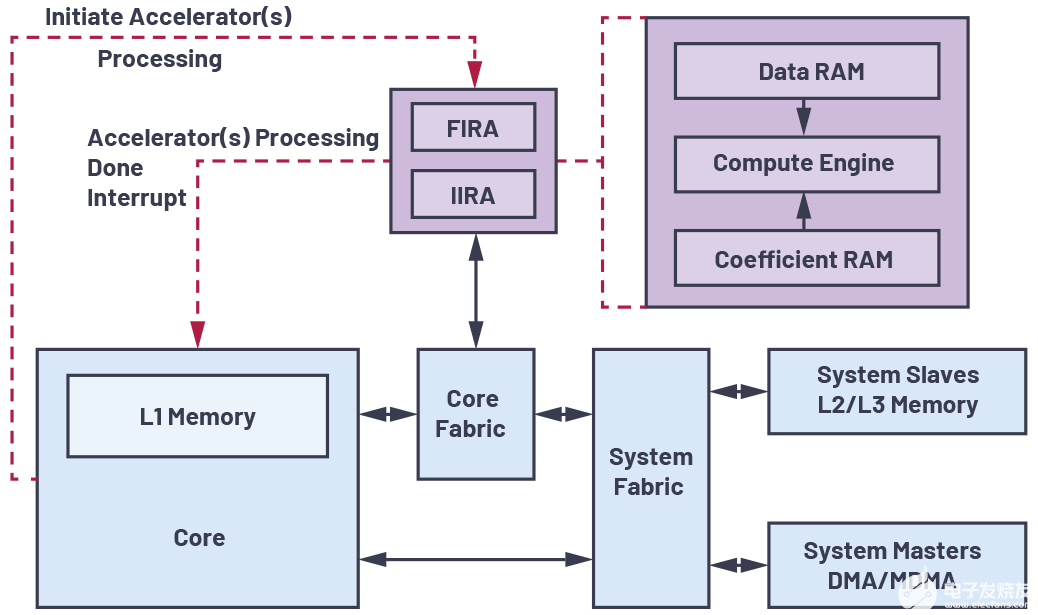

0 数字滤波器是数字信号处理中最常用的一种技术,可以对数字信号进行滤波、降噪、增强等处理,其中最常见的两种数字滤波器是IIR滤波器和FIR滤波器。本文将从IIR滤波器和FIR滤波器的原理、特点和应用等方面进行详细介绍,以便更好地理解两种滤波器的区别。

2023-06-03 10:21:43 6407

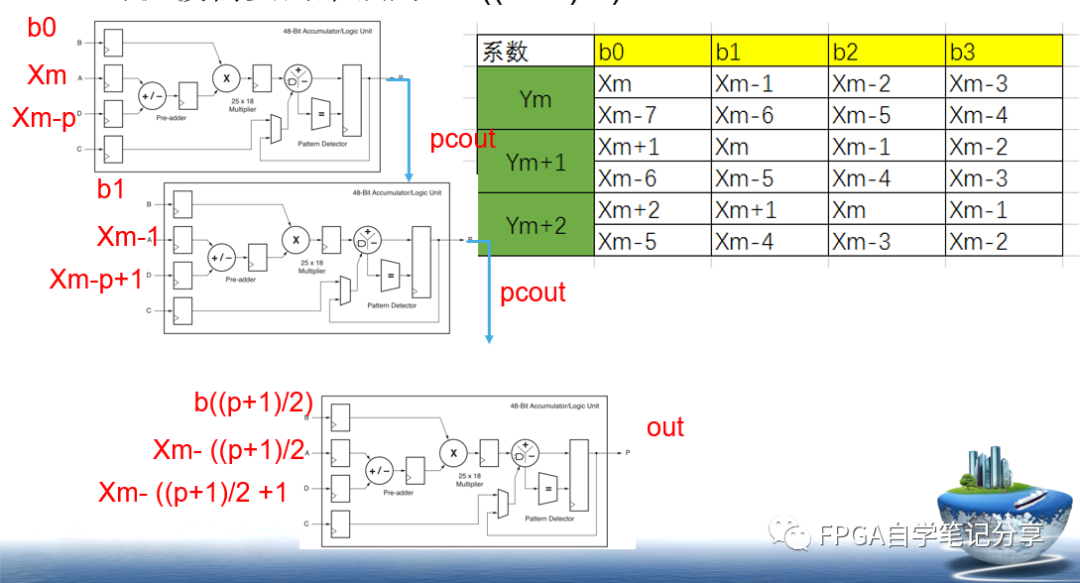

6407 上文 FPGA数字信号处理之滤波器2_使用dsp48e1的fir滤波器设计完成了结构设计。

2023-06-02 12:36:22 360

360

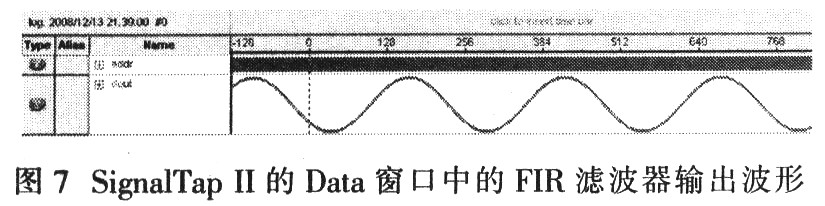

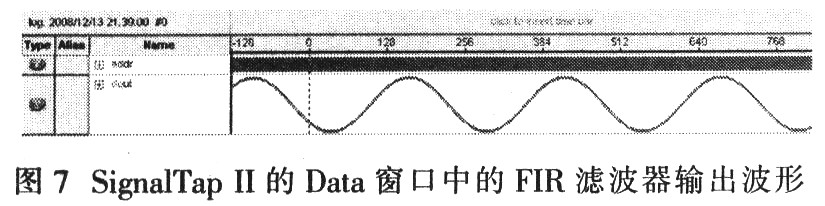

DSPBuilder设计了一个4阶FIR滤波器,并用QuartusII进行硬件仿真,仿真结果表明设计FIR滤波器的正确性。同时使用IPCore开发基于FPGA的FIR数字滤波器,利用现有的IPCore在FPGA器件上实现滤波器设计。

2012-08-11 15:32:34

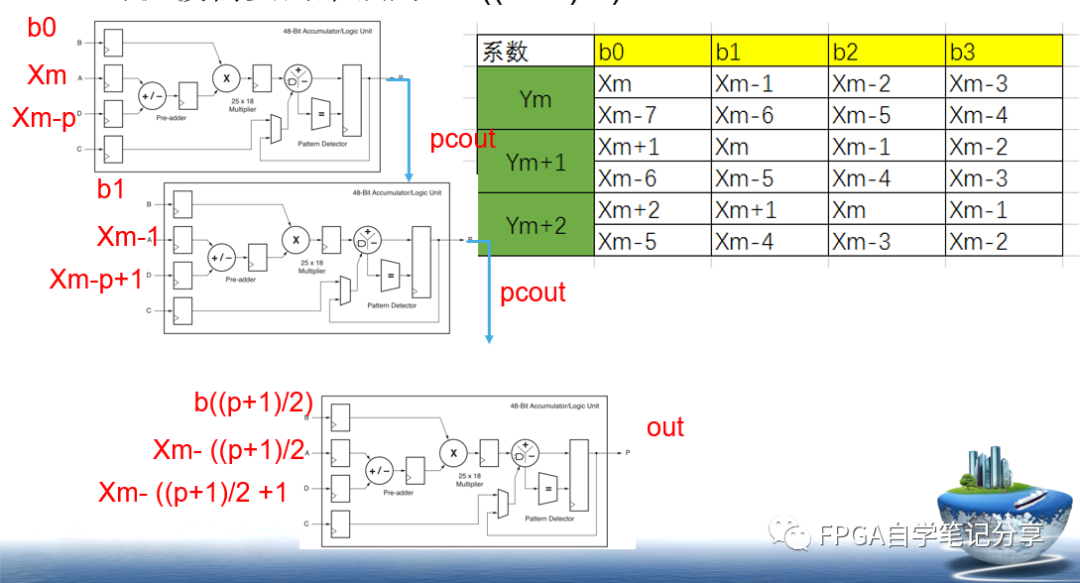

点击上方 蓝字 关注我们 本文将回顾对称 F IR 滤波器 的高效 FPGA 实现的注意事项。 本文将推导对称 FIR 滤波器的模块化流水线结构。我们将看到派生结构可以使用 Xilinx

2023-05-26 01:20:02 228

228

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的并行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了复现以及解读,并进行了仿真验证。

2023-05-24 10:57:36 331

331

本文介绍了设计滤波器的FPGA实现步骤,并结合杜勇老师的书籍中的串行FIR滤波器部分进行一步步实现硬件设计,对书中的架构做了简单的优化,并进行了仿真验证。

2023-05-24 10:56:34 343

343

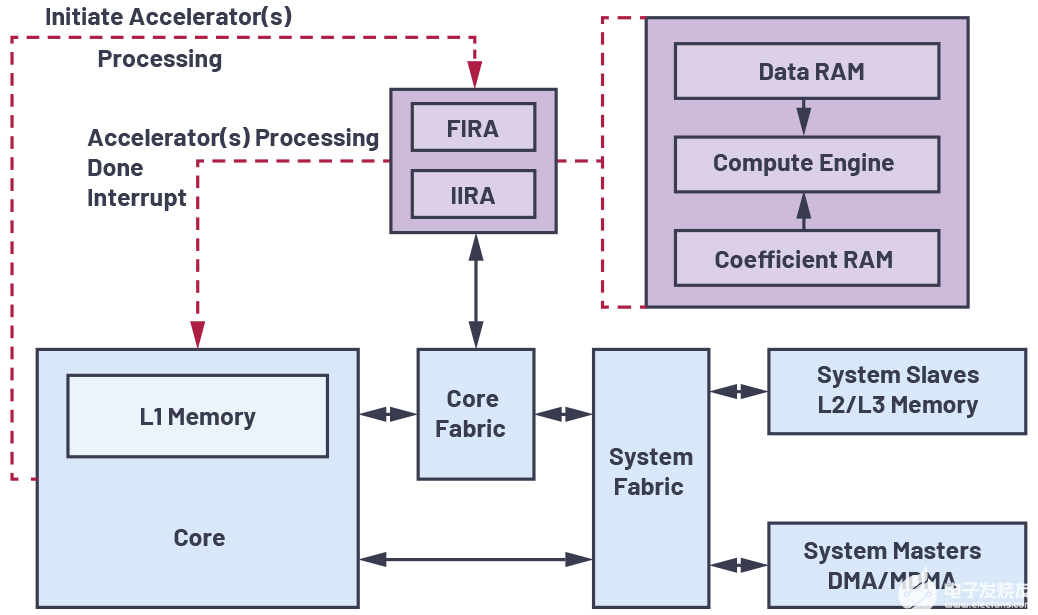

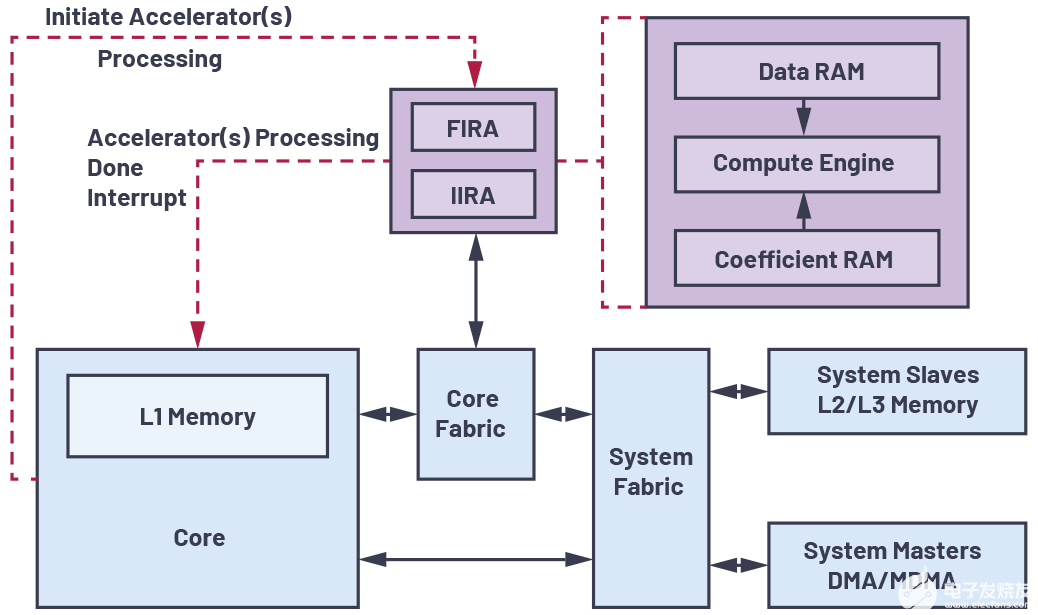

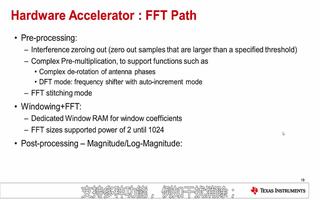

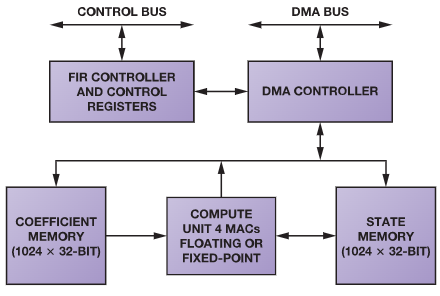

SHARC ADSP-2146x处理器集成了硬件加速器,可实现三种广泛使用的信号处理操作:FIR(有限脉冲响应)、IIR(无限脉冲响应)和FFT(快速傅里叶变换)。加速器卸载了核心处理器,并有可能使处理器的计算吞吐量增加一倍以上。本文以加速器在下一代音频系统中的应用为例。®

2023-03-03 14:46:51 458

458

借助硬件加速器开发您的设计

2023-01-03 09:45:15 384

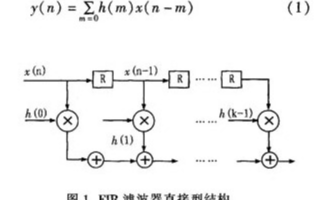

384 1.根据冲激响应的不同,将数字滤波器分为有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器。对于FIR滤波器,冲激响应在有限时间内衰减为零,其输出仅取决于当前和过去的输入信号值。对于IIR

2022-12-30 23:45:05 1347

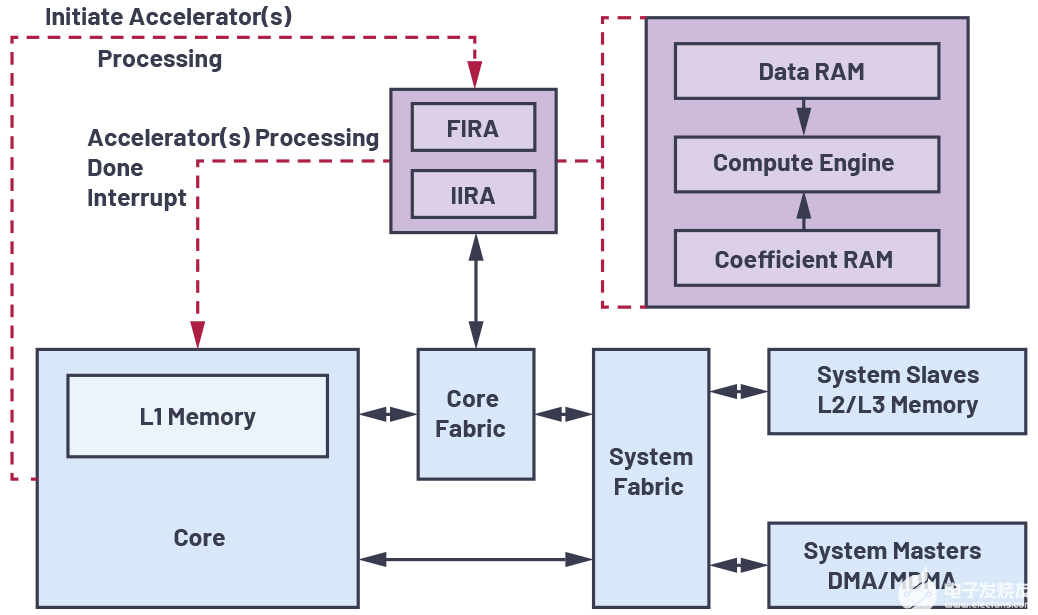

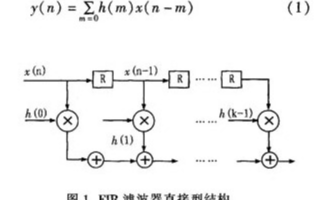

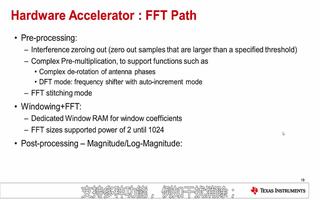

1347 处理器上的片上FIR和IIR硬件加速器(也称为FIRA和IIRA)可用于卸载FIR和IIR处理任务,从而腾出内核用于其他处理。在本文中,我们将讨论如何借助经过测试的实时示例说明的不同使用模型在实践中使用这些加速器。

2022-12-20 11:39:25 535

535

处理器上的片上FIR和IIR硬件加速器(也称为FIRA和IIRA)可用于卸载FIR和IIR处理任务,从而腾出内核用于其他处理。在本文中,我们将讨论如何借助经过测试的实时示例说明的不同使用模型在实践中使用这些加速器。

2022-12-20 11:22:36 575

575

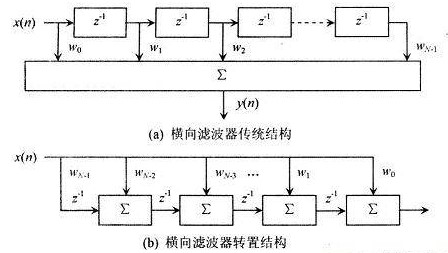

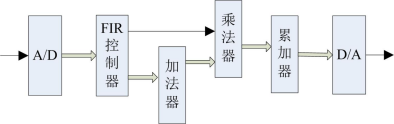

和移位操作。这些结构需要占用器件较多的LE(逻辑元件)资源,设计周期长,工作频率低,实时性差。本文提出一种基于Stratix系列FPGA器件的新的实时高速脉动FIR滤波器的快速实现方法。利 用FGPA集成的DSP(数字信号处理器)乘加模块定制卷积运算单元,利用VHDL(甚高速集成电路硬件描述

2022-12-01 10:20:05 482

482 当 AI 设计人员将硬件加速器整合到用于训练和推理应用的定制芯片中时,应考虑以下四个因素

2022-08-19 11:35:55 1125

1125

数字滤波器从实现结构上划分,有FIR和IIR两种。FIR的特点是:线性相位、消耗资源多;IIR的特点是:非线性相位、消耗资源少。由于FIR系统的线性相位特点,设计中绝大多数情况都采用FIR滤波器。

2022-04-24 14:40:16 2166

2166 OpenHarmony Dev-Board-SIG专场:OpenHarmony 新硬件加速器

2021-12-28 15:12:30 969

969

硬件加速器提升下一代SHARC处理器的性能

2021-04-23 13:06:32 6

6 提出一种新的高阶FIR滤波器的FPGA实现方法。该方法运用多相分解结构对高阶FIR滤波器进行降阶处理,采用改进的分布式算法来实现降阶后的FIR滤波器。设计了一系列阶数从8到1 024的FIR滤波器

2021-03-23 15:44:54 30

30 倍,其中L为并行的路数,并且运算延迟小。首先从理论上分析了基于多相滤波器的并行滤波原理,并以八路并行为例,对FIR滤波运算做了浮点仿真验证。然后用经典符号数表示以及优化定点滤波器系数,并针对滤波器系数设计了流水线结构。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 13

13 倍,其中L为并行的路数,并且运算延迟小。首先从理论上分析了基于多相滤波器的并行滤波原理,并以八路并行为例,对FIR滤波运算做了浮点仿真验证。然后用经典符号数表示以及优化定点滤波器系数,并针对滤波器系数设计了流水线结构。最后在Ahera的Stratix II系列芯片上

2021-01-28 17:22:00 7

7 用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2020-09-25 10:44:00 3

3 必要在性能和实现复杂性之间做出选择,也就是选择不同的滤波器实现结构。这里运用并行流水线结构来实现速度和硬件面积之间的互换和折衷。

2020-03-04 09:22:01 2800

2800

2.6 mmWave波形传感器简介1443硬件加速器

2019-05-08 06:20:00 2598

2598

。常系数FIR滤波器的系数固定不变,可根据其特点采用分布式算法进行设计,故实现起来速度快,消耗的资源少。变系数FIR滤波器的系数是不断变化的。当前含有变系数FIR滤波环节的芯片普遍存在速度与处理级数的矛盾,有效解决此问题具有重要的现实意义。

2019-04-22 08:07:00 4654

4654

本教程讨论基于Xilinx FPGA的Memcached硬件加速器的技术细节,该硬件加速器可为10G以太网端口提供线速Memcached服务。

2018-11-27 06:41:00 3259

3259 在数字信号处理中,数字滤波器的应用是极其广泛和重要的单元。与模拟滤波器相比,数字滤波器可以克服模拟滤波器所无法克服的电压漂移,温度漂移以及噪声等问题。数字滤波器根据冲击响应函数的特性,可以分为IIR滤波器和FIR滤波器两种。由于FIR滤波器只有零点、系统稳定等诸多优点。

2018-07-20 14:32:00 4898

4898

用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

2018-04-28 11:50:00 980

980

文介绍了FIR抽取滤波器的工作原理,重点阐述了用XC2V1000实现FIR抽取滤波器的方法,并给出了仿真波形和设计特点。

2018-04-19 11:34:00 1701

1701

很多人认为硬件加速器无非是一种速度更快的仿真器而已。毫无疑问,由于硬件加速器使用物理硬件进行仿真,使用硬件加速器验证复杂的集成电路和大型片上系统(SoC)能比软件仿真器快若干数量级。与仿真用通用计算机相比,仿真用单一功能计算机能提供更高容量、更高效的系统。

2018-03-28 14:50:00 3018

3018

设计时钟的速度运行相关设计。硬件加速器的运行速度则是每秒lM左右个时钟,因此可以将原始性能提高1000倍。原始性能相当于硬件加速器在无需等待验证平台或外部事件的条件下自由运行时的性能。 验证平台对硬件加速性能影响很大。

2018-03-05 10:13:13 3

3 本文针对快速、准确选择参数符合项目要求的滤波器设计方法的目的,通过系统的介绍有限脉冲响应( Finite Impulse Response,FIR)滤波器的原理、结构形式以及几种FIR滤波器设计方法

2017-12-21 14:53:14 14

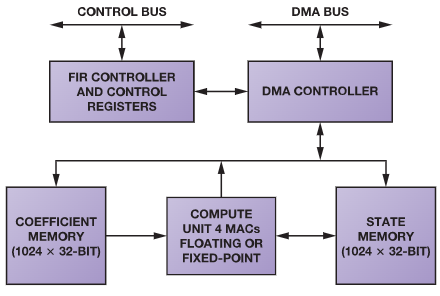

14 超过两倍。本文以下一代音频系统为例,说明硬件加速器在这方面的应用。 为什么使用硬件加速器 FIR滤波器、IIR滤波器和FFT操作在数字信号处理器中应用十分普遍,且具有规则的结构,因此可以用硬件直接实现,特别是用硬件加速器。硬件加速器是专用

2017-12-04 15:22:36 913

913 线性相位FIR滤波器的对称性减小了硬件规模;利用分割查找表的方法减小了存储空间;采用并行分布式算法结构和流水线技术提高了滤波器的速度,在FPGA上实现了该滤波器。

2017-11-24 15:17:27 2799

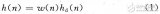

2799 针对传统的FIR 滤波器的缺点,介绍了一种基于FPGA 乘法器的FIR 滤波器设计方法,该滤波器利用FPGA 自带的18位乘法器MULT18 × 18SIO 进行乘法计算,利用寄存器对相乘结果进行

2017-11-22 07:39:45 2378

2378

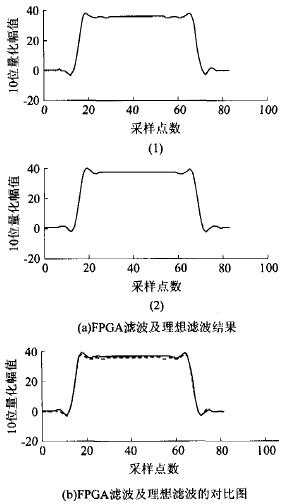

研究了一种采用FPGA实现32阶FIR滤波器硬件电路方案;讨论了窗函数的选择、滤波器的结构以及系数量化问题;研究了FIR滤波器的FPGA实现,各模块的设计以及如何优化硬件资源,提高运行速度等

2017-11-10 16:41:57 15

15 基于MATLAB与QUARTUS+II的FIR滤波器设计与验证

2017-09-18 10:17:37 11

11 数字滤波器广泛应用于硬件电路设计,在离散系统中尤为常见,一般可以分为FIR滤波器和IIR滤波器,那么他们有什么区别和联系呢。

2017-05-04 15:52:17 5712

5712

数字滤波器广泛应用于硬件电路设计,一般分为FIR滤波器和IIR滤波器。那么FIR滤波器和IIR滤波器有什么区别呢?本文通过几个例子做一个简单的总结。

2017-05-03 11:36:31 18

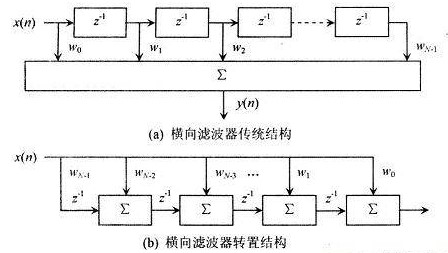

18 FIR滤波器,即有限脉冲响应滤波器,顾名思义,是指单位脉冲响应的长度是有限的滤波器。而根据FIR滤波器的结构形式,分为直接型、级联型、频率取样型和快速卷积型。其中直接型又可以采用串行结构、并行结构、分布式结构。本案例实现了具有线性相位的半串行结构的FIR滤波器。

2017-04-20 14:42:14 2095

2095 基于FPGA实现变采样率FIR滤波器的研究

2017-01-08 15:59:09 19

19 基于位并行DA结构的高速FIR滤波器_周云

2017-01-07 21:39:44 2

2 基于FPGA的FIR滤波器设计与实现,下来看看

2016-05-10 11:49:02 38

38 基于matlab和fpga的FIR滤波器设计,有兴趣的同学可以下载学习

2016-04-27 15:51:58 55

55 本文简要介绍了FIR数字滤波器的结构特点和基本原理,提出基于FPGA和DSP Builder的FIR数字滤波器的基本设计流程和实现方案。##FIR 数字滤波器的详细设计。

2014-07-24 15:30:05 8207

8207

FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。##脉动型(Systolic)FIR滤波器设计

2014-06-30 09:47:40 1723

1723 FIR 滤波器广泛应用于数字信号处理中,主要功能就是将不感兴趣的信号滤除,留下有用信号。##全并行FIR滤波器结构

2014-06-27 10:02:56 7800

7800 在数字滤波器中,FIR滤波器是一种结构简单且总是稳定的滤波器,同时也只有FIR滤波器拥有线性相位的特性。传统的直接型滤波器运算速度过慢,而改进型的DA结构的滤波器需要过高的

2013-08-07 19:04:56 36

36 描述了基于FPGA的FIR滤波器设计。根据FIR的原理及严格线性相位滤波器具有偶对称的性质给出了FIR滤波器的4种结构,即直接乘加结构、乘法器复用结构、乘累加结构、DA算法。在本文中给

2012-11-09 17:32:37 121

121 数字滤波器是数字信号处理领域内的重要组成部分。FIR滤波器又以其严格的线性相位及稳定性高等特性被广泛应用。本文结合MATLAB工具软件介绍了FIR数字滤波器的设计方法,并在Xilinx的

2012-09-25 11:34:08 120

120 针对复杂算法中矩阵运算量大, 计算复杂, 耗时多, 制约算法在线计算性能的问题, 从硬件实现角度, 研究基于FPGA/Nios-Ⅱ的矩阵运算硬件加速器设计, 实现矩阵并行计算。首先根据矩阵运算

2011-12-06 17:30:41 89

89 目前数字滤波器的硬件实现方法通常采用专用DSP芯片或FPGA,本文从FIR滤波器的系数考虑,采用CSD编码,对FIR数字滤波器进行优化设计。

2011-08-16 10:54:41 3448

3448

充分利用有限冲击响应数字滤波器(Finite Impulse Response digital filter ,FIR)系数的对称特性,借助于MATLAB语言和现场可编程门阵列(FPGA)实现了一种高效的 低通滤波器 。设计过程中通过

2011-08-05 14:23:07 82

82 基于流水线技术,利用FPGA进行并行可重复配置高精度的 FIR滤波器 设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用这种FIR滤波器的设计方法可以充分发挥FPGA的优势。

2011-07-18 17:09:28 63

63 本文通过改变通常FIR处理结构,有效地节省了资源,只使用了一套乘加器,一套FIR滤波器结构,就完成了两套FIR滤波器的功能,

2011-05-13 09:32:32 4050

4050

分析了FIR数字滤波器的基本原理,在MATLAB环境下利用窗函数设计FIR低通滤波器,实现了FIR低通滤波器的设计仿真。将设计的符合要求的滤波器在TI公司DSPTMS320LF2407A上实现。通过

2009-12-18 15:53:56 101

101 :FIR 数字滤波器由于具有诸多优点,因而在数字信号处理中得到了十分广泛的应用。介绍了MATLAB 环境下FIR 数字滤波器的设计、仿真和基于TMS320VC5416DSP 硬件平台的实现。详细描述

2009-12-16 13:31:22 58

58 基于MATLAB与QUARTUS II的FIR滤波器设计与验证

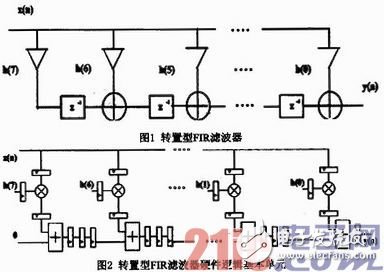

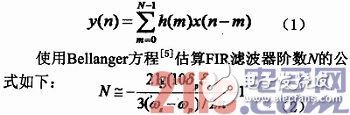

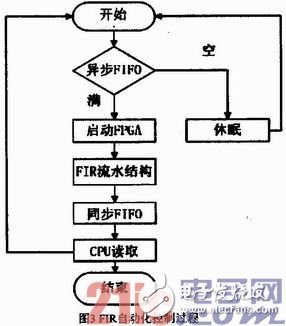

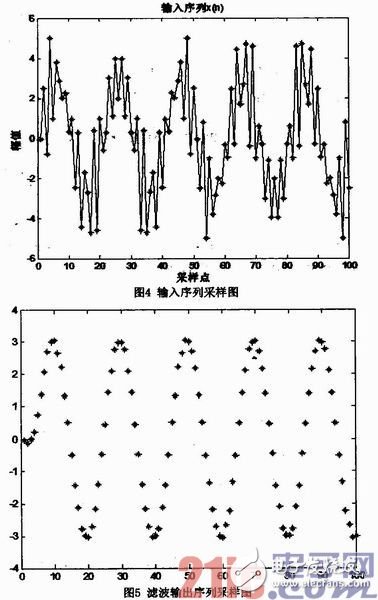

1 引言 FIR数字滤波器能够满足滤波器对幅度和相位特性的严格要求,避免模拟滤波器的温漂和噪声等问题,

2009-12-12 11:23:42 2317

2317

本文综合介绍了基于FPGA 软件Quartus II 和MATLAB 的FIR 滤波器的设计仿真,将两大软件综合运用后大大缩减了设计研发的时间,在算法结构上利用了流水线等优化方式。

2009-11-30 14:21:09 117

117 FIR带通滤波器的FPGA实现

引 言 在FPGA应用中,比较广泛而基础的就是数字滤波器。根据其单位冲激响应函数的时域特性可分为无限冲击响应(Infinite

2009-11-13 09:55:18 6439

6439

基于FPGA对称型FIR滤波器的设计与实现:在基于FPGA的对称型FIR数字滤波器设计中,为了提高速度和运行效率,提出了使用线性I相位结构和加法树乘法器的方法,并利用Altera公I司的FPG

2009-09-25 15:38:38 30

30 本文提出了一种采用现场可编程门阵列器件 FPGA 实现FIR 字滤波器硬件电路的方案,该方案基于只读存储器ROM 查找表的分布式算法。并以一个十六阶低通FIR 数字滤波电路在ALTERA 公

2009-08-31 16:47:47 44

44 摘要: 针对在FPGA中实现FIR滤波器的关键--乘法运算的高效实现进行了研究,给了了将乘法化为查表的DA算法,并采用这一算法设计了FIR滤波器。通过FPGA仿零点验证

2009-06-20 14:09:36 646

646

摘要: 提出了一种采用现场可编码门阵列器件(FPGA)并利用窗函数法实现线性FIR数字滤波器的设计方案,并以一个十六阶低通FIR数字滤波器电路的实现

2009-06-20 14:05:46 952

952

如何用用FPGA实现FIR滤波器

你接到要求用FPGA实现FIR滤波器的任务时,也许会想起在学校里所学的FIR基础知识,但是下一步该做什么呢?哪些参数是重

2009-03-30 12:25:45 4408

4408

基于流水线技术的并行高效FIR滤波器设计

基于流水线技术,利用FPGA进行并行可重复配置高精度的FIR滤波器设计。使用VHDL可以很方便地改变滤波器的系数和阶数。在DSP中采用

2009-03-28 15:12:27 714

714

高效FIR滤波器的设计与仿真-基于FPGA

摘要:该文在介绍有限冲激响应(FIR)数字滤波器理论及常见实现方法的基础上,提出了一种基于FPGA的高效实现方案。

2008-01-16 09:56:02 1373

1373

电子发烧友App

电子发烧友App

评论