声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

asic

+关注

关注

34文章

1154浏览量

119259 -

赛灵思

+关注

关注

32文章

1794浏览量

130515 -

时钟

+关注

关注

10文章

1479浏览量

130304

发布评论请先 登录

相关推荐

UltraScale系列与7系列FPGA的差异

已从该架构中移除BUFMRs、BUFRs、BUFIOs及其相关的路由资源,并被新的时钟缓冲器、时钟路由和全新的I/O时钟架构所取代。

1.25G突发时钟数据恢复/ UltraScale中的2.5G PON应用设备总结

电子发烧友网站提供《1.25G突发时钟数据恢复/ UltraScale中的2.5G PON应用设备总结.pdf》资料免费下载

发表于 01-14 09:56

•0次下载

针对UltraScale/UltraScale+芯片DFX应考虑的因素有哪些(2)

UltraScale/UltraScale+芯片开始支持BUFG_*、PLL和MMCM出现在动态区,在7系列FPGA中这些时钟资源只能在静态区。

AD9208使用过程中有fs/4干扰点的问题如何解决?

我目前在使用AD9208,时钟架构是100MHz作为参考时钟,由LMX2595锁出需要的时钟频率,再由HMC7043产生采样时钟fs和SYSREF供给ADC,同时产生DCLK供给FPG

发表于 12-01 07:50

虹科干货 | 适用于基于FPGA的网络设备的IEEE 1588透明时钟架构

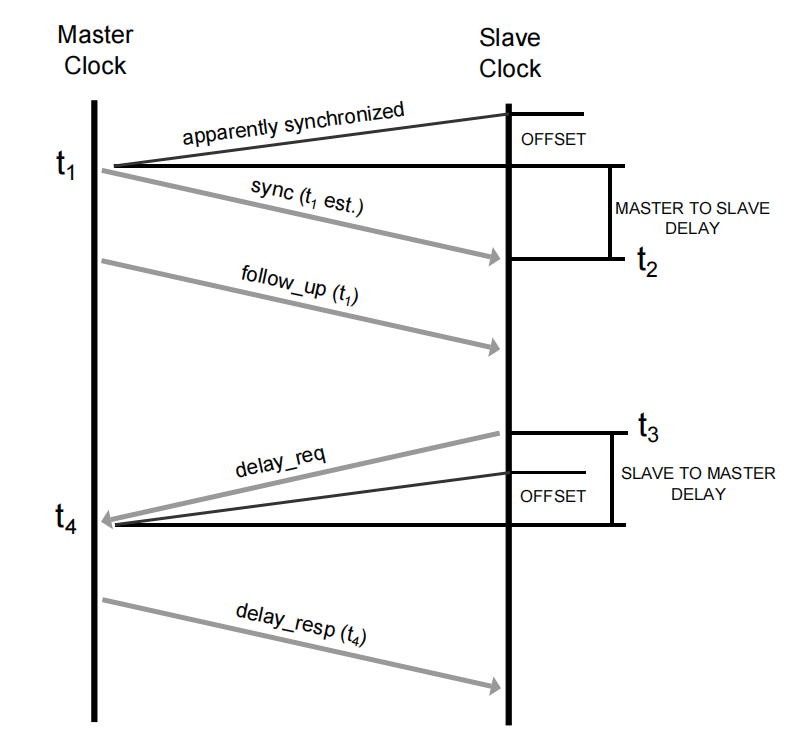

的IEEE 1588透明时钟(TC)架构,帮助您实现精确时间同步和高效通信。 在分布式系统中,传感器/执行器的事件和操作需要进行精确的时间协调,因为时钟差异可能导致操作失败。为了确保时间同步,每个组件都需要具备与其对等组件一致的

适用于基于FPGA的网络设备的IEEE 1588透明时钟架构

的IEEE1588透明时钟(TC)架构,帮助您实现精确时间同步和高效通信。在分布式系统中,传感器/执行器的事件和操作需要进行精确的时间协调,因为时钟差异可能导致操作失败。

使用UltraScale和UltraScale+FPGA开发防篡改设计

电子发烧友网站提供《使用UltraScale和UltraScale+FPGA开发防篡改设计.pdf》资料免费下载

发表于 09-13 15:32

•0次下载

FPGA设计中动态时钟的使用方法

时钟是每个 FPGA 设计的核心。如果我们正确地设计时钟架构、没有 CDC 问题并正确进行约束设计,就可以减少与工具斗争的时间。

发表于 07-12 11:17

•845次阅读

什么是ASIC?ASIC中的“特定应用”是什么意思?

没有关于 ASIC 确切含义的官方声明,而且许多电子专业人士可能并不总是就 ASIC 到底是什么或特定组件是否应归类为 ASIC 达成一致。

发表于 06-15 09:41

•395次阅读

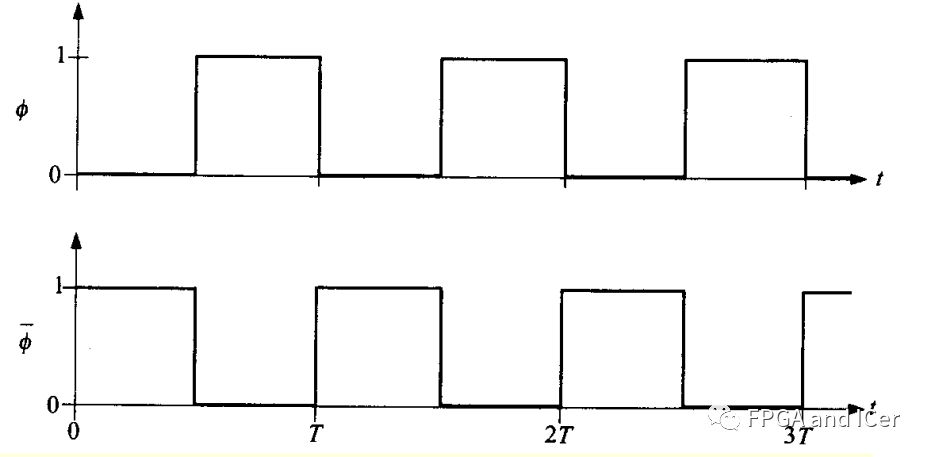

谈谈非理想时钟的时钟偏差

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,时钟信号的好坏很大程度上影响了整个系统的稳定性,本文主要介绍了数字设计中的非理想时钟

MEMS时钟解决方案创新者Stathera宣布A轮募资达1500万美元

“在同步下一代电子产品方面,使用传统时钟架构的技术扩展遇到了瓶颈。Stathera的技术引入了一种集成和制造时钟器件的新方法。”Stathera首席执行官(CEO)兼联合创始人George Xereas表示,“我们很高兴成为唯一一家拥有最先进DualMode频率技术的公司

新UltraScale ASIC时钟架构的使用及好处

新UltraScale ASIC时钟架构的使用及好处

评论