关于层叠和阻抗设计,设计师需要经历的几个阶段

1.小白级:刚接触PCB设计的时候,可能所涉及的产品非常简单不属于高速的范畴,完全不需要控制阻抗,把线拉通就完事了,运气好点的工程师刚涉及PCB设计的时候就能接触高速的产品,但是却不知道要控制阻抗,导致设计出问题;

2.初级:经过一段时间的PCB设计,慢慢了解到阻抗相关的一些概念,具备了高速电路的一些基本知识,知道了控制阻抗的必要性,但是缺乏PCB材料和工艺制程以及阻抗计算相关的一些知识,对阻抗的认识还不是很深,只知道控阻抗需要提供阻抗需求表给板厂给板厂来控。

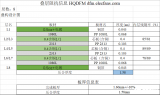

3.中级:在PCB设计上有一定的经验,知道影响阻抗的各种参数,会用Si9000选择相应的阻抗模型进行阻抗计算,但是对板材和工艺方面的知识欠缺,觉得自己计算阻抗和设计层叠比较繁琐,并且就算在设计阶段做了阻抗计算到了板厂还是要调整,所以还是提供一份阻抗需求表,文字加图片的说明方式让板厂来控。

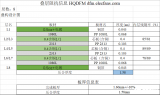

4.高级:对高速PCB设计的有很深的认识,对板厂的加工流程,板材的相关特性及数据有一定的了解,会提供详细的层叠阻抗设计表格,指明层叠顺序的同时,把各层的大致厚度都标注出来,板厂虽然最后一定会调整,但是会在我们指定范围之内做微调。

这个问题你可以回答的诚实一点:)

段位低,找大腿?

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:你的层叠和阻抗什么段位?

文章出处:【微信号:PCBTech,微信公众号:EDA设计智汇馆】欢迎添加关注!文章转载请注明出处。

相关推荐

Sora短期不会向公众开放 还处于反馈获取阶段 据外媒报道Sora核心团队在一次采访中透露,Sora短期不会向公众开放,Sora大模型目前还处于反馈获取阶段,还不是一个完善产品;还需要

![的头像]() 发表于

发表于 03-14 14:55

•375次阅读

为什么输电线路的正序阻抗比零序阻抗小呢? 输电线路的正序阻抗比零序阻抗小是由于以下几个原因: 首先,输电线路的正序阻抗在设计和施工过程中通常

![的头像]() 发表于

发表于 02-18 11:41

•542次阅读

阻抗,工程师们都接触过,但能把阻抗说清楚的工程师少之又少。阻抗看似简单,实则难以言表。下面我们用快问快答的方式,轻松帮你搞懂阻抗!01问:什么是阻抗

![的头像]() 发表于

发表于 01-05 10:44

•467次阅读

阻抗,工程师们都接触过,但能把阻抗说清楚的工程师少之又少。阻抗看似简单,实则难以言表。 下面我们用快问快答的方式,轻松帮你搞懂阻抗! 0 1 问:什么是

![的头像]() 发表于

发表于 01-03 08:40

•606次阅读

板1.6mm厚度叠层与阻抗设计

在10层1阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。

建议层叠为TOP-Signal/Gnd-Gnd

发表于 12-25 13:48

板1.6mm厚度叠层与阻抗设计

在10层1阶板叠层设计中,顶层信号L1的参考平面为L2,底层信号L10的参考平面为L9。

建议层叠为TOP-Signal/Gnd-Gnd

发表于 12-25 13:46

PCB层叠设计是什么?又有什么样的作用? PCB层叠设计又称为PCB层压设计,是指在印刷电路板的设计过程中,通过合理地选择不同层之间的层间结构和层间材料,以及设计每层的布线、焊盘和电源分布等布局

![的头像]() 发表于

发表于 12-21 13:49

•447次阅读

什么是阻抗匹配?影响阻抗的因素? 阻抗匹配是在电子电路中为了提高功率传输效率而进行的一种电性特性调整方法。当能量从一个电路传输到另一个电路时,如果两个电路之间的阻抗不匹配,就会发生功

![的头像]() 发表于

发表于 12-21 11:31

•702次阅读

确定多层PCB板的层叠结构需要考虑较多的因素。从布线方面来说,层数越多越利于布线,但是制板成本和难度也会随之增加。对于生产厂家来说,层叠结构对称与否是PCB板制造时需要关注的焦点,所以层数的选择需要考虑各方面的需求,以达到的平衡。

发表于 11-22 15:29

•361次阅读

的事情,是差一二十欧姆哦!

所以说,遇到这种旁边也是信号线的场景,你自己的阻抗就由不得你说了算了,你自己是多少欧姆的阻抗就很看旁边走线的“

发表于 11-02 14:00

Rigid-Flex刚柔电路的三大特征是 Multi-bending(多弯曲),Multi-stackup(多层叠),Multi-zone(多区域)。

![的头像]() 发表于

发表于 10-07 17:17

•973次阅读

8层通孔板1.6mm厚度叠层与阻抗设计 在8层通孔板叠层设计中,顶层信号 L1 的参考平面为 L2,底层信号 L8 的参考平面为 L7。 建议层叠

![的头像]() 发表于

发表于 08-21 17:16

•1304次阅读

国星光电(002449.sz) 7月18日在投资者互动平台上表示,公司财务状况稳定,经营现金流动状况良好,融资储备手段多样。目前重组事项仍处于计划阶段,存在较大的不确定性,公司应根据交易事项的进展情况,分阶段及时履行信息公开义务

![的头像]() 发表于

发表于 07-19 10:21

•400次阅读

阻抗匹配主要用于传输线上,以此来达到所有高频的微波信号均能传递至负载点的目的,而且几乎不会有信号反射回来源点,从而提升能源效益。信号源内阻与所接传输线的特性阻抗大小相等且相位相同,或传输线的特性阻抗与所接负载

![的头像]() 发表于

发表于 07-04 14:38

•5522次阅读

问什么是阻抗?答在具有电阻、电感和电容的电路里,对电路中的电流所起的阻碍作用叫做阻抗。问什么是阻抗匹配?答阻抗匹配是指信号源或者传输线跟负载之间达到一种适合的搭配。

![的头像]() 发表于

发表于 04-28 11:36

•1.1w次阅读

你处于层叠和阻抗设计的什么阶段?

你处于层叠和阻抗设计的什么阶段?

评论