为了实现测量数据的实时显示,电子测量系统常用到二-十进制(BCD)转码器来完成数据的实时转换。目前,电子系统中的二-十进制(BCD)数制转换有三类实现方法,一是采用软件算法的实现方式,传统的方法是用DAA调节指令实现,但效率较低;其次是纯硬件运算实现方式,这种实现方式从数据转换运算到硬件的直接映射,常采用逻辑运算和数据移位来实现数据转换,转换效率较高,但是在转换数据位数较多时,运算量会显著增加,硬件实现代价也较大;三是基于数据查找表LUT(Lookup Table)的实现方式。

本文提出了一个高效、易于重构的二-十进制(BCD)转码器设计方案,并在FPGA开发板上成功地进行了设计验证。

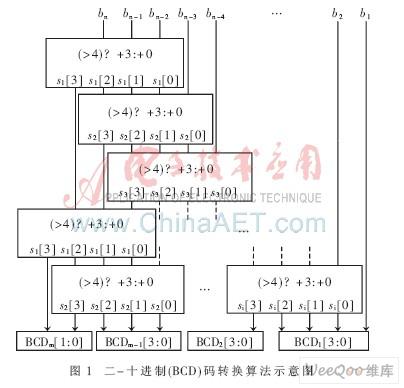

1 二-十进制(BCD)码的转换算法

从以上的二-十进制(BCD)码变换算法中可以看到,二进制数据的最低位b1不需要转换而直接输出,而且每个转换运算单元的低3位输出数据始终不会大于(4)D/(100)B,这样就能够保证最后得到的每一位BCD码不会大于(9)D/(1001)B,从而得到BCD码的正确转换输出。

2 二-十进制(BCD)转码器的实现

2.1 二-十进制(BCD)转码器的ASIC实现

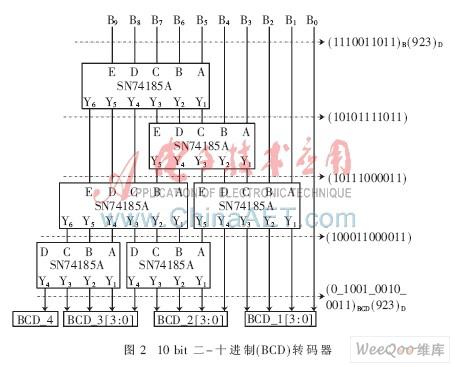

首先,构造出5 bit二进制数的转换单元,然后再以此转换单元为基本单位扩展成其他的多位二-十进制(BCD)转码器,TI公司的SN74185A芯片就是这样的一个5 bit数据转换单元,用它实现的10 bit二-十进制(BCD)码转换器如图2所示。

图2所示的转码器与图1的结构区别在于采用了5 bit的转换单元而不是4 bit的基本单元(高3 bit转换单元的最高位输入接地),从而简化了多位转码器的电路结构。每个转换单元(SN74185A)的6个输出位权依次是(20、10、5、4、2、1),因此也保证了每个转换运算单元的低3位输出数据始终不会大于(4)D/(100)B,使最后得到的每位BCD码都不会大于(9)D/(1001)B。使用时要求转换单元(SN74185A)的无用输入端作接地处理。假如需要转换的10 bit数据是(1110011011)B,每个转换模块完成输入二进制数据的位权转换,如图2所示,经过第一层数据转换后得到(10101111011),再依次经过后面第2层至第4层的数据转换,得到各层次相应转换输出分别是:(10111000011)、(100011000011)、(0100100100011),第4层的转换输出就是十进制(BCD)码:(0100100100011)BCD=(923)D。

2.2 基于FPGA的二-十进制(BCD)转码器设计

在片上数字系统(SOPC)中实现二-十进制(BCD)码转换器,如果直接依据图2所示的结构,使用SN74185A芯片的IP核(Quartus II工具提供)来实现转码器不但存在着2.1中所述的不足之处,而且还会面临着更大的硬件资源浪费问题,这是由于FPGA中的逻辑单元(LEs)都是基于4输入的数据查找表(LUT),如果要实现5输入的转换单元(SN74185A),就需要查找表级联扩展,从而会造成路径延迟进一步增大、逻辑单元利用率降低、硬件实现代价提高。

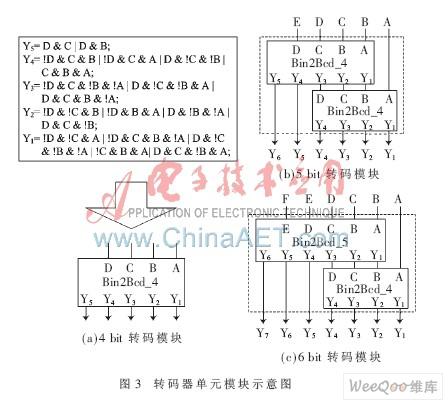

为了克服以上的转码器设计缺陷,针对FPGA的结构特点,提出了以下设计思路:(1)以4 bit数据转换作为基本的转换单元来适应FPGA结构特点,而提高逻辑单元利用率,达到降低硬件代价的目的;(2)利用Verilog HDL层次化设计描述的灵活性,以4 bit数据转换单元为最底层模块,构造出更大的5 bit和6 bit转换单元(模块)。这种设计方法为二-十进制(BCD)转码器的构建提供了4 bit、5 bit和6 bit三种不同大小的单元模块,可使每一个转换单元模块的使用恰到好处(需要小模块的地方就不会使用大模块)。

2.2.1 二-十进制(BCD)转码器单元模块设计

采用上文所述基于FPGA的二-十进制(BCD)转码器设计方案,关键在于要做好最底层模块(4 bit转码模块)的优化设计,对4 bit转码模块的不同Verilog HDL描述方式也会带来不同的实现代价;本文使用结构描述实现4 bit转码模块(Bin2Bcd_4),再通过4 bit转码模块层次实例化构成5 bit转码模块(Bin2Bcd_5)和6 bit转码模块(Bin2Bcd_6)的设计,4 bit、5 bit和6 bit三种单元模块的构造示意图如图3所示。

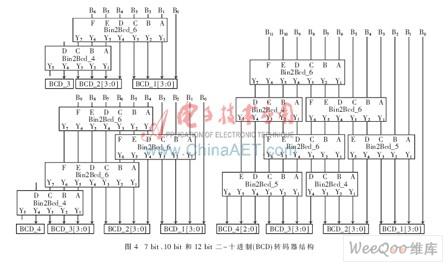

2.2.2 基于混合模块的二-十进制(BCD)转码器设计

根据二-十进制(BCD)转码算法,使用上文2.2.1中得到的4 bit、5 bit和6 bit三种二-十进制转码单元模块,构造出7 bit、10 bit和12 bit二-十进制(BCD)转码器结构,如图4所示,转码单元模块的多余输入端接地,多余输出端悬空。

3 二-十进制(BCD)转码器的设计验证

本文使用Quartus II 6.0(Full Version)开发工具,对于图4所示的3个混合模块构建的二-十进制(BCD)转码器,在Altera公司的FPGA(Altera EP1K30QC208-2)芯片上分别进行了设计验证,验证结果完全达到设计预期。其中12 bit二-十进制(BCD)转码器的功能仿真和时序仿真结果如图5所示。

在完全相同的软硬件验证环境下,把图4所示的转码器设计和使用中规模集成电路IP核(SN74185A)实现的7 bit、10 bit和12 bit的转码器进行了性能对比,验证结果进一步表明了这种采用混合模块构建二-十进制(BCD)转码器的行之有效性;表1所示为采用这两种构建方法得到的7 bit、10 bit和12 bit转码器的验证结果对比。

Altera EP1K30QC208-2(FPGA)芯片上的7 bit、10 bit和12 bit转码器设计验证结果和使用IP核(SN74185A)实现的转码器验证结果对比更加充分证明了这种设计思路的可行性;这种高效、易于重构的二-十进制(BCD)转码器设计为基于FPGA的片上数字测量系统实现做出了有意义的积极探索。

-

FPGA

+关注

关注

1602文章

21320浏览量

593158 -

芯片

+关注

关注

447文章

47788浏览量

409098 -

BCD

+关注

关注

1文章

82浏览量

29281

发布评论请先 登录

相关推荐

在FPGA开发板实现二-十进制转码器设计

在FPGA开发板实现二-十进制转码器设计

评论