在电子产品的设计中,经常存在断电后数据或机器参数的保存问题。早期一般由电池为RAM供电,但由于环境及电池本身的原因,这种方式常使数据丢失。目前,小容量数据存储多采用93系列EEPROM(如93C46)或24系列EEPROM(如24C45)。但如果要求存储的数据量很大?这些芯片的存储能力就不能胜任。为此,本文介绍一种大容量的闪烁存储器芯片AT45D081,并给出其在税控加油机中的应用。

1、AT45D081简介

1.1 AT45D081的特点

AT45D081A是ATMEL公司生产的闪烁存储器。它采用串行方式传送数据, 符合ISO7816标准,时钟频率可高达15MHz, 并采用单5V电源供电。同时具有功耗低、体积小、容量大、传送快速, 与CMOS和TTL电平兼容以及掉电后数据不丢失等特点。 由于读写时序与SPI模式0与模式3兼容, 因此,其硬件设计与软件编程都很容易。

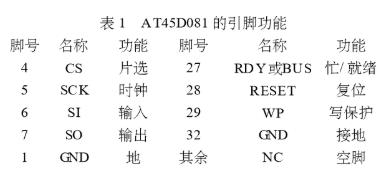

1.2 内部结构与引脚说明

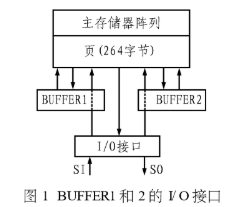

AT45D081内部由主存储器阵列、两个SRAM数据缓冲区BUFFER1、BUFFER2以及I/0接口组成。其中主存储器阵列容量为8M Bits,由4096页组成,每页264字节,为编程方便又把连续的8页定义为一块。每个SRAM数据缓冲区大小为264字节。 这两个缓冲区可在主存储器阵列访问某一缓冲区或某缓冲区访问主存储器阵列时,另外一个缓冲区能同时与外部交换数据。主存储器与缓冲区的相互访问是在芯片内部自动完成的,且不需要外部的干涉,这样就大大提高了外部访问的效率。但外部可以通过读取芯片提供的只读状态存储器的内容知道芯片容量及工作状态信息(可用就绪/忙标志指示缓冲区是否与指定的主存储器阵列页内容一致)。

AT45D081的主要引脚功能见表1所列。当AT45D081的CS由高变低时,芯片启动一次操作,而当CS由低变高时,终止操作。这时SI上的任何数据都被忽略,SO处于高阻态。 当WP为低时,主存储器的前256页不能被访问。如果要访问前256页,则必须使WP为高。WP已被芯片内部拉高,如果要对前256页编程,那么,WP应在外部置高电平。

1.3 操作指令及读写时序

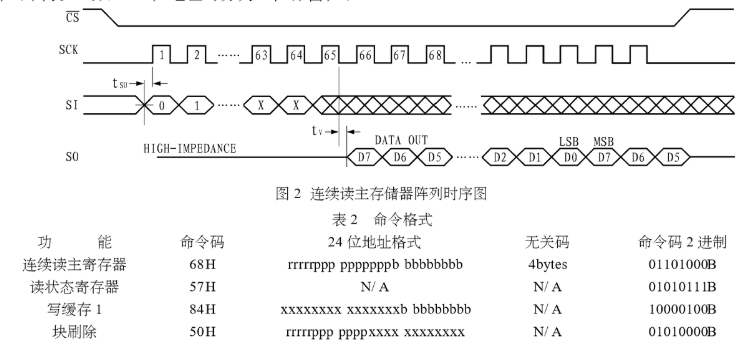

外部访问主存储器阵列和缓冲区及状态寄存器是通过输入命令来实现的。AT45D081共提供了26条命令?这些命令按功能可分为读主存储器阵列页、主存储器阵列页内容传送到缓冲区、缓冲区内容传送到主存储阵列页、页擦除、块擦除、外部通过缓冲区对主存储器页写入、自动页重写?缓冲区读写?状态寄存器读等。所有的命令都遵循下面的格式?首先是8位命令码?然后是24位地址码?有的命令后面还要输入无关码。输入时高位在前?低位在后。输入模式与SPI模式0与模式3兼容。表2所列是连续读主存储阵列、读状态寄存器和写缓冲区命令格式。表中:r代表该位为保留位,p表示该位为页地址位,b表示该位为页内字节地址位,x表示该位可以为0也可以为1,N/A表示输入数据流中没有这些位,由表2可知:24位地址可分为5位保留位, 7位块地址,10位页地址和9位页内字节地址。对于主寄存器阵列,页内字节的访问,如连续读主寄存器阵列,必须指定页及页内地址作为访问的首地址。同时还需注意,该命令24位地址后还有32位无关位输入。而对于缓冲区的访问?因缓冲区的大小为264字节,因此指定9位地址就可以了。此外,在块的擦除方面,由于是整块操作,所以,只需指定7位块地址而无需指定其它地址。

图2所示是连续读主寄存器阵列的时序。从时序图可看出,当CS为高电平时,SI输入的位流无效,此时,SO处于高阻态。当CS由高到低时,片选有效,此时将启动操作命令,在时钟SCK的上升沿把SI上已备好的数据串行送入芯片(高位在前)。对于连续读主存储器阵列命令,其输入命令格式位流为:

01101000 rrrrrppp pppppppb bbbbbbbb xxxxxxxx xxxxxxxx xxxxxxxx xxxxxxxx ,共64位。当第65个时钟到来时?SO由高阻态变为有效状态而输出数据,数据输出也是高位在前。

2、AT45D081在税控加油机中的应用

2.1 税控加油机对存储器的要求

税控加油机是对车辆、油罐等设备进行加油并进行税务管理的加油机器。为对加油过程进行有效监督管理,税控加油机必须达到国家要求的加油精度,并应显示每次加油的油价、加油量及加油金额,同时税控加油机也必须能够存储7年之内每天的加油记录,并提供查询接口。

为了满足税控加油机对数据存储的要求,存储器必须提供足够大的存储空间,且在掉电时不能丢失数据。同时应有较强的防数据误写功能以保证存储在存储器中税务数据的安全。基于多方面考虑?设计中选用了AT45D081。

2.2 税控加油机的功能结构

税控加油机主要由税控CPU、主控CPU以及其它一些外围设备组成。税控CPU和主控CPU之间是通过模拟的SPI总线来通信的。主控CPU通过SKH向税控CPU请求通信,税控CPU通过SKL作应答。通信数据先由一方放到双端口移位缓存中,然后通知对方到缓存中取数据。加油的工作过程如下,主控CPU检测到提油枪信号后将向税控CPU发出加油请求。如果税控CPU允许加油,则一方面使能电机控制输入端A,同时通知主控CPU,主控CPU接到通知后,立即使能电机控制端B,同时计算加油数据并通过SPI协议总线传送到税控CPU,再由税控CPU驱动显示。当主CPU检测到油枪挂起后,它一方面送出关电机信号,另一方面通知税控CPU也送出关机信号。当然,主控CPU也可以通过键盘向税控CPU查询时间及其它信息。

2.3 提高可靠性的设计措施

加油的数据由税控CPU保存在AT45D081中。为提高芯片的抗干扰能力,防止程序对芯片的误写,有效保护片内数据。硬件设计中采取了一些保护措施。其原理如下:

设CS为Q0,RDY为Q1,CPU的复位信号RE-SET为C。AT45D081的复位信号RESET1为Y, 则Y=(Q1Q2)C。因此,当CPU刚上电复位或由于主控CPU运行出错(如程序跑飞)而使“看门狗”芯片MAX813输出复位信号RESET产生热复位时,系统迫使AT45D081复位,同时禁止对该片的任何读写操作。当CPU处于正常工作时,只有该片的片选信号有效,同时芯片处于就绪状态时,才允许对其进行访问,否则迫使芯片处于复位状态并禁止访问,这样就防止了外界对其进行误写,从而有效地保护了片内数据。

图3

2.4 AT45D081的读写软件编程

AT45D081有关引脚接线如图3所示,下面给出针对写缓冲区和连续读主存储器阵列命令的51汇编语言软件编程。

;向缓冲区1写入数据

writebuf:

clr CS

mov a,#84h

lcall Byte_shift_out ;送命令码

clr a

lcall Byte_shift_out ;送8位任意码

mov a,hi_addr

lcall Byte_shift_out ;送高字节地址

mov a,lo_addr

lcall Byte_shift_out ;送低字节地址

writebuf0:

mov a,@r0

;连续读主存储器阵列内容

Readmain:

clr CS

mov a,#68h

lcall Byte_shift_out ;送命令码

clr c

mov a,lopageadd

rlc a

mov a,hi_page_addradd;

;合成24位地址的9~18位

rlc a

lcall Byte_shift_out;送前8位

mov a,hi_addr

rrc a

mov a,lopageadd

rlc a ;合成24位地址0~8位

lcall Byte_shift_out ;送第2个8位

mov a,lo_addr

lcall Byte_shift_out ;送0~7位

clr a

mov r3,#04H

readmain0:

lcall Byte_shift_out

djnz r3,readmain0 ;送32位无关位

readmain1:

lcall Byte_shift_in

mov @r0,a

inc r0 ;

;连续从指定的页及页内地址读出R2个数据

djnz r2,readmain1 ; 送命令码

setb CS

ret

ReadState: ;读状态寄存器内容

clr fmcs

MOV a,#57h;

lcall outcommon

lCALL incommon

setb fmcs

lcall Byte_shift_out; 连续从R0指定的地址写入R2个数据到BUFFER1

inc r0

djnz r2,writebuf0

setb CS

ret

3、结束语

本文设计的税控加油机已通过国家税控认证及电磁兼容试验认证。产品投产5年来,运行一直稳定可靠,各项指标均达到国家要求标准。尚未发现存储在AT45D081中的数据出现丢失和异常现象。

责任编辑:gt

-

芯片

+关注

关注

462文章

53538浏览量

459156 -

寄存器

+关注

关注

31文章

5589浏览量

129068 -

存储器

+关注

关注

39文章

7715浏览量

170854

发布评论请先 登录

stm32存储结构& 存储器映射

51单片机的内部结构简介

IGBT的内部结构及特点

PS501的内部结构图

8051单片机内部结构

大容量闪烁存储器芯片AT45D081的内部结构、特点及应用

大容量闪烁存储器芯片AT45D081的内部结构、特点及应用

评论