-Si539x时钟提升频率灵活性和抖动性能--Si56x Ultra Series™ XO/VCXO提供最大可达3GHz的任意频率时钟-。

中国,北京- 2018年6月26日- Silicon Labs(亦称 “芯科科技” ,NASDAQ: SLAB)日前宣布扩展其时钟产品系列,以满足56G PAM-4 SerDes和新兴112G串行应用对于高性能时钟的要求。通过此次产品系列的扩展,Silicon Labs成为唯一一家可为100/200/400/600G设计提供全面时钟发生器、抖动衰减时钟、压控晶体振荡器(VCXO)和XO选择的时钟供应商,并且满足100 fs以下参考时钟抖动要求并留有余量。

包括Broadcom、Inphi、Intel、MACOM、Marvell、MediaTek和Xilinx在内,领先的交换SoC、PHY、FPGA和ASIC制造商正在转移到56G PAM-4 SerDes技术,以支持更高带宽的100G+以太网和光网络设计。为了满足56G SerDes参考时钟的严格要求,硬件开发人员通常需要100 fs(典型值)以下RMS相位抖动规范的时钟。这些设计通常需要与CPU和系统时钟等其他频率时钟混用。Silicon Labs是首家为56G设计提供完全集成时钟IC解决方案的时钟产品供应商,该解决方案将SerDes、CPU和系统时钟集成到单一器件中。

在56G应用中,硬件开发人员通常会寻求完整的时钟树解决方案,以保证100 fs以下的RMS相位抖动,从而确保足够的余量并减少产品开发风险。Silicon Labs的新型时钟和振荡器产品满足当前这些严格的56G SerDes要求、以及新兴的112G串行SerDes设计需求,这些设计在未来的数据中心和通信应用中将得到迅速发展。

Silicon Labs时钟产品高级营销总监James Wilson表示:“Silicon Labs的新型时钟发生器、抖动衰减器和VCXO/XO构成了业界最广泛的、频率灵活的超低抖动时钟器件系列产品,适用于基于56G SerDes的最新100/200/400/600G通信和数据中心设计。无论我们的客户是在设计同步还是自由运行的系统,我们都能提供合适的超高性能时钟解决方案,以满足他们的56G SerDes应用需求。”

Silicon Labs Si5391是业界最低抖动、任意频率时钟发生器。它是市场上唯一能够从单一IC提供200/400/600G设计所需全部时钟频率的时钟发生器,同时为56G SerDes参考时钟提供100 fs以下RMS相位抖动性能。具有多达12个差分输出,Si5391时钟提供频率灵活的A/B/C/D等级选项。精密校准P级选项可以为56G SerDes设计中所需的主频率提供优化的69 fs(典型值)规格RMS相位抖动性能。Si5391是一款真正的100 fs以下“单芯片时钟树”解决方案,设计旨在从同一IC合成所有输出频率,同时满足56G PAM-4参考时钟抖动要求并留有余量。

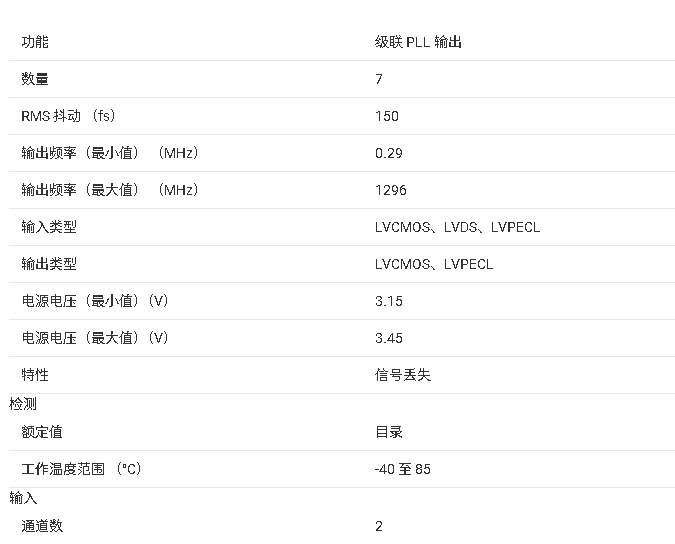

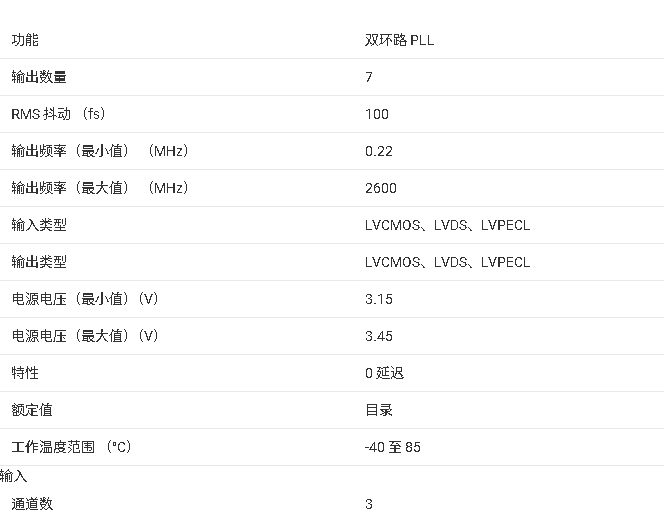

Silicon Labs Si539x抖动衰减器提供业内领先的抖动性能和频率灵活性。这些超低抖动时钟旨在满足互联网基础设施的严格规范和高性能要求,可降低各种时钟应用的成本和复杂性。Si539x任意频率抖动衰减时钟能够从任意频率输入时钟产生任意频率输出时钟组合,同时提供业界领先的抖动性能(90 fs RMS相位抖动)。Si5395/4/2 P级器件为56G/112G SerDes时钟应用提供了最佳的抖动性能(69 fs RMS典型相位抖动)。

新型Si56x Ultra Series VCXO和XO系列产品非常适用于需要超低抖动振荡器的下一代高性能时钟应用。Si56x VCXO/XO可定制到最大3GHz的任意频率,支持两倍于之前的Silicon Labs VCXO产品的工作频率范围,且抖动减半。Si56x振荡器采用业界标准的5mm x 7mm和3.2mm x 5mm封装,提供单路、双路、四路和I2C可编程选项,与传统XO、VCXO和VCSO的引脚兼容并可直接替换。该系列器件的典型相位抖动低至90 fs。

Silicon Labs还为需要更高稳定性及长期可靠性的应用提供Si54x Ultra Series XO系列产品,例如光传输网络(OTN)、宽带设备、数据中心和工业系统等应用。Si54x XO专为56G设计而构建,其依靠四级脉冲幅度调制(PAM-4)信号进行串行数据传输,以增加每通道的比特率,同时保持带宽不变。使用Si54x XO作为低抖动参考时钟可以最大限度地提高信噪比(SNR)余量,最大限度地减少误码并提高信号完整性。Si54x系列产品具有最佳的性能,且典型相位抖动低至80 fs。

价格与供货

Silicon Labs新型时钟和Ultra Series振荡器已经量产,可提供样片。这些时钟产品在一万片采购量时单价为:

• Si5391时钟发生器 — 6.05美元起

• Si539x抖动衰减时钟 — 6.60美元起

• Si56x XO/VCXO — 5.21美元起

Silicon Labs提供各种评估板(EVB)以加速器件评估和开发。时钟和振荡器EVB价格范围为95到299美元。Silicon Labs的ClockBuilder Pro(CBPro)软件支持Si5391和Si539x系列产品,这使得器件配置和定制变得非常简单。客户可以使用CBPro为其特定需求量身定制时钟解决方案,并可在两周内收到样片。

关于Silicon Labs

Silicon Labs(NASDAQ:SLAB)是领先的芯片、软件和解决方案供应商,致力于建立一个更智能、更互联的世界。我们屡获殊荣的技术正在塑造物联网、互联网基础设施、工业自动化、消费电子和汽车市场的未来。我们世界一流的工程团队创造的产品专注于性能、节能、互联和简易化。

-

时钟

+关注

关注

11文章

1953浏览量

134561 -

时钟发生器

+关注

关注

1文章

268浏览量

69891 -

SiliconLabs

+关注

关注

2文章

56浏览量

24948

发布评论请先 登录

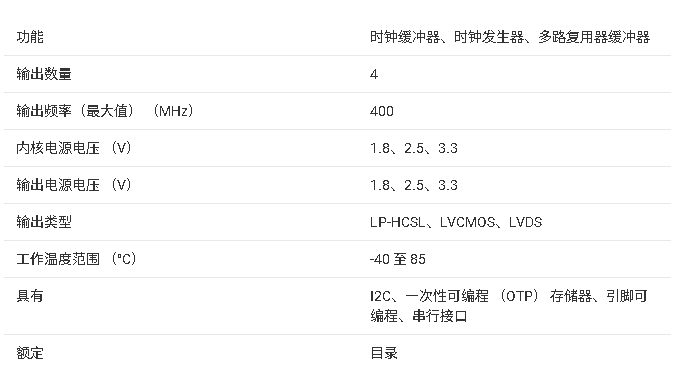

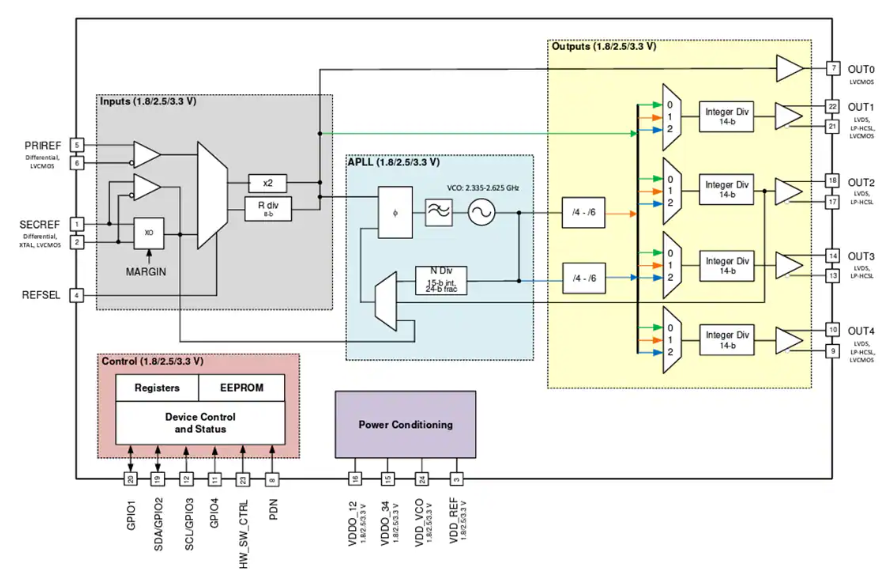

LMK3H2108超低抖动时钟发生器

探索时钟发生器的竞争优势

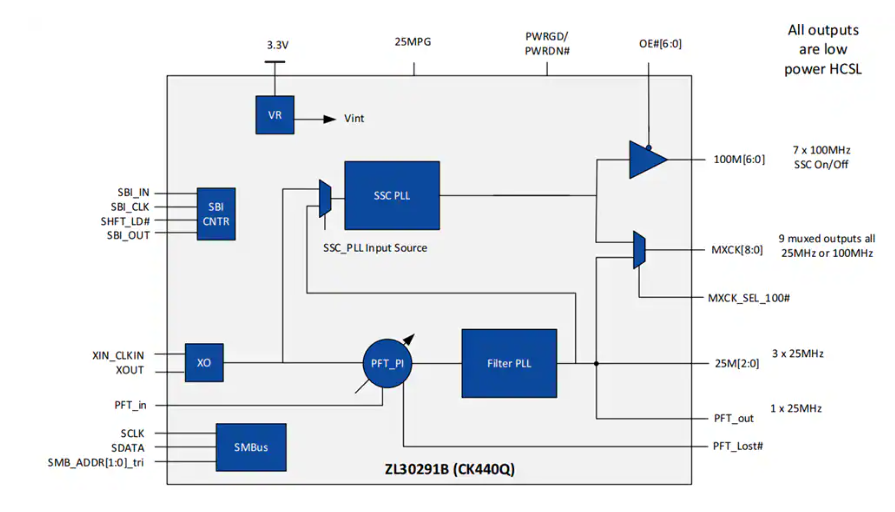

ZL30291B:面向PCIe Gen6与平台时序的高性能时钟发生器

CDCE62002 四输出时钟发生器/抖动清除器技术文档总结

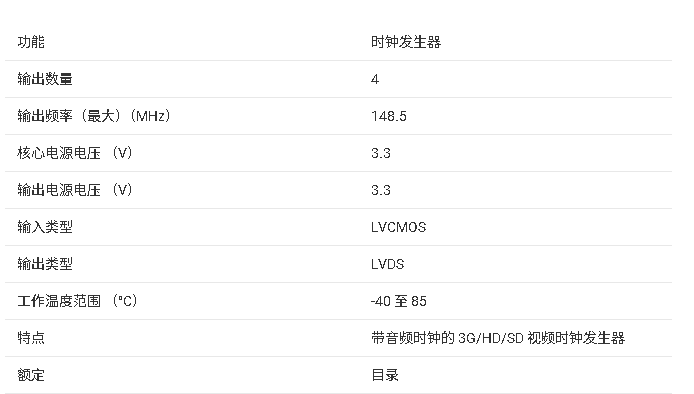

LMH1983 3G/HD/SD视频时钟发生器技术文档总结

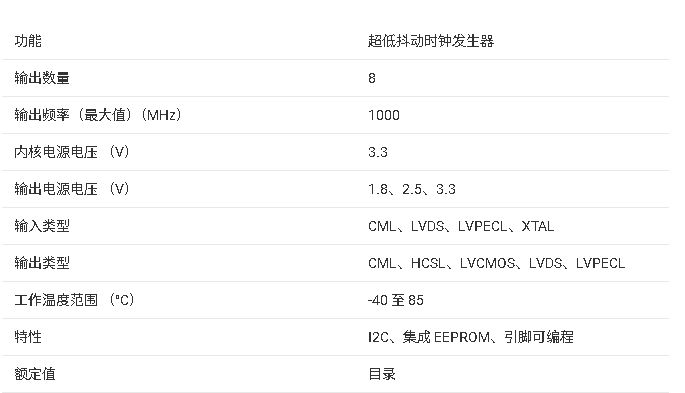

LMK03806 具有 14 个输出的超低抖动时钟发生器技术手册

LMK03328 具有两个独立 PLL 的超低抖动时钟发生器系列技术手册

LMK03318 具有单 PLL 的超低抖动时钟发生器系列技术手册

LMK3H2104 4-Output PCIe时钟发生器技术文档总结

德州仪器CDCE6214Q1TM超低功耗时钟发生器技术解析

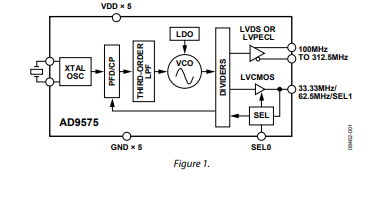

AD9575双路输出网络时钟发生器技术手册

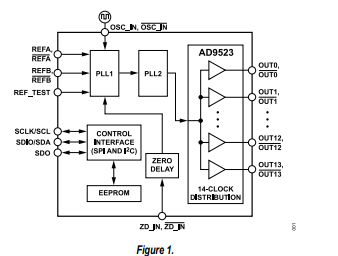

AD9523 14路输出、低抖动时钟发生器技术手册

Silicon Labs推新型时钟发生器 抖动衰减器和VCXO/XO堪称业界最超低抖动时钟器件系列

Silicon Labs推新型时钟发生器 抖动衰减器和VCXO/XO堪称业界最超低抖动时钟器件系列

评论