声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Altera

+关注

关注

37文章

771浏览量

153308 -

性能

+关注

关注

0文章

265浏览量

18817

发布评论请先 登录

相关推荐

给Altera Arria 10 FPGA和Arria 10 SoC供电:经过测试和验证的电源管理解决方案

尺寸、重量和复杂性,并可降低功耗和冷却成本。而且,它对于实现最优系统性能是必不可少的。例如,从 12V DC/DC 稳压器提供 0.95V/105A 以给图 1 的 Arria 10 GX FPGA

发表于 10-29 17:01

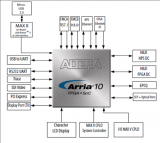

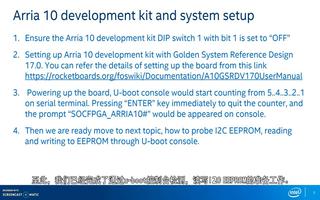

英特尔Arria 10 SOC FPGA开发板硬件支持32位 DDR4 SDRAM

,广泛的ARM软件和工具生态系统以及增强的FPGA和数字信号处理(DSP)硬件设计流程。Arria 10 SoC旨在满足中端应用的性能和功耗要求. 英特尔 Arria

发表于 05-20 14:05

•1271次阅读

英特尔Arria 10 FPGA的应用之路

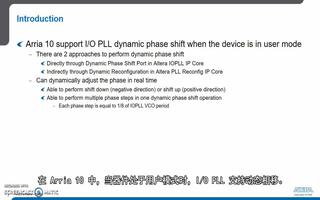

可提供中端市场中的最佳性能和能效。英特尔 Arria 10 FPGA 和 SoC 的高性能逻辑结构,结合了适用于芯片至芯片和芯片至模块接口、

Arria 10 SoC确保系统设计满足现在和未来性能要求

借助 Arria 10 SoC,您可以通过将 GHz 级处理器、FPGA 逻辑和数字信号处理 (DSP) 集成到单个可定制的片上系统中来减小电路板尺寸,同时提高性能。

Arria® 10 的性能

Arria® 10 的性能

评论