大家好,又到了每日学习的时间了,今天咱们来聊一聊数字信号处理中DFT、DTFT和DFS的关系,咱们通过几幅图来对比,探讨一下哦。

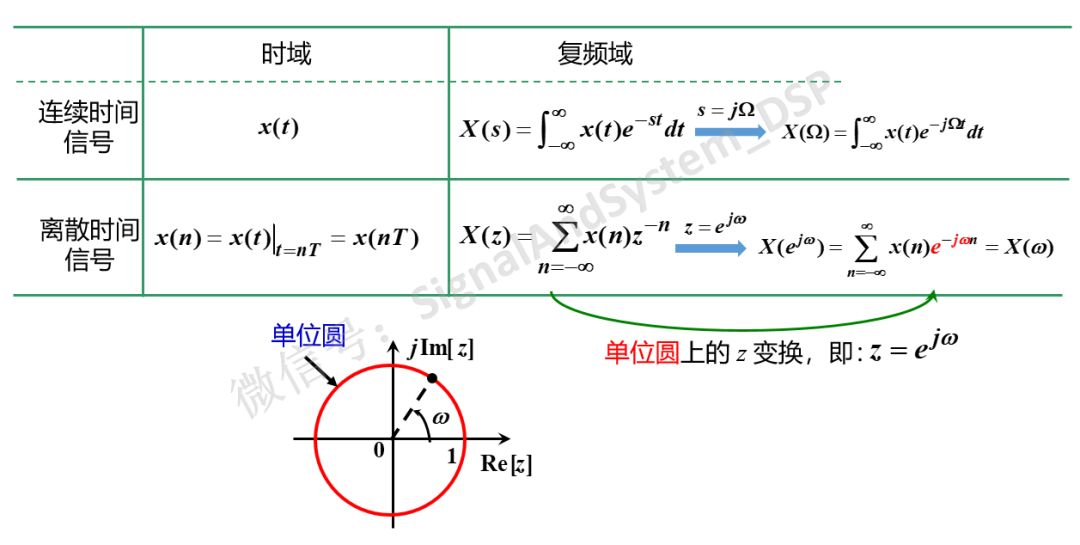

很多同学学习了数字信号处理之后,被里面的几个名词搞的晕头转向,比如DFT,DTFT,DFS,FFT,FT,FS等,FT和FS属于信号与系统课程的内容,是对连续时间信号的处理,这里就不过多讨论,只解释一下前四者的关系。

首先说明一下,我不是数字信号处理专家,因此这里只站在学习者的角度以最浅显易懂的性质来解释问题,而不涉及到任何公式运算。

学过卷积,我们都知道有时域卷积定理和频域卷积定理,在这里只需要记住两点:1.在一个域的相乘等于另一个域的卷积;2.与脉冲函数的卷积,在每个脉冲的位置上将产生一个波形的镜像。(在任何一本信号与系统课本里,此两条性质有详细公式证明)

下面,就用这两条性质来说明DFT,DTFT,DFS,FFT之间的联系:

先看图片:

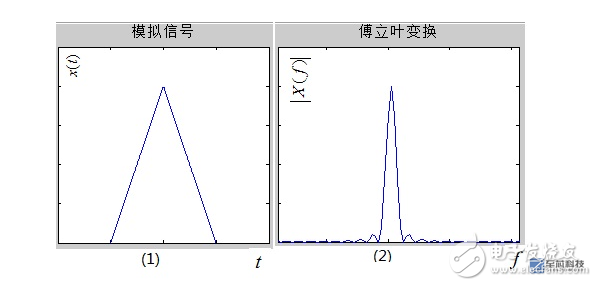

首先来说图(1)和图(2),对于一个模拟信号,如图(1)所示,要分析它的频率成分,必须变换到频域,这是通过傅立叶变换即FT(Fourier Transform)得到的,于是有了模拟信号的频谱,如图(2);注意1:时域和频域都是连续的!

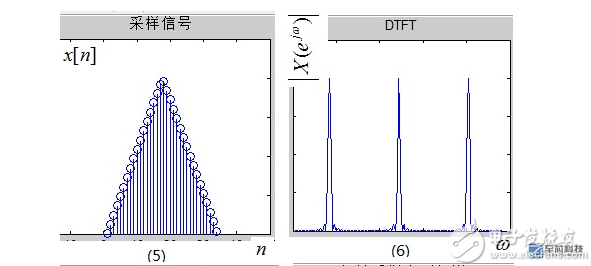

但是,计算机只能处理数字信号,首先需要将原模拟信号在时域离散化,即在时域对其进行采样,采样脉冲序列如图(3)所示,该采样序列的频谱如图(4),可见它的频谱也是一系列的脉冲。所谓时域采样,就是在时域对信号进行相乘,(1)×(3)后可以得到离散时间信号x[n],如图(5)所示;由前面的性质1,时域的相乘相当于频域的卷积,那么,图(2)与图(4)进行卷积,根据前面的性质2知,会在各个脉冲点处出现镜像,于是得到图(6),它就是图(5)所示离散时间信号x[n]的DTFT(Discrete time Fourier Transform),即离散时间傅立叶变换,这里强调的是“离散时间”四个字。注意2:此时时域是离散的,而频域依然是连续的。

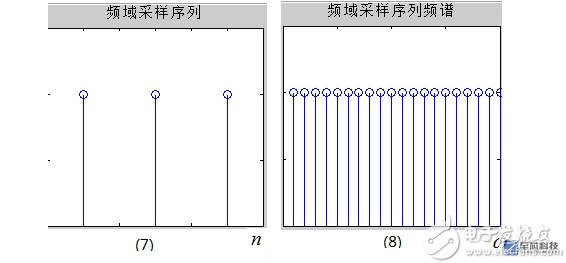

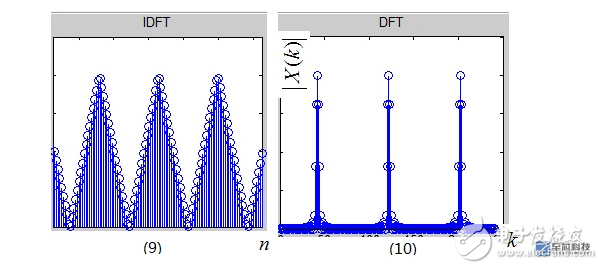

经过上面两个步骤,我们得到的信号依然不能被计算机处理,因为频域既连续,又周期。我们自然就想到,既然时域可以采样,为什么频域不能采样呢?这样不就时域与频域都离散化了吗?没错,接下来对频域在进行采样,频域采样信号的频谱如图(8)所示,它的时域波形如图(7)。现在我们进行频域采样,即频域相乘,图(6)×图(8)得到图(10),那么根据性质1,这次是频域相乘,时域卷积了吧,图(5)和图(7)卷积得到图(9),不出所料的,镜像会呈周期性出现在各个脉冲点处。我们取图(10)周期序列的主值区间,并记为X(k),它就是序列x[n]的DFT(Discrete Fourier Transform),即离散傅立叶变换。可见,DFT只是为了计算机处理方便,在频率域对DTFT进行的采样并截取主值而已。有人可能疑惑,对图(10)进行IDFT,回到时域即图(9),它与原离散信号图(5)所示的x[n]不同呀,它是x[n]的周期性延拓!没错,因此你去查找一个IDFT的定义式,是不是对n的取值区间进行限制了呢?这一限制的含义就是,取该周期延拓序列的主值区间,即可还原x[n]!

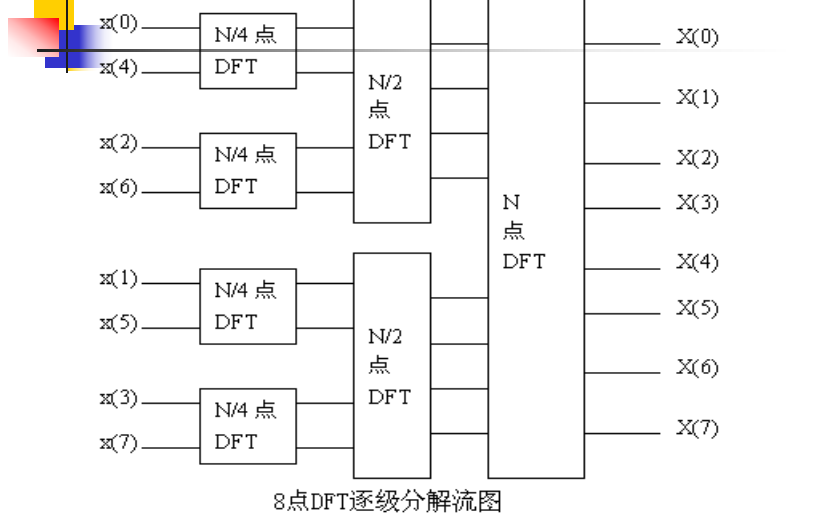

FFT呢?FFT的提出完全是为了快速计算DFT而已,它的本质就是DFT!我们常用的信号处理软件MATLAB或者DSP软件包中,包含的算法都是FFT而非DFT。

DFS,是针对时域周期信号提出的,如果对图(9)所示周期延拓信号进行DFS,就会得到图(10),只要截取其主值区间,则与DFT是完全的一一对应的精确关系。这点对照DFS和DFT的定义式也可以轻易的看出。因此DFS与DFT的本质是一样的,只不过描述的方法不同而已。

不知道经过上面的解释,您是否明白各种T的关系了呢?如果您不是算法设计者,其实只要懂得如何使用FFT分析频谱即可,博主近期会更新一篇文章,专门介绍如何利用FFT分析简单信号的频谱。

其实个人认为,纠结了这么多,就是为了打破现实模拟世界与计算机数字世界的界限呀!

今天就聊到这里,各位,加油。

-

FPGA

+关注

关注

1602文章

21320浏览量

593176 -

TFT

+关注

关注

10文章

374浏览量

109778 -

卷积

+关注

关注

0文章

95浏览量

18409

发布评论请先 登录

相关推荐

FT,FS,DFT,DTFT,DFS,FFT有何关系

序列的傅里叶变换(DTFT)

什么是DFT,DFT是什么意思

离散序列的傅里叶变换DTFT

离散信号与系统的频域分析,信号与系统电子课件六免费下载mfxz

聊一聊数字信号处理中DFT、DTFT和DFS的关系

如何用DFS算法来秒杀岛屿系列问题

几幅图弄清DFT、DTFT和DFS的关系

几幅图弄清DFT、DTFT和DFS的关系

评论