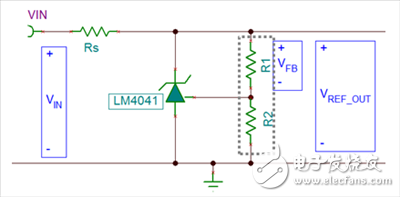

可调参考电压源为电路设计者提供了极大的灵活性,因为该参考电压不再局限于制造商的预设值。从输出到反馈引脚,可调输出通常会配置一个分压器,如图1所示。为调节输出,将反馈引脚的电压与内部参考电压(在本帖中显示为VREF_INT)作比较,通常为1.2V。设备会对输出电压进行调节,直到VFB和VREF_INT相匹配。

一些可调并联参考(如LM4041)使VFB通过R1;还有一些并联参考会使VFB通过R2,如TLV431。而我主要研究LM4041,但在方程中,通过转换R1和R2,此概念同样适用于其他可调并联参考。在本篇博文上,我将介绍一种用数字信号改变电阻分压器和参考电压的方法。

图1:典型的VREF反馈分频器

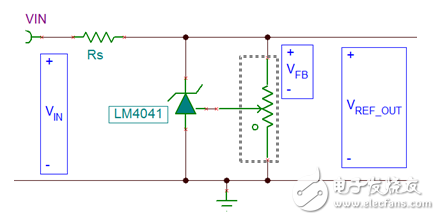

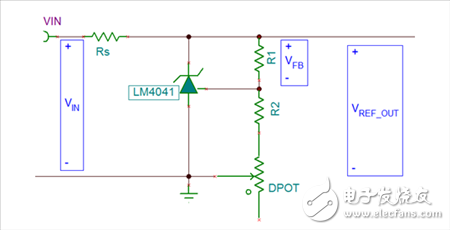

该方法中使用一个数字电位计替代两个固定电阻。图2概念性地展示了这一点,其中反馈引脚与电位计的弧刷相连接,高端连接VREF,低端连接GND。

图2:电位计中央分接头(弧刷)连接反馈引脚

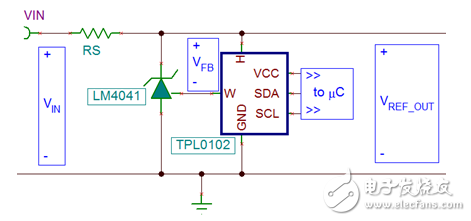

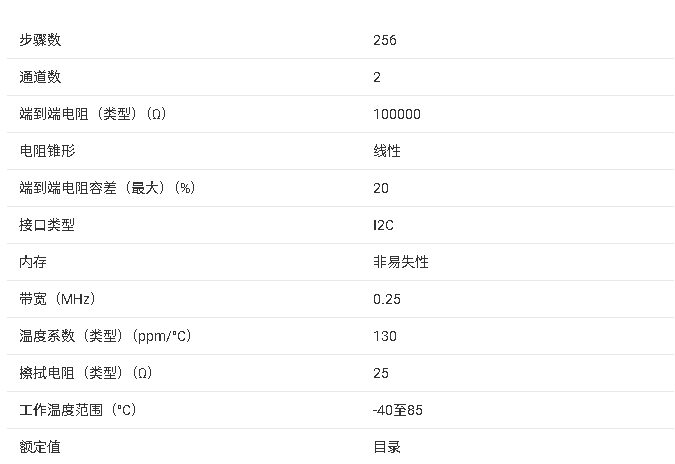

图3展示的是重绘电路,用TPL0102数字电位计充当电压分频器。通过连接穿过内部电阻高低引脚的电压,连接输出与弧刷引脚,可以安装一个数字电位计作为电压分频器。弧刷的位置会影响弧刷与高低引脚间的电阻比率,此外通过向设备发送代码,可以用数字方式对该位置进行控制。TPL0102使用I2C接口,其他电位计使用串行外设接口或平行接口。

图3:TPL0102数字电位计作为反馈分频器时的VREF

因为电阻比率设定输出电压,所以分频器电阻的绝对值不是至关重要的。这样一来,便可以轻松用数字电位计来替代电阻分频器。方程1中展示了调节输出、VREF_OUT和电阻比率之间的关系:

在该应用中,这一点非常重要,因为数字电位计的绝对电阻值变化很大,而电阻比率却是非常准确。例如,为产生3.3伏的参考电压,要求R2对R1的电阻比率为1.66。

电位计数据表中提供了用于计算特定代码电压分频器输出的公式,如方程2和方程3所示。其中,VHW表示从高引脚(H)到弧刷的电压,而VWL表示从弧刷(W)到低引脚(L)的电压:

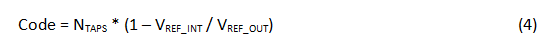

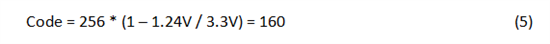

我在介绍中提到VFB通过R1,所以我们继续使用方程2,计算高引脚与弧刷引脚之间的电压。弧刷连接至设备的反馈引脚,VFB被迫为VREF_INT。方程4展示了用于求出VREF_OUT所要求数字代码的公式:

继续讨论方程5中的例子,其中NTAPS为256,VREF_INT为1.24伏,VREF_OUT为3.3伏,你需要写出十进制码160,得出R1和R2电阻值分别为37.50kW和62.50kW。更重要的是,用方程1计算得出这两个电阻的比率同样是1.66。

如果你需要改变参考电压,你只需写出I2C事务,相应地移动弧刷位置即可。因此,反馈引脚的电压会改变并调节VREF_OUT。你也可以使用电位计以数字方式调整参考电压,电位计上的分接头越多,电阻率的分辨率越高,输出参考电压的分辨率也就越高。

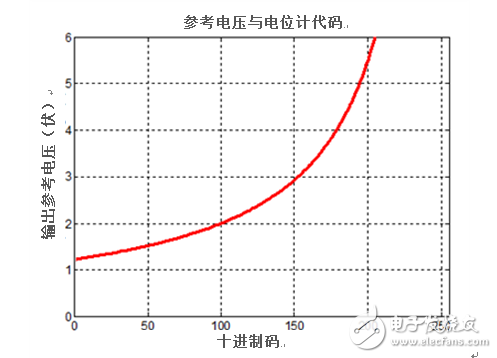

该应用中使用数字电位计的一大缺陷在于数字电位计集成电路的电压极限一般不能超过5.5伏。可以确定的是,电阻率不会出现VREF_OUT大于5.5伏的情况。对于一个有256个分接头的数字电位计和内部参考电压为1.24伏的并联参考来说,十进制码不能超过200。图4展示了输入码对有256个分接头的电位计和1.24伏参考设备的参考电压的影响。

图4:参考电压与数字电位计代码

为并联参考通电之前安装使用电位器可以保证将电阻分压器放在正确位置。如果不可行,则可以在未使VFB降低的电阻上并联加装一个大电阻器。这样一来,LM4041从反馈引脚(通过R2)到地面的功率将为1MW,或者TLV431从反馈引脚(通过R1)到输出口的功率将为1MW。

为避免再产生一个并联电阻,可以在设备上安装固定R1和R2电阻器,并将数字电位计与其中一个电阻串联连接。然后需安装电位计作为变阻器,如图5所示。这种安装方法取决于数字电位计的绝对电阻值,它不像作为比率计分压器时那样精确,需向微控制器提供反馈从而最终做出数字编码的选择。

图5:以数字电位计为变阻器的固定电阻器

既然你了解了用可调参考电压设置输出电压的方法,你就知道如何利用其随时改变输出电压。如果你在应用中已经使用了微控制器,那么搭配使用数字电位计可以给一个看似简单的零部件添加一些功能。

其他资源

-

基准电压源

+关注

关注

1文章

384浏览量

22280 -

LM4041D12

+关注

关注

0文章

2浏览量

6360

发布评论请先 登录

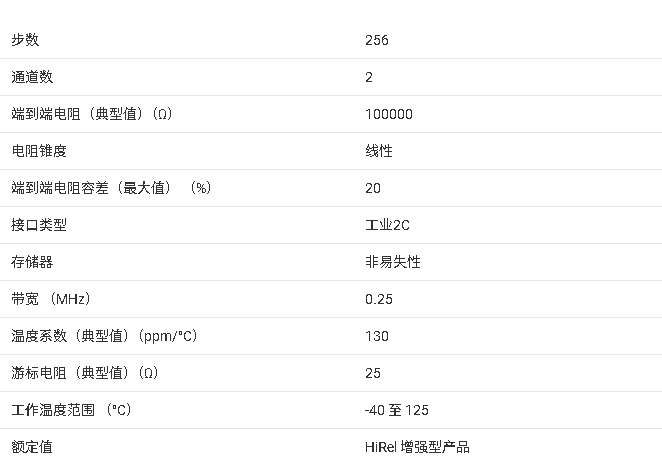

TPL0102-100 双路 256 抽头非易失性数字电位器产品总结

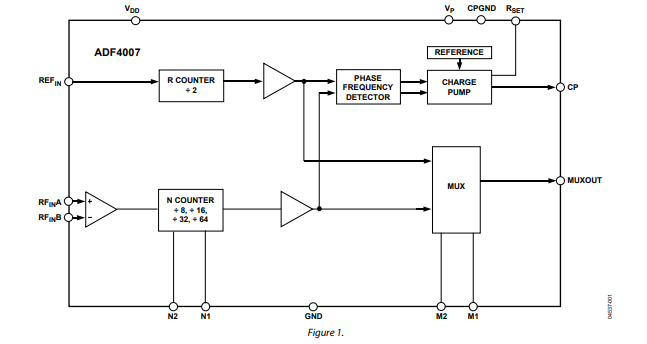

ADF4007高频分频器/PLL频率合成器技术手册

用TPL0102数字电位计充当电压分频器设计

用TPL0102数字电位计充当电压分频器设计

评论