设计背景:

Verilog HDL语言分为面向综合和面向仿真两大类语句,且可综合语句远少于仿真语句,读者可能会有可综合设计相对简单的感觉。然而事实刚好与此相反,这是因为:首先,可综合设计是用来构建硬件平台的,因此对设计的指标要求很高,包括资源、频率和功耗,这都需要通过代码来体现;其次,在实际开发中要利用基本Verilog HDL语句完成种类繁多的硬件开发,给设计人员带来了很大的挑战。所有的仿真语句只是为了可综合设计的验证而存在。为了让读者深入地理解可综合设计、灵活运用已学内容,本章将可综合设计中的基本知识点和难点提取出来,融入Verilog HDL语法以及开发工具等诸多方面,以深入浅出的方式向读者说明设计中的难点本质。

设计原理:

本次的设计主要是用来理解组合和时序逻辑的关系和写法,通过描述组合和时序逻辑电路来仿真出对用的仿真波形,然后来分析其逻辑特点和相应的关系。

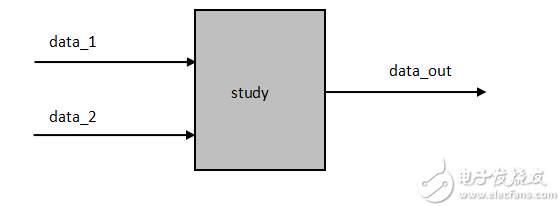

设计架构图:

设计代码:

组合逻辑设计模块

0modulestudy(data_1,data_2,data_out);//端口列表

1

2 inputdata_1,data_2;//输入

3 outputregdata_out;//输出

4

5 //描述一个组合逻辑电路

6 always@(*)

7 begin

8 data_out =data_1 &&data_2;//与逻辑

9 end

10

11endmodule

测试模块

0`timescale1ns/1ps

1

2moduletb;

3

4 regdata_1,data_2;//定义输入寄存器

5 wiredata_out;//定义输出线型

6

7 study study_dut(//设计模块端口例化

8 .data_1(data_1),

9 .data_2(data_2),

10 .data_out(data_out)

11 );

12

13 initialbegin//描述数据流的变化

14 data_1 =0;data_2 =0;

15 #200

16 data_1 =1;data_2 =0;

17 #200

18 data_1 =0;data_2 =1;

19 #200

20 data_1 =1;data_2 =1;

21 #200

22 data_1 =0;data_2 =0;

23 #200

24 $stop;//系统任务停止

25 end

26

27endmodule

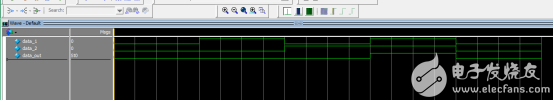

组合逻辑仿真图:

在仿真波形中可以清楚的看到输入数据流的变化顺序,数据翻转后,输出立马改变没有延迟。

时序逻辑设计模块

0modulestudy(clk,data_1,data_2,data_out);//端口列表

1

2 inputclk,data_1,data_2;//输入

3 outputregdata_out; //输出

4

5 //描述一个组合逻辑电路

6 always@(posedgeclk)

7 begin

8 data_out <=data_1 &&data_2;//与逻辑

9 end

10

11endmodule

测试模块

0`timescale1ns/1ps

1

2moduletb;

3

4 regclk,data_1,data_2;//定义输入寄存器

5 wiredata_out;//定义输出线型

6

7 study study_dut(//设计模块端口例化

8 .clk(clk),

9 .data_1(data_1),

10 .data_2(data_2),

11 .data_out(data_out)

12 );

13

14 initialbegin//描述数据流的变化

15 clk =1;data_1 =0;data_2 =0;

16 #200.1

17 data_1 =1;data_2 =0;

18 #200.1

19 data_1 =0;data_2 =1;

20 #200.1

21 data_1 =1;data_2 =1;

22 #200.1

23 data_1 =0;data_2 =0;

24 #200

25 $stop;//系统任务停止

26 end

27

28 always#10clk =~clk;

29

30endmodule

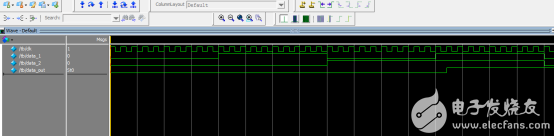

时序逻辑仿真图:

在仿真中可以清楚的看到,在时序逻辑中,我们或综合处寄存器,也就是说得到的数据会在寄存器中存一个上升沿,因为用的是上升沿触发,在波形中一看到。当两个输入都为高电平的时候输出也应该为高电平,可是没有立马的变为高电平,要等下一个上升沿来了才能变为高电平。

这样就直观的看清楚了组合和时序逻辑综合出的波形的差距,也就是一个有综合出是线型,一个是寄存器。

-

FPGA

+关注

关注

1602文章

21320浏览量

593159 -

时序逻辑

+关注

关注

0文章

37浏览量

9099

发布评论请先 登录

相关推荐

FPGA之组合逻辑与时序逻辑、同步逻辑与异步逻辑的概念

FPGA实战演练逻辑篇47:消除组合逻辑的毛刺

勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑

FPGA零基础学习:数字电路中的组合逻辑

数字设计FPGA应用:时序逻辑电路FPGA的实现

FPGA学习系列:6.组合逻辑和时序逻辑

FPGA学习系列:6.组合逻辑和时序逻辑

评论