什么是多路选择器

多路选择器是数据选择器的别称。在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。

FPGA中多路选择器结构

典型的FPGA器件主要包含3类基本资源:可编程逻辑块(configurablelogicblock,CLB)、布线资源和可编程输入/输出模块。可编程逻辑块四周被预制的布线资源通道包围,可编程输入/输出模块分布在FPGA四周,除了上述3种资源以外,通常在FPGA中还包含块RAM、乘法器等可选资源。

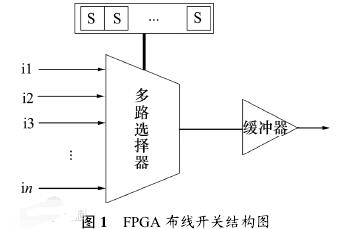

在FPGA各种资源中,可编程逻辑块是实现用户功能的基本单元,每个可编程逻辑块包含1个互连开关矩阵和4个SLICEs,其中每个SLICE包括2个查找表(Look-Up-Table,LUT)、2个触发器和一些多路选择器。互连开关矩阵主要由不同长度导线和多个布线开关组成,典型的布线开关结构如图1所示。

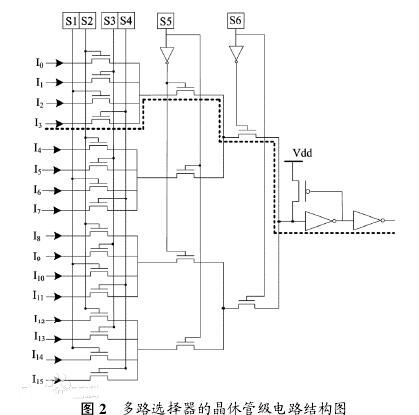

由图1可见:每个布线开关由多路选择器、缓冲器和一些可编程的SRAM单元构成。其中多路选择器是连接各布线轨道和可编程逻辑块的桥梁,其结构对FPGA的性能和功耗都有较大的影响。根据多路选择器所驱动的导线长度不同,FPGA中多路选择器的规模从4选1到30选1不等。图2所示为16选1的多路选择器晶体管级电路结构。

多路选择器的左边是 16 条输入线,用于连接布线轨道或可编程逻辑块等资源,S1~S6 代表 6 个可编程SRAM 单元,通过配置 SRAM 单元的内容可以从 16条输入线中选出 1 条作为有效输入端,例如,当 S1~S6存储单元的存储值为“000100”时,输入线 I3被选择中,信号所经过的有效路径如图 2 中虚线所示。多路选择器的主体部分是传输晶体管,由于 NMOS 晶体管载流子的迁移效率高,电路速度快,因此,多路选择器中的传输晶体管均采用 NMOS 晶体管实现。

多路选择器工作原理

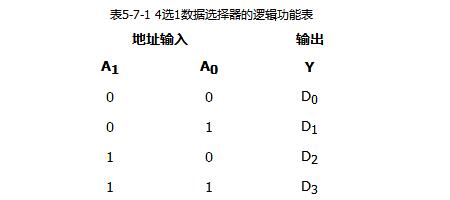

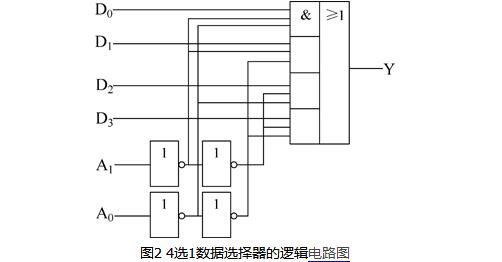

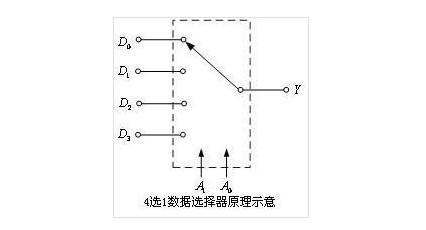

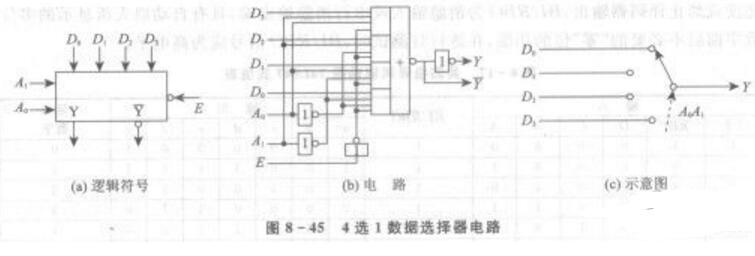

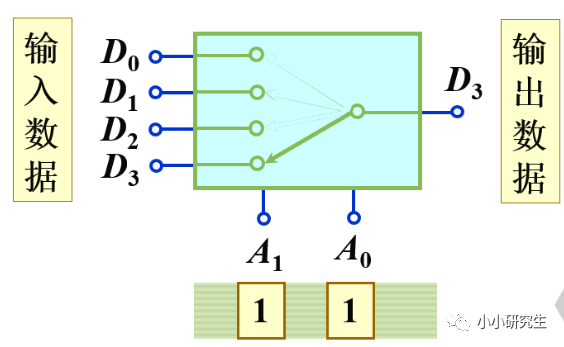

常用的多路选择器有4选1、8选1、16选1等多种类型。下面以4选1数据选择器为例介绍数据选择器的工作原理。根据前面介绍的数据选择器的功能,可以列出4选1数据选择器的逻辑功能表,如表5-7-1所示。其中D0~D3为数据输入端,A0、A1为数据选择端。

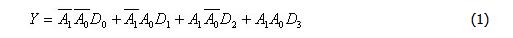

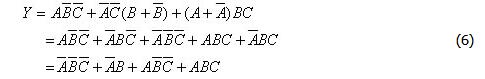

由逻辑功能表可以写出输出与输入之间的表达式为

由逻辑表达式画出4选1数据选择器逻辑电路2所示。

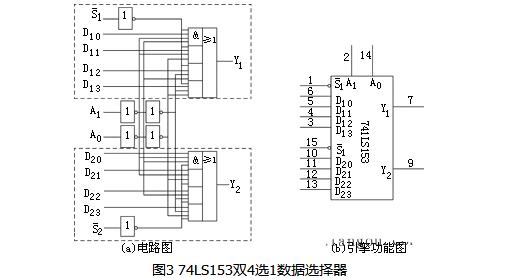

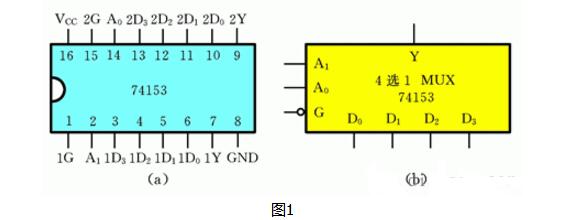

74LS153是一种集成的双4选1数据选择器逻辑器件。图3所示为74LS153的逻辑电路图和框图。

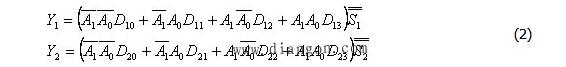

由图3(a)可知,74LS153的逻辑电路中包含两个4选1数据选择器,它们的数据输入端分别为D10、D11、D12、D13和D20、D21、D22、D23,数据输出端分别为Y1和Y2。它们有公共的地址选择输入端A0、A1。除此之外,还各自有有一个使能控制端 。由图3(a)可以写出输入与输出之间的逻辑函数式为

。由图3(a)可以写出输入与输出之间的逻辑函数式为

由式(2)可以看出,只有当使能控制端 时,数据选择器才能正常工作,否则数据输出端锁定在低电平。故使能控制端为低电平有效。

时,数据选择器才能正常工作,否则数据输出端锁定在低电平。故使能控制端为低电平有效。

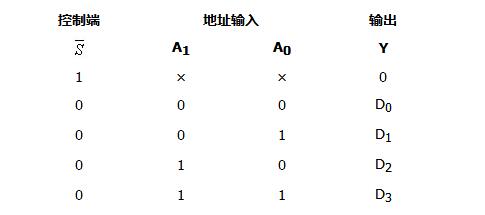

74LS153的逻辑功能表如表2所示。

表2 74LS153的逻辑功能表

多路选择器的应用

(1)多路选择器的扩展应用

可以用多片少数据输入的数据选择器设计多数据输入的多路选择器。

例1:用74LS153设计一个8选1的数据选择器。

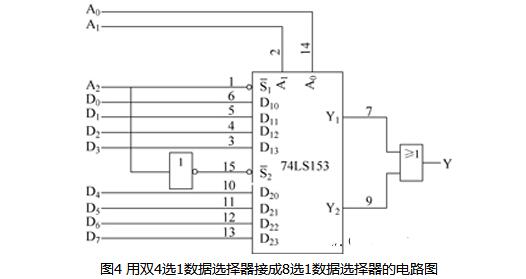

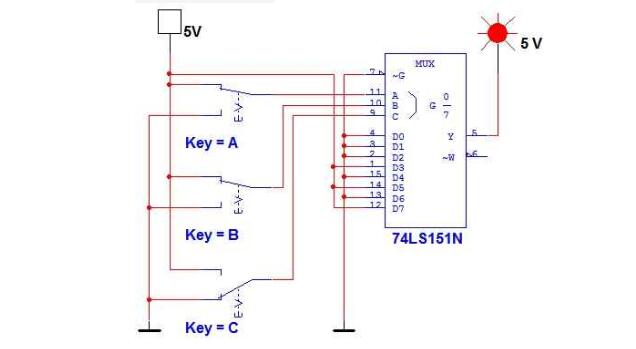

解:74LS153是一个双4选1多路选择器。有两个公用的地址选择输入端,8个数据输入端。8选1数据选择器需要3个地址输入端(23=8),因此需要用使能控制端来补充地址输入端的不足。用双4选1数据选择器芯片74LS153设计的8选1数据选择器的电路如图4所示。

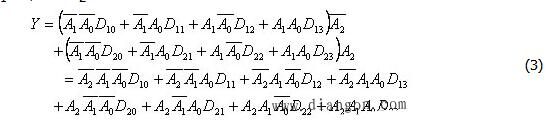

当A2=0时,上边的4选1数据选择器工作,根据地址输入端A0、A1的状态,输出端Y1选择输出D0~D3,此时Y2=0,故Y=Y1;当A2=1时,下边的4选1数据选择器工作,根据地址输入端A0、A1的状态,输出端Y2选择输出D4~D7,此时Y1=0,故Y=Y2。逻辑函数式为

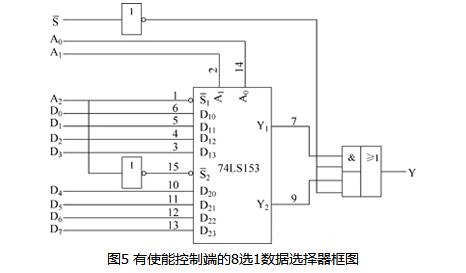

也可以添加使能控制端对所接成的8选1数据选择器的工作状态进行控制。添加使能控制端的8选1数据选择器的电路如图5所示。

由图5可知,当=0时,8选1数据选择器正常工作;当=1时,8选1数据选择器的输出被锁定在低电平。

(2)用多路选择器设计组合逻辑电路

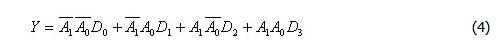

由表2可知,具有两位地址输入A0、A1的4选1数据选择器,当使能控制端=0时,输出与输入之间的逻辑关系式为

若将A0、A1作为两个输入变量,同时令D0~D3为第三个变量的适当状态(包括原变量、反变量、0和1),就可以用4选1数据选择器实现任何形式的三变量组合逻辑函数。

同理,用由n位地址输入端的多路选择器可以实现任何形式的变量数不大于n+1的组合逻辑函数。

例2:用4选1数据选择器实现以下组合逻辑函数:

解:将式(4)化成与式(5)相对应的形式:

将式(6)与式(4)比较可知,只要令数据选择器的数据输入端为

则多路选择器的输出就是所要表达的组合逻辑函数。

多路选择器的设计实现

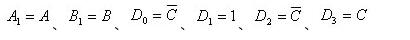

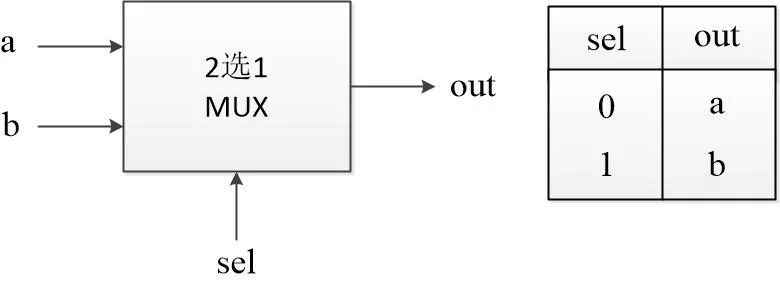

设计一个二位4路选择器,由于选择器使用条件触发的方法对应真值表进行匹配输出与输入,因此可以联想到在C程序设计中的条件语句“If”和“Case”两种,那么这两种设计从硬件的角度出发有什么不同呢?

代码如下:

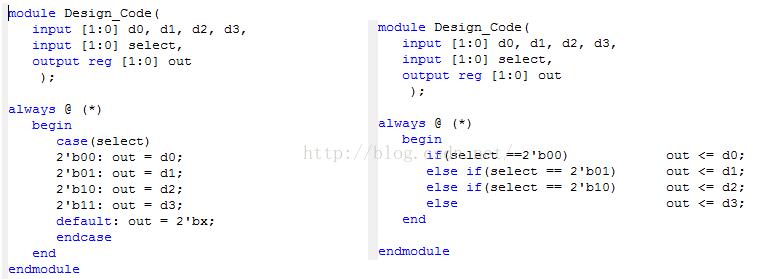

为了区别两种设计的不同,可以查看ISE提供的综合报告,操作如下:

综合报告对比:

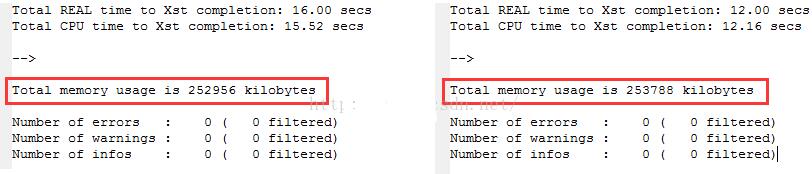

使用Case条件语句 使用IF条件语句

由综合报告查看可知,if语句运用的元器件多于case语句运用的元器件,同时,if语句中每一个分支之间具有优先级(串行),得到类似级联的结构;而case语句所有分支处于同一优先级(并行),综合可以得到一个多路选择器。因此,对于设计多路选择器而言,if语句所造成的延时往往比case语句的大,所以对于多路选择器而言,运用case语句的效果会更好。

Case语句下可能出现锁存器。注释case条件下的case语句块的某一行可以得到不完整的case语句下的2位四路选择器。由不完整case语句下的2位四路选择器可知:由于case语句所有分支处于同一优先级,所以当条件不完整时,对于处理结果,它不取决于语句的先后顺序,只取决于待处理信号,而处理结果为与待处理信号相差1’b1的信号的处理结果,在这一条件下相当于与待处理信号相差1’b1的信号的处理结果得到了锁存,锁存器因此产生。

对与锁存器而言,锁存器在待处理信号存在Glitch的情况下,可能会对Glitch产生锁存,从而导致锁存出现严重错误,是目标信号处理结果与预期目的产生极大的偏差,因此锁存器存在不稳定因素,所以在使用锁存器时,要牢记优先消除待处理信号的Glitch。

测试文件:

initial begin

// Initialize Inputs

d0 = 0;

d1 = 1;

d2 = 2;

d3 = 3;

select = 0;

#100;

select = 1;

#100;

select = 2;

#100;

select = 3;

#100;

// Add stimulus here

end

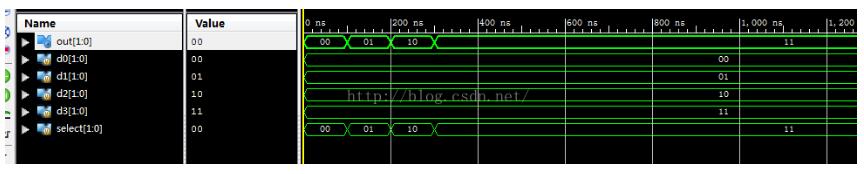

仿真结果:

-

数据选择器

+关注

关注

2文章

114浏览量

16332 -

多路选择器

+关注

关注

1文章

22浏览量

6437

发布评论请先 登录

相关推荐

FPGA基础学习笔记--组合逻辑电路-多路选择器与多路分解器

4选1多路选择器是什么?

8选1多路选择器电路图(五款8选1多路选择器电路)

一文解析多路选择器的工作原理及电路实现

一文解析多路选择器的工作原理及电路实现

评论