引言

随着电子系统的不断发展,芯片间以及板间的数据传输需求也在不断增长,传统的单端并行数据传输模式早已不能满足现在高带宽应用的要求。USB 3.0、SATA 3.0、PCI-E 2.0等新串行规范的发布以及更高速的串并/并串转换单元(SERDES)芯片的推出更是引起了业界对高速差分串行数据传输的无限憧憬。为了解决下一代无线通信基站中多天线(MIMO)信号处理所带来的巨大数据吞吐量要求,本文基于Virtex-5 FPGA的GTP单元给出了一种在高级电信计算架构(ATCA)机箱内实现单对差分线进行3.125Gbps串行传输的设计方案。

传输系统设计

传输系统的组成结构如图1所示,主要由两块ATCA板和一块ATCA机箱背板组成。两块ATCA板上各放置一片FPGA作为串行链路的两个端点,两片 FPGA之间用两对差分线进行连接,形成双向各3.125Gbps的串行通信链路。为了验证该系统的远距离传输能力,将两块板放置在14槽ATCA机箱的物理槽位1和物理槽位14,此时总的传输距离大约为40英寸。

图1 高速串行传输系统的总体结构

由于已有ATCA机箱的背板性能不可更改,本文主要的设计集中在ATCA单板的设计上,主要是单板的叠层设计、作为传输端点的FPGA的供电设计、串行传输的参考时钟设计以及FPGA内部GTP收发器单元的参数调节。

叠层设计

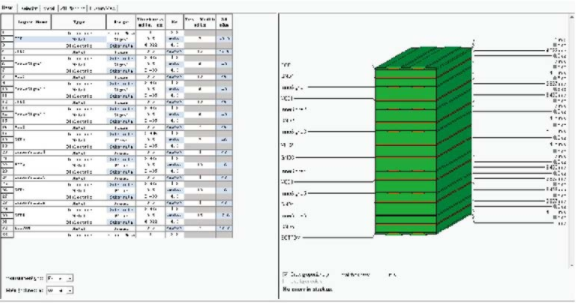

叠层设计是其他设计的基础,本系统在设计叠层结构的时候主要考虑了两个方面:一是让所有的GTP收发差分线布于带状线信号层而不是单边耦合的微带线信号层。虽然带状线比微带线损耗大一些,但是带状线的阻抗更可控一些,而且与交流地平面的耦合更好,有利于高速信号的回流;二是为了减少GTP单元的供电噪声,采用三个电源平面分别给串行收发器的三种模拟电源AVTT(端接电源)、AVCC(内部电路电源)、AVPLL(PLL电源)进行供电。具体的叠层结构如图2所示。

图2 叠层结构的设计

电源设计

GTP模拟供电电源的噪声情况是影响GTP性能的重要因素之一。除了在设计叠层的时候让GTP的三个模拟电源分别分配到一个单独的平面上并配上地平面进行耦合外,还在外部为每个电源管脚都串联一个磁珠,再并联一个0.22μf的电容形成一个LC低通滤波器对电源进行滤波。GTP的模拟电源都采用低噪声的 LDO电源芯片TPS74401进行供给,输出电压的纹波小于50mV。

时钟设计

高速串行收发器的参考时钟是另一个影响信号传输质量的重要因素。本系统使用具有强大clock clean功能的时钟合成芯片LMK03001C来产生串行收发器的参考时钟。其输出时钟的最大均方根抖动(RMS jitter)小于550fs,占空比为50%,输出时钟电平标准具有LVDS和LVPECL两种。其输出时钟的频率可以灵活编程设置,从而可以满足不同传输速率的要求,使本系统可以适应多种串行传输协议的实现。

预/去加重和均衡参数设计

为了对抗传输路径对高频分量的过多衰减,有必要在发送端进行预加重或者在接收端加上均衡或者同时使用两种手段。预/去加重和线性均衡都是通过对信号的畸变来改善接收信号的质量,只有合适的预/去加重和线性均衡的比例以及两者之间的组合才能达到改善接收信号质量的目的,否则反而会恶化接收信号的质量。本文利用GTP的SPICE模型以及串行传输信道的S参数模型对在不同预/去加重和均衡参数设置下的串行链路传输质量进行仿真,从而找出合适的参数设置。

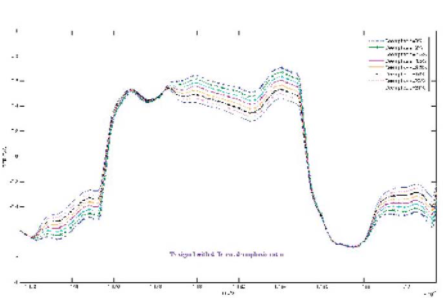

图3 不同预/去加重比例下的发送信号

图3即为在不同预/去加重比重设置下的仿真结果图。中间部分显示的是连续3个高电平比特的发送波形,很明显,后面两个高电平比特的幅值随预/去加重的比例相应地降低了。另外,图中同一个逻辑位里的信号电平并不平坦,这种现象主要是因信号传输链路上的阻抗不匹配处引起的发射造成的,例如ATCA单板与 ATCA背板的接插件连接处。

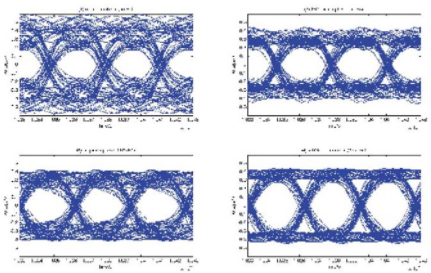

图4 预/去加重和均衡对接收信号的影响

图4给出的是GTP在不同参数设置下接收信号的眼图。其中第1个子图为在发送端未施加预/去加重的情况下,接收端FPGA管脚上的信号眼图。可见,长距离的传输严重恶化了信号的质量,信号眼图趋于闭合。第2个子图为在发送端施加23%的预/去加重时,接收端FPGA管脚上的信号眼图。预/去加重一定程度上弥补了传输信道的低通特性,降低了信号的抖动,改善了信号的质量。第3个子图为发送端未施加预/去加重而在收端施加25%的均衡,即把75%的原始信号加上25%的高通滤波器的输出作为总的接收信号。如同预/去加重一样,通过均衡,高频分量相对被增强,低频分量相对被抑制,有效地补偿了信道的不理想性。第 4个子图为在4.5%的预/去加重和25%均衡同时作用时得到的接收信号。可见,预/去加重和均衡的有效搭配可以很好地改善原本被严重恶化的传输信号。

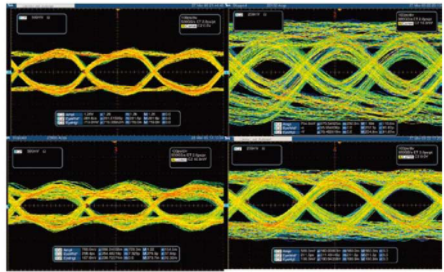

图5 实测串行信号眼图

验证与结果讨论

对本系统的性能测试主要通过两种方式进行:一是采集收发端信号眼图并将其与接收器的波罩(EYE_MASK)进行比较;二是测试串行传输的误码率(BERT:bit error ratio test)。

接收器的EYE_MASK形象地反映了接收器的灵敏度和动态范围,只有处于接收区域内的信号才能被接收器正确识别,否则采样判决后得到的将是误码。 Virtex-5中GTP单元的最小EYE_MASK为(112ps,150mV),其中112ps表示最小眼宽(EYE_WIDTH),150mV给出最小眼高(EYE_HEIGHT)。图5给出了在靠近FPGA发送管脚和接收管脚处测得的串行传输收发两端的信号。在该测试信道环境下,正常发送信号到达接收端时已经被大幅衰减和畸变,眼宽仅为96ps,眼高仅为70.5mV,均不满足GTP的要求(112ps,150mV)。如果不考虑芯片内部的均衡器,该接收信号将不能被正确识别。相反,如果在发送端增加预/去加重,则能有效地对抗信道的不理想性,在一定程度上降低接收处信号的抖动,使眼图睁开达到 (211ps,191mV)。这一实测结果与之前的仿真和理论分析一致。

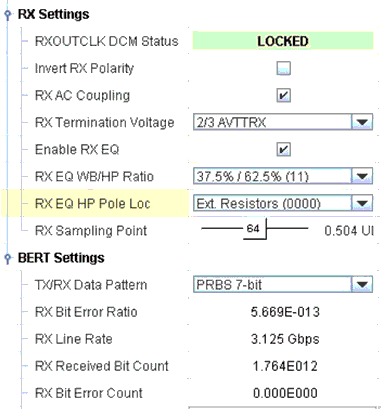

赛灵思提供了一个专门用于误码率测试的工具IBERT,如图6所示,其基本原理是在发送端发送一个伪随机序列(如PRBS7),接收端接收到序列后再与同一伪随机序列进行校对并记录校对结果。利用这个工具可以动态调整GTP的参数设置并测出相应的传输误码率。

图6 误码率测试

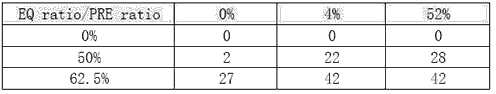

通过IBERT工具可以得到本系统在不同预/去加重和均衡参数设置下的无误码(BER《1e-12)采样区间,如表1所示。

表 1 无误码采样区间(单位:1/128 UI)

责任编辑:gt

-

FPGA

+关注

关注

1602文章

21320浏览量

593173 -

芯片

+关注

关注

447文章

47788浏览量

409106 -

收发器

+关注

关注

10文章

2968浏览量

104774

发布评论请先 登录

相关推荐

基于FPGA的高速数据采集系统接口设计

请问FPGA的输出管脚到差分芯片的输出之间是否需要添加一级驱动器?

AD19:如何设置 差分线对与单端线之间的线间距?

差分线传输线长度差有关的问题

怎么实现基于FPGA的具有流量控制机制的高速串行数据传输系统设计?

基于FPGA单芯片实现ARM系统设计解决方案

基于FPGA的高速串行传输接口研究与实现

基于Virtex-5的3.125G串行传输系统的设计

基于FPGA芯片实现单对差分线串行传输系统的设计

基于FPGA芯片实现单对差分线串行传输系统的设计

评论