2020年12月,合肥晶合集成电路股份有限公司(以下简称“晶合集成”)与矽成积体电路股份有限公司(以下简称“ISSI”)、成都锐成芯微科技股份有限公司(以下简称“锐成芯微”)联合推出110nm-AL MCU 全平台解决方案(图1)。该平台为晶合集成“显像微电”(显示器驱动、图像传感、微控制器、电源管理)四大特色工艺中重要的“微”一环。

嵌入式闪存(110LP-eFlash):基于110nm LP 1.5V/5V 低功耗逻辑工艺的嵌入式闪存平台。面向容量介于16KB/32KB-256KB,擦写次数大于100K次的MCU应用。采用ISSI第二代架构 2T-pFlash (pFusion®) 的记忆体模块,搭配锐成芯微的全套低功耗模拟IP方案:

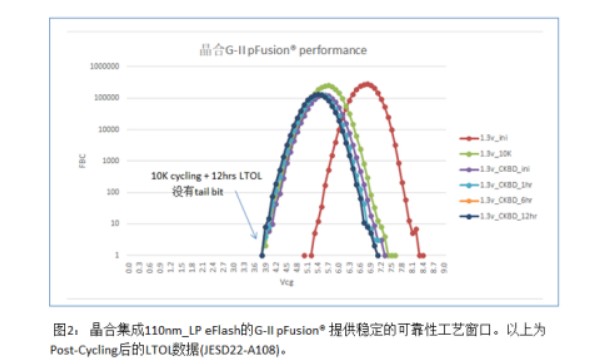

1)NVM IP:ISSI pFusion® 第二代架构。在第一代架构低功耗、高速度、高抗干扰能力及高可靠性的基础上,显著提升可靠性的工艺窗口(图2),特别适用于高可靠性需求的工规及车规应用;客制化的pFusion®模块允许同时存在不同大小的擦除区块,提升系统配置弹性,满足客戶多种应用场景需求。

2)模拟IP:锐成芯微的全套低功耗模拟IP方案具有卓越的静态功耗(nA级),极大降低了芯片在待机模式下的整体功耗。在功耗、性能和成本上实现极佳平衡,可以广泛应用於MCU、IoT, smart card,wireless、power meters以及车规系统。2020年晶合集成成功导入多家嵌入式闪存客户产品验证并于12月进入投片量产。

MTP(110LP-MTP):基于110nm LP 1.5V/5V 低功耗逻辑工艺的MTP(Multiple-Time Programming)平台。面向容量1KB-16KB/32KB,擦写次数介于10次-10K次的MCU应用。锐成芯微的LogicFlash® IP 提供业界最小的MTP IP。具有擦写次数大于10K次, 高温数据保存大于10年,高速读写及低芯片测试成本等优势,满足低成本高性能MCU的应用需求,可广泛应用于工业和家电类产品,例如锂电池供电的物联网、智能家居、智能穿戴类应用。目前已经成功导入客户并进入投片量产。

晶合集成的110nm全铝后段12寸生产线可为客户在MCU及低功耗SOC产品提供更具市场竞争力的代工业务和更优质的技术服务。为了更好满足客户产品日益增长的更新迭代需求,到2022年,晶合集成还将在55nm逻辑工艺基础上推出55nm嵌入式闪存工艺平台,进一步为客户提供128KB-1MB高性能MCU平台解决方案。

关于合肥晶合集成电路股份有限公司

合肥晶合集成电路股份有限公司(简称“晶合集成”)成立于2015年5月,专注于半导体晶圆生产代工服务。截至2020年11月产能突破3万片/月,实现了在手机面板驱动芯片代工领域领先的目标。晶合集成初期的主要产品为面板驱动芯片,后续将以客户需求为导向,结合平板显示、汽车电子、家用电器、工业控制、人工智能、物联网等产业发展趋势,进一步拓展微控制器(MCU)、CMOS图像传感器(CIS)、电源管理(PMIC) 、人工智能物联网(AIoT)等不同应用领域芯片代工,矢志成为中国最卓越的集成电路专业制造公司之一。

关于矽成积体电路股份有限公司

矽成积体电路股份有限公司(简称“ISSI”)成立于1988年,是一家技术领先的集成电路设计企业。公司专注于汽车电子、网络通信、工控医疗及数字消费电子四个领域,为此设计开发高性能IC芯片,主要产品包括DRAM、SRAM、FLASH及混合模拟信号产品。除此之外,矽成也拥有独立自主研发的embedded flash(pFusion)智财权(IP),透过技术授权于各大芯片代工厂及设计公司,量产工艺从180nm到55nm,累计的出货片数远大于一百万片晶圆;以第三方的e-flash IP 来说,目前是属于世界领先的供应商之一。

关于成都锐成芯微科技股份有限公司

锐成芯微成立于2011年,是一家专注于集成电路IP核技术研发及服务的国家高新技术企业,总部位于成都,在国内多地设有分支机构。锐成芯微是国内领先的同时拥有超低功耗模拟IP技术、高可靠性嵌入式存储IP技术、高性能RF技术和高速数据传输IP技术的企业,目前已与国内外20多家晶圆代工厂开展合作,产品覆盖从14/16nm到180nm的CMOS, BiCMOS, BCD, SiGe, HV,FinFET,FD-SOI等几十个工艺制程,累计开发IP 500多项,国内外申请专利超200件,服务全球300多家集成电路设计企业,产品广 泛应用于物联网、智能家居、汽车电子、智慧电源、可穿戴、医疗电子、工业控制等领域。

责任编辑:tzh

-

微控制器

+关注

关注

48文章

8249浏览量

162266 -

集成电路

+关注

关注

5446文章

12463浏览量

372606 -

mcu

+关注

关注

147文章

18604浏览量

386555 -

嵌入式

+关注

关注

5186文章

20143浏览量

328644

发布评论请先 登录

【「AI芯片:科技探索与AGI愿景」阅读体验】+工艺创新将继续维持着摩尔神话

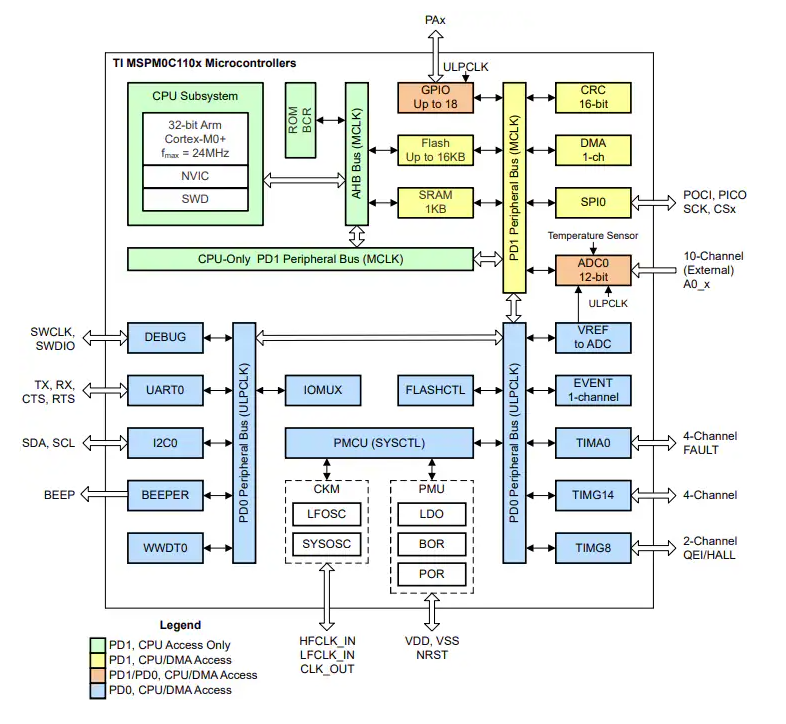

Texas Instruments MSPM0C110x/MSPM0C110x-Q1/MSPS003混合信号MCU数据手册

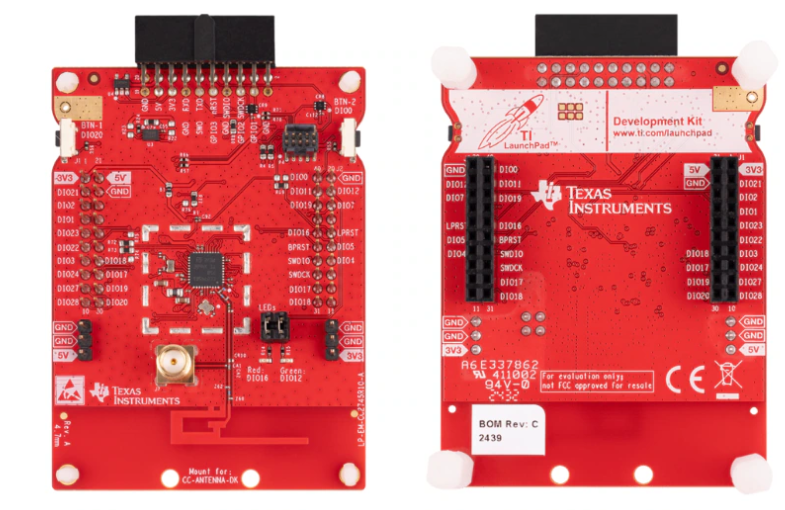

Texas Instruments LP-EM-CC2745R10-Q1 LaunchPad™开发套件特性/应用/布局

晶振测试,有那些难点?又如何去解决

突破14nm工艺壁垒:天准科技发布TB2000晶圆缺陷检测装备

千亿美元打水漂,传三星取消1.4nm晶圆代工工艺

千亿美元打水漂,传三星取消1.4nm晶圆代工工艺

深入探索:晶圆级封装Bump工艺的关键点

思特威与晶合集成签署深化战略合作协议,携手推进国产CIS发展

晶合集成2024年净利润预计大幅增长

晶合集成全资子公司皖芯集成大手笔 晶圆大厂引资95.5亿

晶圆背面涂敷工艺对晶圆的影响

晶合集成发布110nm-LP MCU工艺平台

晶合集成发布110nm-LP MCU工艺平台

评论