如果您阅读了许多PCB设计指南,尤其是有关并行协议和差分对布线的指南,则将看到很多关于走线长度匹配的内容。当您需要进行迹线长度匹配时,您的目标是最大程度地减少串行协议中的差分对,并行协议中的多个对(例如PCIe),并行协议中的多个迹线/对或使用以下协议的任何协议之间的时序差异源同步时钟。CAD工具使您可以轻松地考虑一次发生的情况。但是,在其他频率下会发生什么。更具体地说,宽带信号会发生什么?

所有数字信号都是宽带信号,其频率内容从DC扩展到无穷大。由于数字信号的带宽很大,迹线长度匹配应使用哪个频率?不幸的是,用于迹线长度匹配的频率是模棱两可的,因此设计人员需要了解如何应对PCB迹线长度匹配与频率的关系。为了更好地理解这一点,我们需要研究宽带设计中使用的技术,以及如何在走线长度匹配中考虑整个信号带宽。

差分对的PCB走线长度匹配与频率的关系

正确进行迹线长度与频率的匹配需要考虑到迹线上传播信号的整个带宽。在过去的几年中,这一直是差分串行协议的研究主题,诸如USB 4之类的标准对宽带信号完整性指标提出了特定要求。一些示例宽带信号完整性指标是:

集成差分串扰

积分差分插入损耗

积分差分回波损耗

积分差分阻抗偏差

所谓“集成”,是指信号完整性的特定方面适用于整个相关频率范围。换句话说,如果以差分串扰为例,我们希望将两个差分对之间的差分串扰最小化到某个极限以下,这在信令标准中已指定。我们马上将看到为什么这对于跟踪长度匹配很重要。

分散

在时域中,我们只关心差分对的两端在同一时刻跨过HI和LOW状态(假设为二进制)之间的中途过渡。显然,抖动在这里造成了一个问题,即它会将您的走线长度限制在一定的最小容限范围内,因此,您永远不会在同一时刻使一对线的两端完美过渡。在频域中,我们需要考虑以下来源的色散:

几何色散:这是由于互连的边界条件和几何形状而引起的,然后,边界和几何形状决定了互连的阻抗随几何形状的变化。

介电扩散: 这发生在PCB基板中,并且与PCB上互连的几何形状无关。它包括Dk的色散和损耗。

粗糙度色散:由于铜粗糙度模型的因果关系以及高频下的趋肤效应,会产生这种额外的色散来源。

纤维编织的色散:PCB层压板中的纤维编织在整个互连中产生周期性的色散变化。

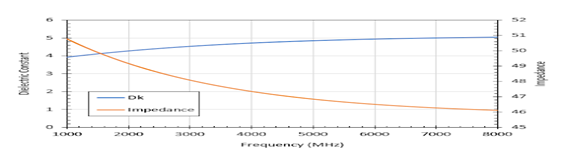

因为这些色散源始终存在于走线中,所以它们会导致实际PCB走线的阻抗,速度和所有其他信号完整性指标是频率的函数。下面显示了一个示例,该示例显示了Dk实部中的色散如何影响微带走线的阻抗。

信号速度

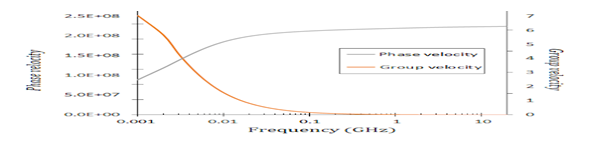

如果您熟悉传输线理论,那么您就会知道阻抗和信号速度密切相关。让我们以PCB走线的信号速度为例。下图显示了具有粗糙度和色散的模拟带状线的组速度和相速度。

带铜粗糙度和介电色散的示例带状线上信号的群速度和相速度。

在这里我们可以看到,相速度在很宽的频率范围内变化很大,从1 MHz到20 GHz达到2倍的变化。相速度的变化在这里是重要的参数,因为这是不同频率分量沿互连线传播的速率。通过这种变化,我们可以看到对于实际互连而言,PCB迹线长度匹配与频率之间的匹配变得多么困难。我们需要某种方式来考虑所有频率,而不仅仅是任意选择的单个频率。

宽带长度匹配与频率

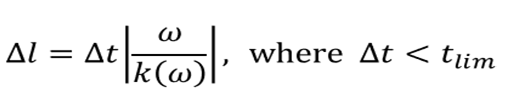

为了制定长度匹配的度量,我们需要考虑给定信令标准的最小允许长度偏差。我们将此最小时间偏差称为tlim。我们可以写出以下有关长度公差和允许的时序失配的方程:

根据允许的时序变化的长度变化。

在此,函数k只是互连上信号的传播常数,这也是由于色散引起的频率的函数。我们可以采用统计方法使用称为“ Lp范数”的方法来处理允许的长度不匹配。无需太过深入地研究所涉及的数学,只需知道该度量等效于计算函数和某个平均值(它们之间仅相差一个常数)之间的RMS差异即可。因此,这使其成为解决某些目标设计值和信号完整性度量(阻抗,脉冲响应衰减/延迟,串扰强度等)之间变化的理想数学工具。

使用Lp范数,我们可以根据时序不匹配限制tlim定义的一些上限来重写允许的长度不匹配:

根据允许的时序变化的长度变化。

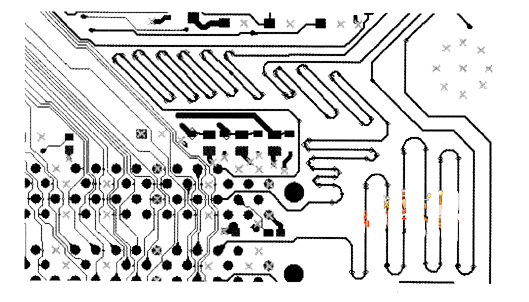

当使用宽带信号完整性指标进行PCB设计时,可以将上述方程式视为一个约束条件:在确定传输线的尺寸时,这可能会影响差分对的两端之间或中的任意两条走线之间的总允许长度偏差。高速并行协议。只要您知道传输线的传播常数,积分就很容易计算。然后,可以使用场求解器来计算此值,具有标准传输线几何形状的分析模型来手动计算。

只是为了给计算提供一些数字,如果我使用上面显示的模拟带状线的相速度,我们会发现,如果允许的最大最大值,则平行的两条单端完全隔离的迹线之间的最大允许长度不匹配为2.07 mm时序不匹配为10 ps。请注意,对于10 ps,这是许多高速数字信号的边沿速率的很大一部分。对于我上面模拟的带状线,这等于1.3041毫米的允许长度不匹配。

总而言之,我们已经证明,使用Lp范数可以将PCB迹线长度匹配与频率的关系降低为单个度量。如果您是PCB设计人员,则无需手动执行此计算,而只需要使用正确的PCB布线工具集即可。

编辑:hfy

-

pcb

+关注

关注

4225文章

22484浏览量

386024 -

宽带信号

+关注

关注

1文章

17浏览量

11208

发布评论请先 登录

相关推荐

PCB板上的差分传输线长度匹配问题

高速信号的走线长度如何控制?

如何在PADS9.2里生成走线长度报表?

我的PCB走线经验归纳

计算PCB线宽线长过孔铜厚电流的软件

如何实现Altium PCB设计中的内部走线长度?

高速PCB设计调整走线长度

pcb如何在走线长度匹配中考虑整个信号带宽

pcb如何在走线长度匹配中考虑整个信号带宽

评论