尽管 Vivado 不支持 “placement cost tale”的功能,InTime 却有一个相似功能叫做“Placement Exploration”配方(Receipe),并且不会对性能产生任何影响。在本文中,我们将通过展示几则用户案例的结果,来了解这个布局配方的作用以及它能对您有哪些帮助。

1. 什么是“Placement Exploration”配方?

Placement Exploration 这种策略可以将非关键的寄存器位置随机化。这样可以让 Vivado 探索更多的可能性,使用不同的布局布线计算来产生不同的结果,同时不会影响设计的功能。

2. 运行原理

这个配方需要设计有一些非关键的单元(单元已经达到时序路径),目标器件要有一些未使用的 slice。设计中未使用的 slice 越多,就有更多的运行组合可以创造出来,从而提升随机性,取得更好的结果。

如果这些需要没有满足,用户在运行配方的时候会看到下面的报错。

这种情况下,您需要重新检验设计,看看是不是没有假路径(false path,适用于 InTime 2.2.1以前的版本)或者是不是器件可用的 slice 数量较少。如果是因为没有假路径,您可以查看是否可以为设计设置假路径。

3. 真实案例

我们继续前面案例。下面的代码可以让您使用FEP Tcl API 来在云端编译:

项目一

· Device 器件: xcvu190

· TNS (ns) : -5841.436

· WNS (ns): -0.725

· WHS (ns): 0.016

· CLB Utilization 利用率 (%): 80.15

· Run Time 运行时间: 04:46

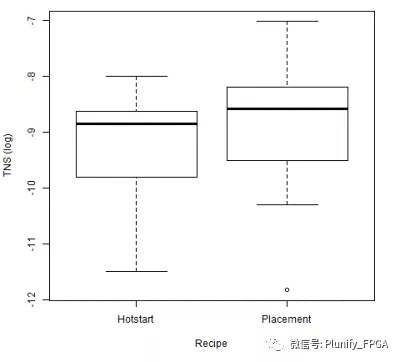

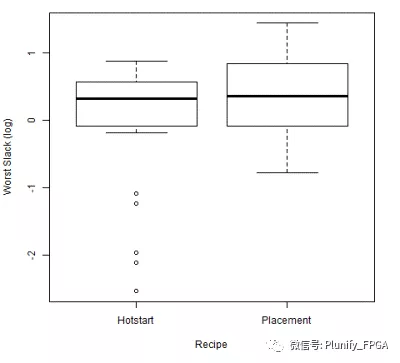

本设计优化了两轮。每轮有20-30次编译以及结果。对于 placement exploration,我们从前一轮的结果中选取最好的WNS 结果,在这个案例中,是-0.417ns。然后将它设置成“父版本”来进行探索。在下表(log)中,您可以看到结果中“种子”的作用,WNS 有着非常广泛的分布值。最好 WNS结果的平均值是-0.694ns,产生了高达0.457ns的巨大变化。如果您对比最好 WNS 结果和上一轮的 Placement Exploration,WNS 显著提升了43%。

图一: TNS 盒状图

图二: WNS盒状图

项目二

· Device器件: xcvu190-flgb2104

· TNS (ns) : -10229.035

· WNS (ns): -1.203

· WHS (ns): 0.016

· CLB Utilization 使用率(%): 75.71

· Run Time 运行时间: 04:33

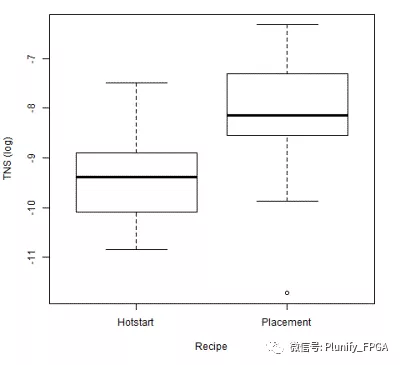

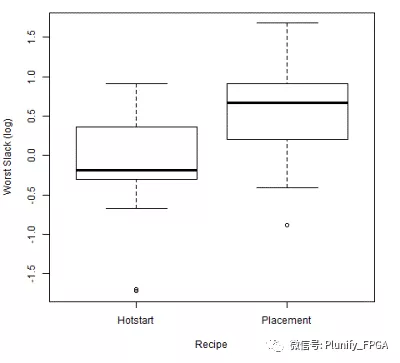

与项目一相似,项目二也有两轮优化。在第一轮中,目标是取得最好的WNS。我们使用上一轮最好的 WNS 结果(-0.404),运行一轮 placement exploration。基于 placement exploration 的结果, 平均值是-0.512ns。最好结果是-0.187,对于原父版本的结果来说,325ps是一个高达53%的巨幅提升。

图三: 项目二 TNS

图四: 项目二 WNS

4. 技术总结

结果的提升不言自明。如果您在为最终的300ps提升而奋战,请考虑使用这个方法,它能帮您在截止日期之前达到要求。

最后一点需要说明的是,运行附加的编译需要很多计算能力和运行时间。而最好的解决方案是云计算,您可以使用您自己的云服务,或者注册一个 Plunify Cloud 账户。

编辑:hfy

-

寄存器

+关注

关注

30文章

5027浏览量

117711 -

Vivado

+关注

关注

18文章

789浏览量

65092

发布评论请先 登录

相关推荐

深入探索Vivado非工程模式FPGA设计流程

介绍一种OpenAtom OpenHarmony轻量系统适配方案

Vivado Design Suite用户指南:设计分析与收敛技巧

Vivado设计套件用户:使用Vivado IDE的指南

如何实现基于FPGA Vivado的74系列IP封装呢?

如何在Vivado中添加时序约束呢?

能否提供LPDDR4-3200 3G“Row 16bit”所有颗粒建议的最新搭配方案或列表?

在Vivado中实现ECO功能

Vivado使用进阶:读懂用好Timing Report

Vivado的“Placement Exploration”配方案例分析

Vivado的“Placement Exploration”配方案例分析

评论