上篇介绍了如何利用verilog实现4线SPI配置时序,本篇将以AD9249介绍其3线SPI配置的verilog实现。

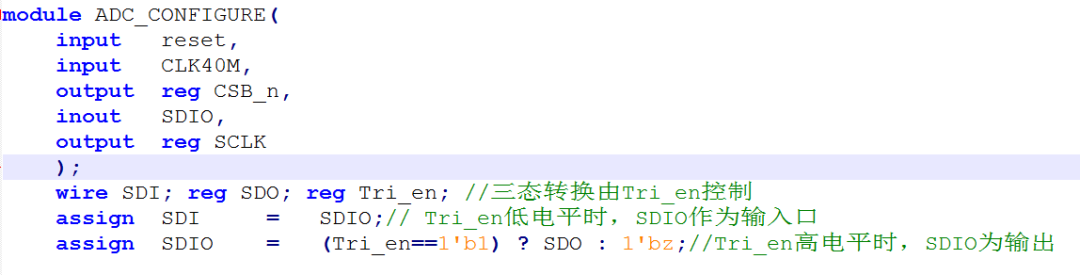

3线SPI的时钟产生方式和上一篇的4线SPI相同,这里不在叙述。两者的不同点在于:三线SPI模式需要FPGA管脚三态控制SDIO的输入/输出状态。下图所示的代码即为三态控制逻辑。SDI、SDO成为了内部逻辑信号,和上篇的4线SPI配置相同操作即可,而SDIO为三态管脚,需定义为inout类型。

Tri_en信号即为三态控制信号,在写操作中,该信号必须置高;然而在读操作中,该信号在写地址的前半段需置高,当完成写地址操作后,ADC的SDIO接口由输入变输出,此时FPGA控制Tri_en信号拉低,将FPGA端的SDIO管脚由输出变为输入,从而正常接收ADC的SDIO口输出的寄存器数值。

Tri_en到底应该在哪个具体时刻拉低,以便完成FPGA的SDIO三态转换呢?答案其实在第三篇已经说的很清楚了~~~~

另外,3线SPI读/写操作有专门的读写标志位,大家务必要留心~~

3线SPI的FPGA实现就介绍到这里了,其实和4线基本一样,只不过多了个三态转换而已,大家把上篇的4线SPI的实现过程想清楚了,再加上一个三态转换控制,3线SPI也就拿下了!

-

FPGA

+关注

关注

1655文章

22287浏览量

630308 -

Verilog

+关注

关注

30文章

1370浏览量

114140 -

SPI

+关注

关注

17文章

1866浏览量

99817

原文标题:FPGA通过SPI对ADC配置简介(五)--Verilog实现3线SPI配置

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

SPI的缺点介绍

蜂鸟E203在黑金XC7A200T型FPGA上点亮LED并实现流水灯

Hbirdv2在vivado2018.3上的仿真工作

关于系统链接脚本的介绍

HbirdV2-SoC自带pwm配置介绍

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

MAX9249多媒体串行链路串行器,带有LVDS系统接口技术手册

(精选笔记)ESP32 C3添加SPI以太网口芯片DM9051ANX通讯开发指导以及ESP IDF V5.4介绍 [手把手教程,图多消化好]

iic协议与spi协议的区别

江苏润石12位低功耗数模转换芯片RS1320介绍

以AD9249介绍其3线SPI配置的verilog实现

以AD9249介绍其3线SPI配置的verilog实现

评论