步骤1:您需要的内容

Nexys开发板FPGA

Xilinx ISE

某种扬声器

用于将板连接到扬声器的辅助电缆,或其他布线设置

步骤2:聚集项目项

收集项目的所有必需项(例如,电路板,Xilinx,扬声器和辅助电缆)。如果尚未购买nexys板,请先开始。这些可以直接通过Digilent或通过外部卖家(如Amazon)购买。之后,请访问www.xilinx.com下载Xilinx。最后,获取指定的扬声器系统和辅助电缆。然后,熟悉VHDL并熟练使用Xilinx。这将确保以下步骤不会造成混乱。

步骤3:在Xilinx中创建项目

打开Xilinx,然后单击新项目。屏幕打开后,

为项目命名,指定保存位置,并将顶级源类型设置为HDL。然后单击下一步。然后指定给定板的所有详细信息。这取决于您拥有的nexys板的版本。我们使用了nexys 2,因为它是最便宜的。 nexys-2开发板的详细信息如下:

评估开发板:无规格

产品类别:全部(或通用)

家族: Spartan 3E

设备:Nexys-2:XC3S500E

速度:-4

顶级源类型:HDL

综合工具:XST(VHDL/Verilog)

首选语言:VHDL

然后单击下一步。下一页将显示指定输入和输出的屏幕。这将设置第一部分以简化工作。首先给信号起一个名称,并对其进行相应的输入或输出。信号如下:

a:输入

b:输入

c:输入

d:输入

e:in

f:in

g:in

clk:in

音频输出:out

然后单击下一步。在下一个屏幕上,确保所有详细信息正确无误,然后单击“完成”。这将打开新项目。

步骤4:VHDL背景

此步骤将使您对所有这些内容有一些了解。 VHDL的不同部分实际上可以做到。为了创建作曲家,我们将需要指定实体,项目架构和两个单独的流程块。实体是输入和输出的基础,体系结构将指定每个信号和那里的值,而流程块将处理实际功能。

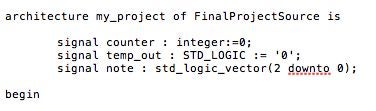

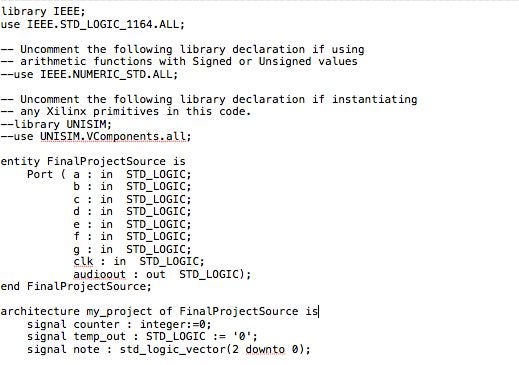

源文件顶部的实体声明给出每个输入和输出的规范。在作曲家的情况下,它们是a,b,c等,然后是STD_LOGIC或STD_LOGIC_VECTOR。字母代表值的名称,STD_LOGIC给出类型。 STD_LOGIC允许像变量一样一次为该值分配一个值。 STD_LOGIC_VECTOR允许以总线形式分配多个值。总线只是一组捆绑在一起的信号。但是,对于作曲家而言,仅使用了STD_LOGIC信号。

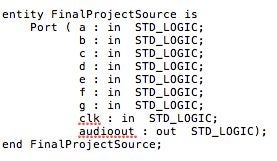

仅在实体声明下方指定了体系结构。这给出了源文件的“架构”。该体系结构包含前面所述的过程块以及将用于将信号值从一个过程传输到另一个过程的所有临时信号。结束架构后,文件也将结束。

然后可以创建流程块,以实际使作曲家工作。可以在源文件中找到过程块的示例。这些段包含带有信号的灵敏度列表。其背后的想法是,当灵敏度列表中的信号之一发生更改时,将运行整个过程块。在作曲家的情况下,这使我们可以在切换按钮时更新发送到扬声器的信号。

以上内容为VHDL提供了一些背景知识。但是,强烈建议您先阅读一些教程,然后再继续。以上所有示例均位于源文件中。

步骤5:让我们开始

在至此,您已经准备好开始作曲家的实际构建。作曲者将需要一个实体,体系结构和两个流程块。步骤2中的设置将为您填写实体声明。它看起来应该像第一张图片。

现在,有趣的部分开始了。首先,指定要在架构中各流程块之间使用的信号。以下是将要使用的信号。计数器将帮助进行分频,temp_out给我们一个信号,告知我们可以保留一个临时值,并且音符用于分配要播放的音符。这应该看起来像第二张图片。

在开始之后,我们将放置我们的流程块。上面给出了信号和架构。

步骤6:设计

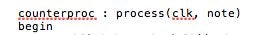

下一步我们需要开始作曲家的实际设计。第一个处理块将用作分频器。过程声明的示例如图3所示。

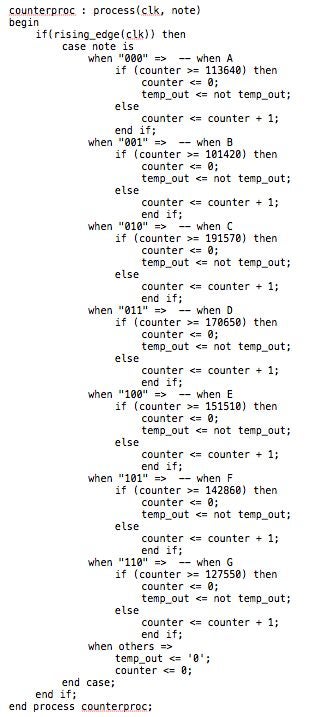

我们现在将使用时钟的50MHz信号。想法是递增计数器直到达到阈值,然后在每次达到该值时切换temp_out。这将使我们较低的较慢的频率代表音符的频率。例如,音符A为440Hz。通过从50MHz除以440Hz,我们可以从时钟获得该频率。然后我们取这个值,当计数器达到这个值时,我们切换temp_out,否则我们就简单地增加计数器。

将频率分为每个给定的音符后,我们必须检查音符的对应开关是否被按下。这是通过检查note的值来完成的。如果音符为“ 000”,则按下音符A的开关。如果音符为“ 010”,则按音符C,依此类推。

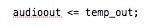

最后,我们需要确保音符只能在时钟的上升沿播放。这是通过将其包含在检查上升沿的if语句中来完成的。它应该看起来像图片4。

第7步:频分

现在实现了分频器。由于我们已经列出了所有规范,因此剩下的只是复制和粘贴并涵盖所有可能的条件。图5中提供了设置了所有音符的整个分频器。

请注意,当音符为“ 111”时,我们只需将计数器复位并输出为0。这是因为该板仅演奏七个注释,我们不希望任何不受支持的开关的非法值。现在,我们现在需要存储temp_out的值以用于扬声器。如图6所示,这是通过将temp_out分配给音频输出来完成的。

这将允许我们保存从上一过程中获得的频率并实际使用它。

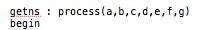

步骤8:流程语句

现在,我们继续设计和实现第二个流程块。第二个处理块将处理获取下一个状态。为了简化,我们使用状态来表示每个音符。此状态机将允许我们在切换开关时将其状态设置为所需的每个音符。例如,当按下第一个开关时,便会选择音符A并将其设置为下一个状态,这会将值分配给信号(来自体系结构声明的音符)。这将使我们能够在要弹奏音符的第一个处理块中进行检查。图7显示了带有灵敏度列表的第二个过程块的示例声明。

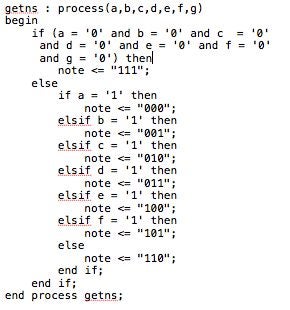

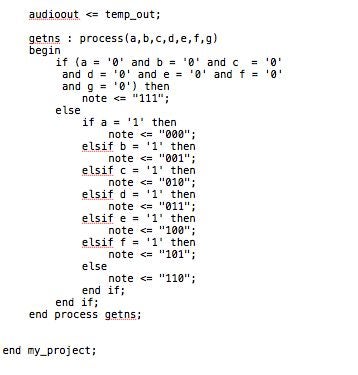

接下来,我们指定所有可能的条件,分别按下每个开关。我们首先需要检查是否没有按下任何开关。如果没有一个开关,则将音符设置为“ 111”,否则当按下一个开关时,我们将更改其对应的字母值。例如,当按下第一个开关时,信号a将获得该值。然后在getns内,我们给分频器分配要检查的值。该流程块使用多个if和elsif来说明不同的可能性。完成的过程框在图8中。

注意我们如何检查是否没有先按任何音符。这将确保我们仅获取有效的note值。除此之外,第二个else内部的if和elsif可以确保在没有切换任何受支持的开关时,我们不会意外地为note分配一个除“ 111”以外的值。

步骤9:将所有内容放在一起

至此,我们基本完成了。我们需要做的就是组装所有VHDL并对其进行合成。合成时应该没有错误。此后,预期的源在图9、10和11中。

现在,作曲家已经完成。下一步是测试使用刺激以确保其确实起作用。由于这对于作曲家的工作并不重要,因此我们在这里不解释测试。我们的测试代码随该项目的源代码一起提供。

步骤10:设置端口映射

快到了!现在,我们需要做的就是分配端口值,以便使作曲家能够在nexys板上工作。单击“提前计划”即可完成。打开此应用程序后,将出现一个界面,上面有一个怪异的面板。从那里,我们看到底部的框,其中包含实体值的端口映射。从这里开始,我们为每个实体在板上分配一个与其正确的开关相对应的端口。之后,我们需要为扬声器的电线分配端口。完成此操作后,保存并退出。现在我们可以再次进行合成,然后单击生成编程文件。此后,您需要将启动选项切换为JTAG Clock。通过单击顶部的“进程”,然后单击“属性”来完成此操作。在出现的窗口中,在启动选项下选择JTAG Clock(它最初是CCLK)。现在,退出该窗口并再次生成编程文件。

步骤11:对开发板进行编程

现在,打开Digilent的Adept并连接您的开发板,确保板子打开。熟练的人员应自动识别该设备。现在,在浏览窗口中选择位文件。一旦选择,点击程序。现在,该板已被编程。下一步是连接扬声器。这是通过将导线连接到在“预先计划”中选择的每个端口来完成的。然后您就完成了!

步骤12:玩得开心!

与作曲家见面,让演讲者演奏不同的音符。玩得开心!

-

FPGA

+关注

关注

1602文章

21317浏览量

593134

发布评论请先 登录

相关推荐

如何使用 Kivy 编写一款乒乓球游戏

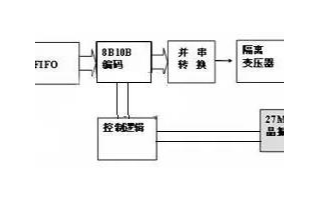

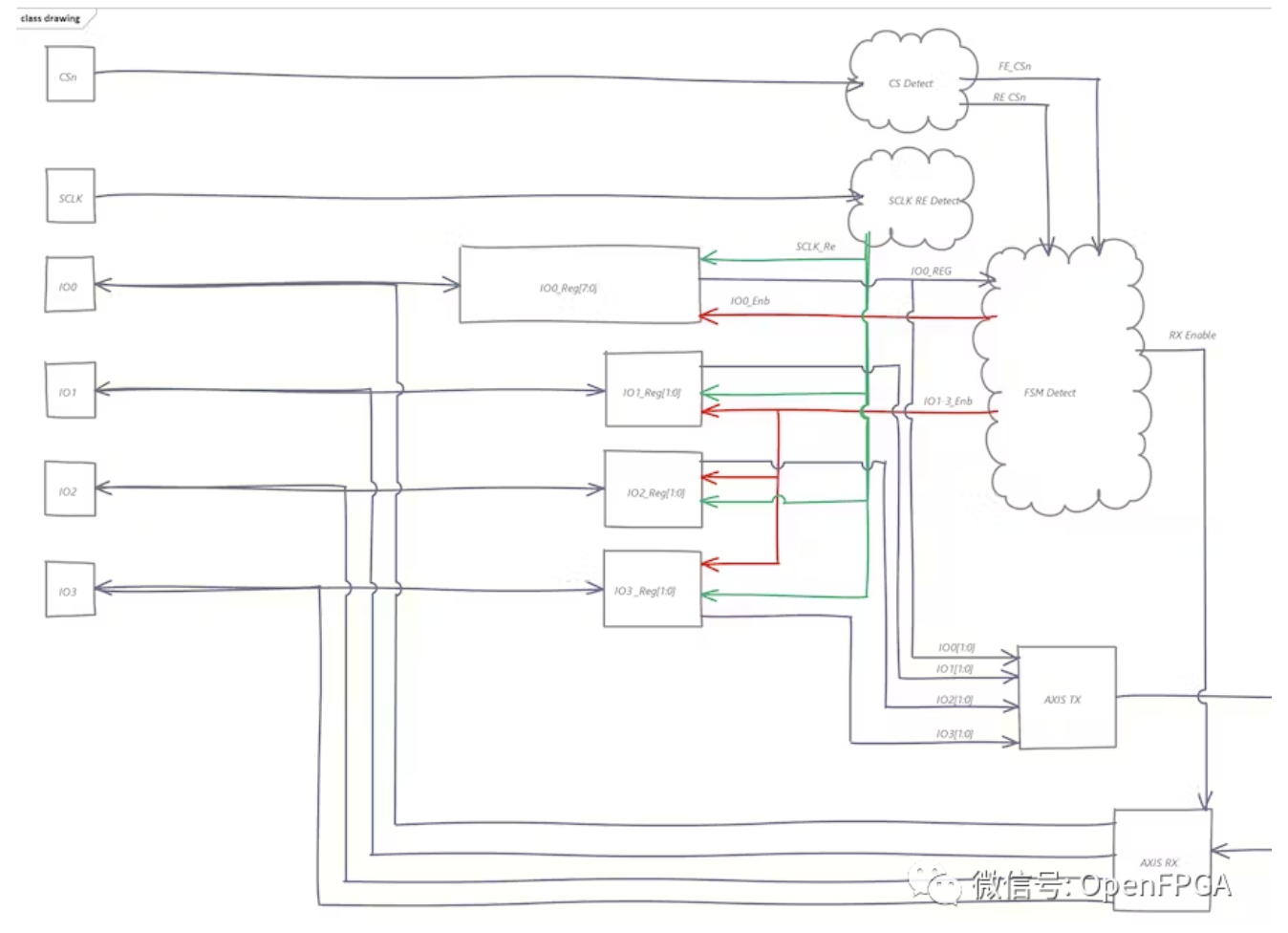

基于VHDL语言用FPGA制作SPI-ASI接口转换器

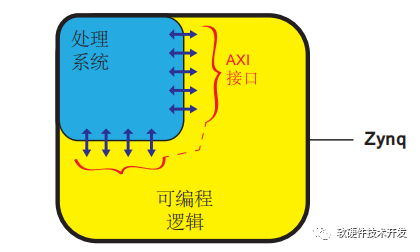

ZYNQ7000系列FPGA资源对比

FPGA的Verilog代码编写规范

labview编写FPGA上位机

Verilog Testbench怎么写 Verilog Testbench文件的编写要点

FPGA编写器的制作

FPGA编写器的制作

评论